碳化硅基MOSFETs器件研究进展

2016-09-13李金平

李金平, 王 琨

(1.国家国防科技工业局 协作配套中心, 北京 100081; 2.中国科学院半导体研究所 半导体材料科学重点实验室, 北京 100083)

碳化硅基MOSFETs器件研究进展

李金平1, 王琨2

(1.国家国防科技工业局 协作配套中心, 北京 100081;2.中国科学院半导体研究所 半导体材料科学重点实验室, 北京 100083)

基于近20年的研发,宽禁带半导体材料碳化硅(SiC)的金属-氧化物-半导体场效应晶体管(MOSFETs)的制备工艺逐步成熟,性能不断提高,已有SiC MOSFETs产品进入市场,故综述双注入MOSFETs(DMOSFETs)和沟槽MOSFETs(UMOSFETs)两种结构的SiC MOSFETs的研究进展和发展趋势,并介绍SiC MOSFETs器件制备的关键工艺和目前推出SiC MOSFET产品的公司及其产品性能。

碳化硅;功率器件;金属-氧化物-半导体场效应晶体管;阻断电压;通态电阻

第三代宽禁带半导体材料碳化硅(SiC)具有禁带宽度大、热导率高、击穿电场高、稳定性好等突出优势,非常适于研制新一代高压、大电流、高效率电力电子器件,其在电动汽车、高速铁路、舰船驱动、光伏和风力发电等领域具有极其重要的应用前景,是目前的国际研究热点。基于SiC材料可以研制多种类型的整流器件和电力开关器件,例如肖特基二极管(SBD)、金属-氧化物-半导体场效应晶体管(MOSFET)、结势垒控制肖特基二极管(JBS)、绝缘栅双极晶体管(IGBT)等。

与同为第三代宽禁带半导体材料的氮化镓(GaN)等材料相比,SiC可以通过热氧化得到氧化物材料二氧化硅(SiO2),从而使得基于SiC材料的MOSFETs器件和电路的研制成为可能。与其他类型的SiC电力电子器件相比,SiC MOSFETs具有高开关速度、高反向阻断电压等优势,而且驱动电路简单,与现有的电力电子器件(硅基功率MOSFETs和IGBTs)兼容性好,是备受瞩目的新型电力开关器件,具有极为突出的潜力和优势。

1 SiC MOSFET的分类及研究进展

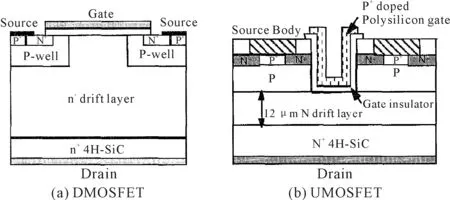

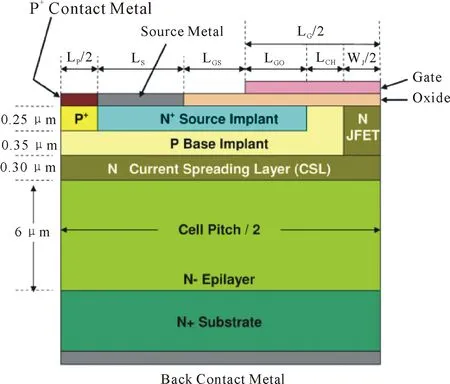

SiC MOSFETs的分类有多种方法,目前较为常用的是按照器件结构来进行分类,可分为横向和纵向两种结构。横向MOSFET的源极和漏极都制作在晶圆的同一面,而纵向结构器件的漏极制作在晶圆的背面(源漏两电极分别在晶圆的上下两面)。横向MOSFET,由于其两个电极制作在晶圆的同一面,较易实现功率集成电路,而且可通过提高器件的横向尺寸来提高器件的电压和电流,对外延材料的厚度要求较低,工艺也相对简单,因此在SiC功率器件的研究初期,其地位比较显著,但横向MOSFET器件的导通电阻较高,而且阻断电压也很难做高,所以其发展受到了限制。随着外延材料生长技术和SiC器件制备工艺的提高,导通电阻较低、能够工作在大电压和大电流条件下的纵向MOSFETs逐渐备受青睐。纵向MOSFET是通过纵向沟道的导通和关断实现功率转换,器件的阻断电压和导通电阻由外延材料的厚度和掺杂浓度进行调节,可以满足高压大电流的需求,是目前大功率SiC MOSFETs的研究热点。而根据垂直导电结构的差异,纵向MOSFET又可分为DMOSTETs(Double-implanted MOSFETs)和UMOSFETs(Trench MOSFETs)两种,如图1所示。

图1 纵向MOSFET结构

1993年,世界上第一款SiC功率MOSFET器件由美国Cree公司提出[1],是属于沟槽栅的UMOSFET[2],据报道该器件的耐压为150 V,特征导通电阻为33 mΩ·cm2。该结构的优点在于基区和源区不是使用离子注入和高温退火,而是通过外延形成,这样使得器件的沟道免于退化。但是,该结构却有以下两点不足:一是在制作槽栅时使用的干法刻蚀工艺会使得侧壁表面较为粗糙,使该结构的沟道迁移率较低;二是在该结构中,一部分栅氧化层位于漂移区中,由于在MOS界面中氧化物中的电场强度约是半导体的2.5倍,因此氧化层中的电场强度最高将达到6 MV/cm,很容易导致栅氧化层发生提前击穿。然而,基于双注入工艺的DMOSFET结构[2]则可克服上述缺点。

1.1SiC DMOSFET

DMOSFET又名双注入(Double-implanted)MOSFET,顾名思义,器件的研制过程需要经过两次离子注入。第一次是为形成P阱(P-well)区的P型离子注入,第二次是为制作源极欧姆接触的N+型离子注入。注入完成后,两个P-well区之间为JFET沟道,在器件工作的反向阻断模式下,可以有效保护栅氧化层。当栅压为正时,P-well区表面部分反型形成MOSFET导电沟道,电流从器件的漏极经过衬底、漂移区、JFET沟道、MOS沟道到达源极。 DMOSFETs由于引入JFET沟道保护栅氧化层,使得器件的击穿主要发生在半导体内,因此可以提高器件的阻断电压,这是此结构器件的最大优势之一。在DMOSFETs的研究中,美国普渡大学和Cree公司是最早开展相关研究并取得突出进展的代表性研究机构。

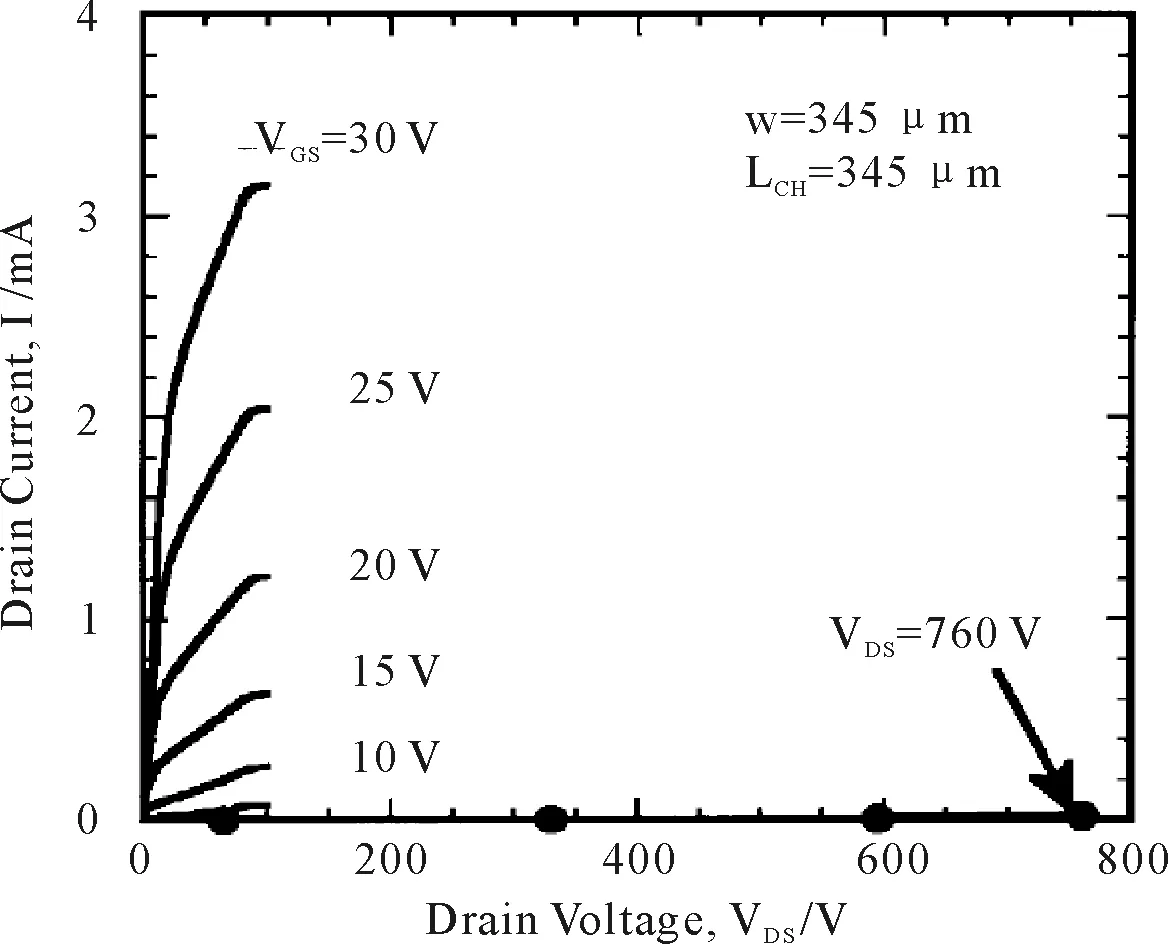

1997年,美国普渡大学的 Shenoy等人[3]采用N型6H-SiC作为衬底,首次实现了双注入MOSFETs。器件的漂移区为N型6H-SiC,掺杂浓度为6.5×1 015 cm-3,第一次注入硼形成P阱,第二次注入氮形成N+欧姆接触区。最终获得的器件,如图2所示,沟道长度10 μm时阻断电压为760 V,沟道长度5 μm时通态电阻为66 mΩ·cm2。该结构的优点是栅氧化层位于表面,远离漂移区,加之P-well的屏蔽作用,导致该器件的氧化层不易发生提前击穿,所以耐压很高。为了进一步降低DMOSFET的通态电阻,普渡大学的研究人员引入自对准注入工艺,两次注入之间不用图形转移,通过自对准定义沟道尺寸,减小沟道长度。2004年研制出的沟道长度为0.5 μm的SiC DMOSFETs[4],阻断电压900~1 000 V,特征通态电阻最低可到9.95 mΩ·cm2。

(a) 电压

(b) 电阻

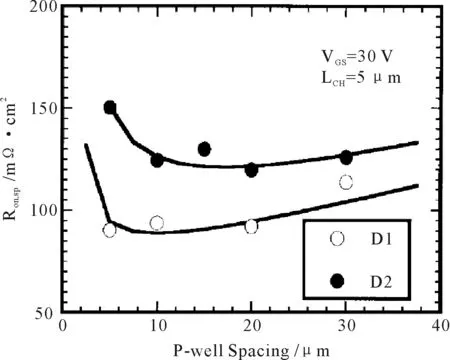

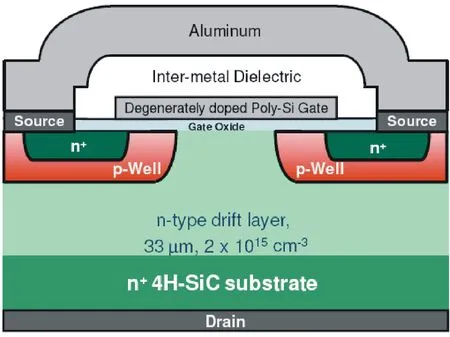

美国Cree公司继普渡大学之后开展了SiC DMOSFETs研究。Ryu等人2002年报道的大尺寸(3.3 mm×3.3 mm)SiC DMOSFETs[5],基于4H-SiC衬底,MOS沟道长度1.5 μm,电子迁移率最高可到22 cm2/Vs,N-漂移区的厚度为20 μm,掺杂浓度为2.5×1015cm-3。最终研制的器件,特征通态电阻在室温和200 ℃时分别为42 mΩ·cm2和85 mΩ·cm2,阻断电压为2 400 V,电流可到10 A。2003年,他们将N-漂移区的厚度增为115 μm,掺杂浓度降为6×1014cm-3,研制出阻断电压为10 kV的4H-SiC DMOSFETs[6],但器件的特征通态电阻较高,为236 mΩ·cm2。后来,他们对漂移区的厚度和掺杂浓度进行了优化,将所研制的10 kV DMOSFETs的特征通态电阻降至123 mΩ·cm2,此时器件的漂移区厚度为85 μm、掺杂浓度为8×1014cm-3,器件结构如图3所示[7-8]。该结构采用了50个终端保护环,单个器件总的终端长度达到了400 μm,该器件结构之所以可以达到10 kV的耐压,这些终端保护环的存在起到了重要的作用。2005年,继普渡大学的短MOS沟道器件之后,Cree公司的研究人员[9]也研制出MOS沟道长度为0.5 μm的DMOSFETs,阻断电压为2 000 V,特征通态电阻10.3 mΩ·cm2。

(a) 10 kV, 123 mΩ·cm2

(b) 30 A, 3 300 V

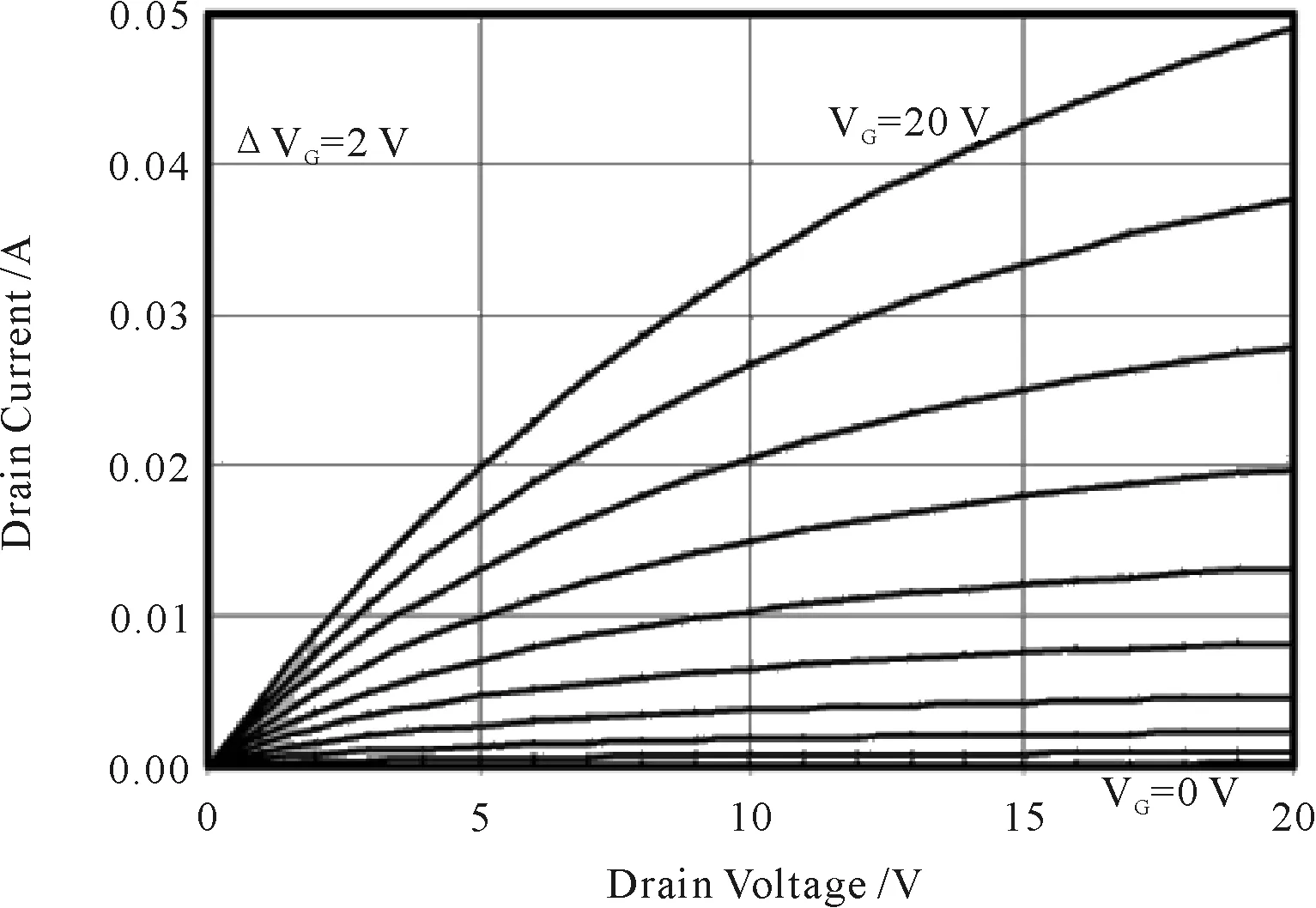

为了降低器件导通电阻,2007年,Saha和Cooper等人研制出一种击穿电压为l kV,导通电阻仅为6.95 mΩ·cm2的DMOSFET[10],如图4所示,其在原有的DMOSFET结构基础上进行了以下改进。

(1) 在P阱(P base)下方增加了一层电流分布层(current spreading layer, CSL),使得电流均匀向下流动,减少了电流的拥挤,降低导通电阻。

(2) 采用了宽度只有1 μm的重掺杂JFET区,在一定程度上也可以减少导通电阻。

(3) 采用自对准工艺把沟道长度制造成0.5 μm,从而在一定程度上减少了沟道对载流子的散射作用。在低压MOSFET中,沟道电阻是影响导通电阻的最主要的因素,在沟道中由于SiO2/SiC界面粗糙度对载流子的散射作用,使得载流子迁移率迅速降低,从而增大了器件的正向导通电阻。因此,对于低压器件而言,改善界面特性是提高载流子迁移率、降低导通电阻的重要途径。

(4) 该结构采用了在一氧化氮(NO)中进行退火,使得沟道电子迁移率比以往的器件高了5倍[10],界面特性有了显著的改善。

2011年Cree公司[11]研制的MOS沟道长度为0.5 μm的器件,阻断电压1 500 V,特征通态电阻降至3.7 mΩ·cm2。

(a) 结构

(b) 正向输出特性曲线

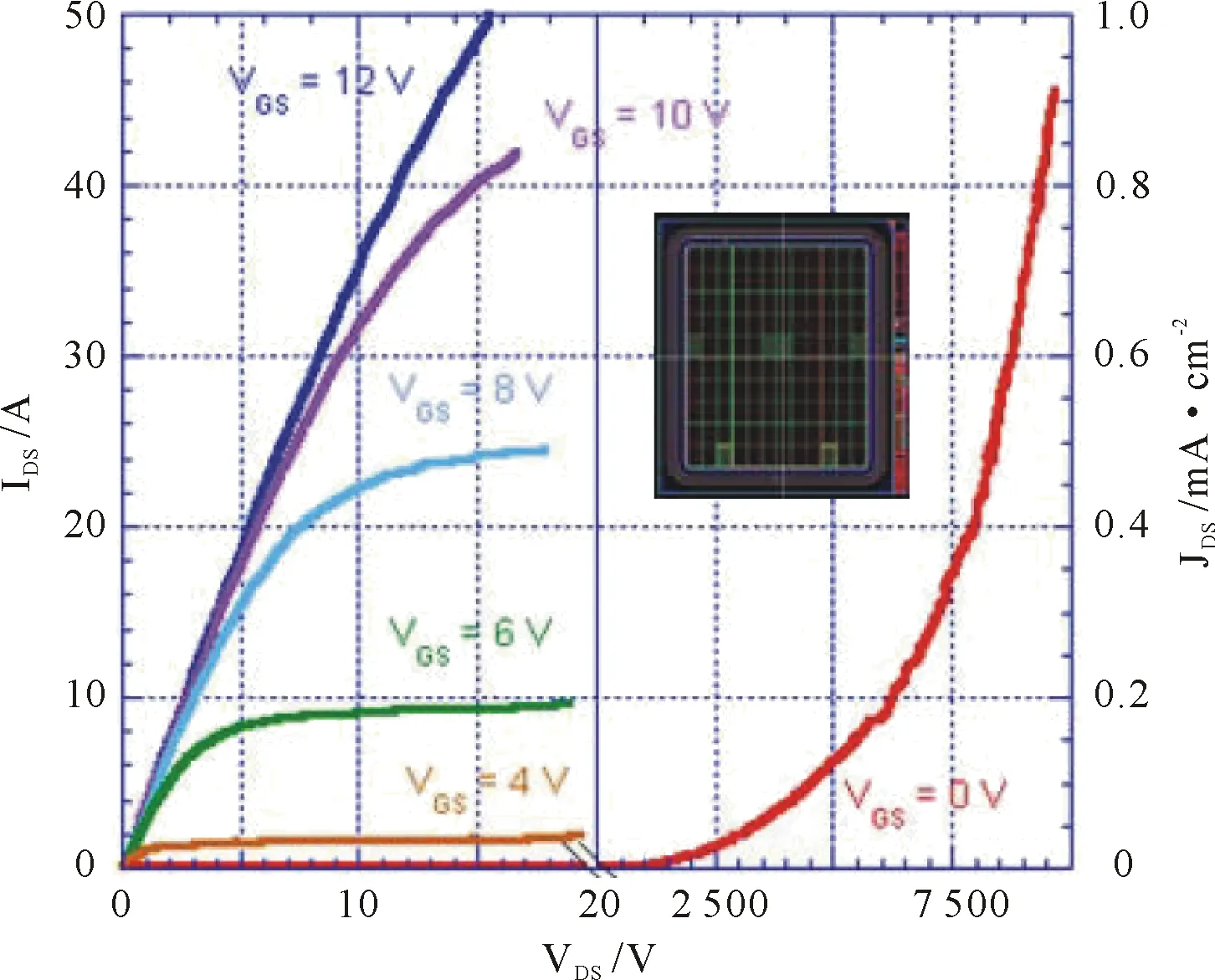

功率开关应用要求器件具有高的电流容量。2006年Cree公司报道了有源区面积为5.5 mm×5.5 mm的10 kV/5 A 的4H-SiC 功率DMOSFET,如图5所示[12]。N-漂移层厚100 μm,掺杂浓度为6.0 ×1014cm-3。该器件的MOS 沟道长度为0.5 μm,并且采用了基于边缘终端结构的浮动保护环技术(包含65个保护环),边缘终端结构总长550 μm。栅氧化层是采用1 175℃热氧化后经NO退火工艺形成,器件在关断电压为5.0 kV/6 A的瞬态特性测量条件下,开关时间为70 ns。因而,4H-SiC功率DMOSFET可用于高压、高频(20 kHz)开关领域应用。

图5 Cree公司于2006年报道的DMOSFET

2007年诺斯罗普格鲁曼电子系统公司报道了10 kV/50 A的4H-SiC功率DMOSFET(有源区面积增大至0.61 cm2)[13],器件结构示意如图6所示。N-漂移层厚100 μm,掺杂浓度为5.0×1014cm-3,在P阱层上再外延生长约100 nm厚的薄层。

(a) 结构

(b) 器件开态和关态特性

2009年Cree公司研制出20 A、1 200 V和30 A、3 300 V的4H-SiC DMOSFETs(图3)[8,14]。2013年,Cree公司研制出了1 600 V / 150 A 4H-SiC DMOSFET,该器件导通电阻12.4 mΩ,且能在200℃下稳定工作[15]。2015年,中国科学院微电子所研制出1 700 V/7 A 4H-SiC DMOSFET。器件的漂移区厚17 μm,掺杂浓度为5×1015cm-3,沟道长度为1 μm[16]。

SiC DMOSFETs与UMOSFETs相比,因为引入了JFET结保护栅氧区域,因此器件的击穿发生在半导体内部,阻断电压较高,而且制备工艺相对简单,是目前SiC MOSFETs产品采用的主要结构。这类器件在提高阻断电压、降低通态电阻方面的研究热点包括:(1)栅氧化层退火工艺优化[8],降低SiC/SiO2界面态密度和陷阱密度,提高MOS沟道迁移率;(2)采用自对准注入工艺,减小MOS沟道长度[4],降低器件通态电阻;(3)优化漂移区的厚度和掺杂浓度,综合优化器件阻断电压和通态电阻性能[7];(4)优化器件结构,例如终端引入浮动保护环(floating guard ring, FGR)结构[12,17],提高器件综合性能。

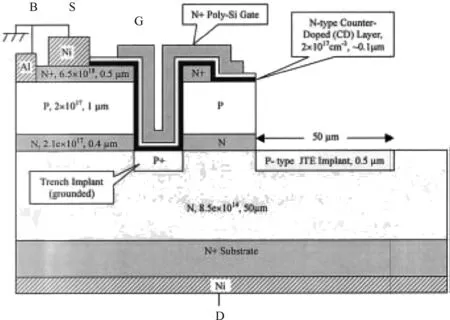

1.2SiC UMOSFETs

图1(a)给出了沟槽结构UMOSFETs的结构示意图,可以看出其与DMOSFETs最大的不同之处在于形成了沟槽结构的MOS沟道。UMOSFETs器件在研制时,首先通过刻蚀形成U型或V型的栅槽,接着进行氧化,在栅槽的底部和侧面形成SiO2氧化层,然后沉积电极。当器件的栅极电压大于开启电压时,器件导通,电流由N+衬底经过N-漂移区进入MOS沟道,最后到达源极。与DMOSFETs相比,UMOSFETs器件的基区和有源区可通过外延工艺形成,避免了离子注入和高温退火对器件沟道的影响。而且U型栅槽结构的MOS沟道也有助于降低器件的导通电阻和提高沟道密度,更易于实现大电流器件。另外,MOS沟道垂直于晶圆表面,可以提高晶圆的利用率。但是,由于UMOSFETs器件U型沟槽的形成必须通过干法刻蚀,工艺复杂,而且刻蚀台面的质量会大大影响载流子的迁移率;另一方面,垂直的MOS沟道使得沟道底部电场产生累积,很容易导致栅氧化层发生提前击穿。所以,提高沟道载流子迁移率、降低MOS氧化层电场是提高SiC UMOSFET性能的两个重要方向。

美国Cree公司的Palmour等人[1]1993年首次实现了基于6H-SiC的UMOSFETs,由于氧化层较薄(40~50 nm),器件的阻断电压很低(60V就被击穿)。2002年美国普渡大学的Li等人[18]提出了一种如图7(a)所示的沟道掺杂SiC UMOSFETs结构,首次同时引入MOS沟槽氧化物保护和结终端(JTE)保护两种方法提高器件的阻断电压,最终得到的器件,阻断电压达到3 360 V。虽然,引入沟道掺杂结构提高了器件的阻断电压,但是MOS沟道底部的P+注入层会对沟道侧壁造成损伤,进而影响载流子迁移率,导致器件的特征通态电阻较高(199 mΩ·cm2),而且这层掺杂薄层的制备工艺非常复杂,限制了其进一步的商业化应用。随后,同研究小组的Khan等人[19]改进了上述结构,如图7(b)所示,将MOS沟道底部的P+注入层进一步扩展到电流扩展层(N spreading layer)下方,进一步降低了栅氧化层电场,增大了MOS沟槽深度,提高了电流驱动能力。另外,他们首次在注入之后对器件在NO气氛中退火(post-oxidation annealing),降低氧化物内的缺陷密度,提高了载流子迁移率。所研制的SiC UMOSFETs,阻断电压提高到5 050 V,特征导通电阻为105 mΩ·cm2。

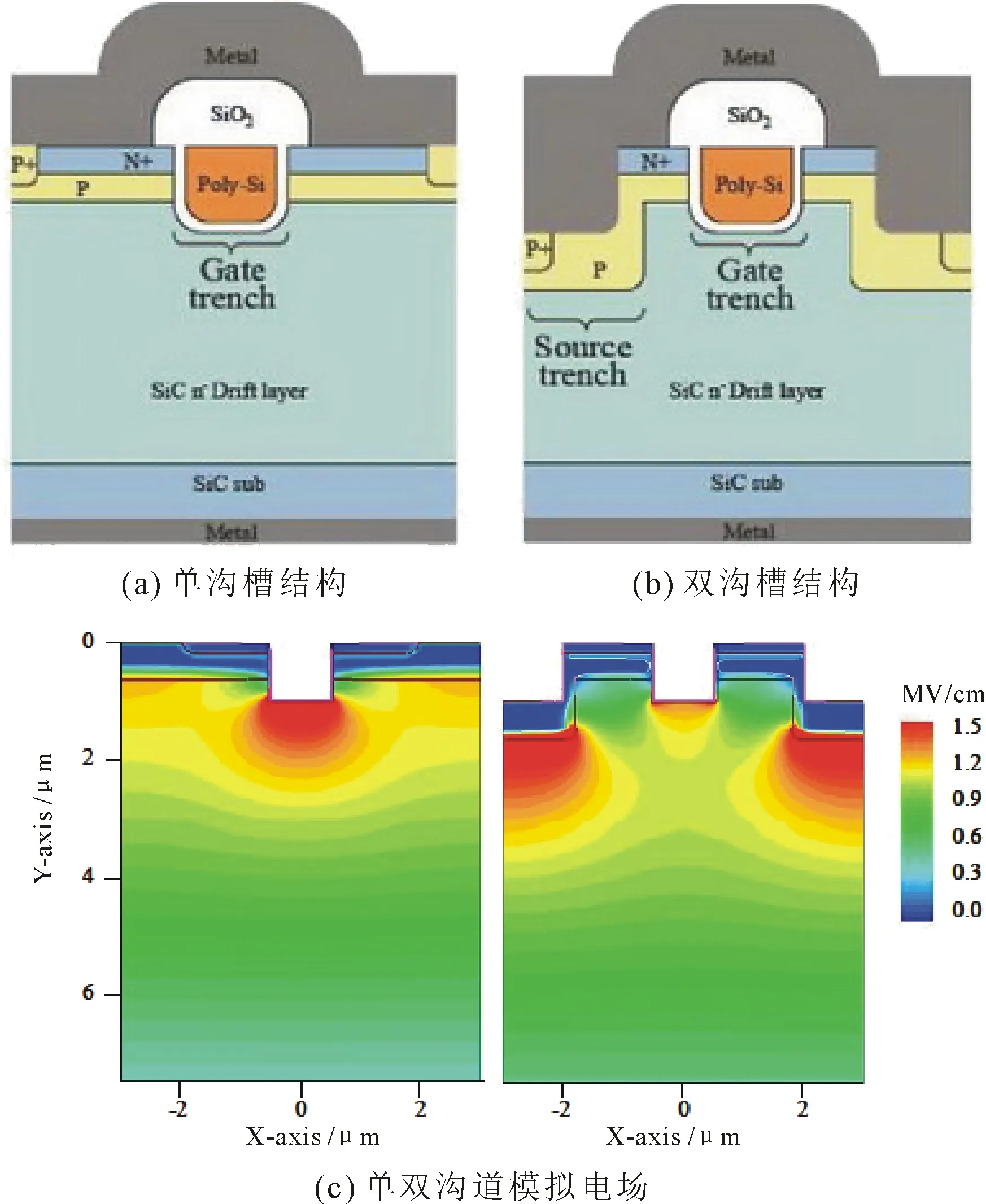

(a) 引入MOS沟槽氧化物保护和结终端

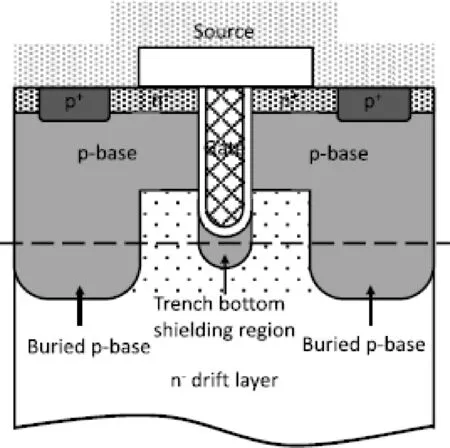

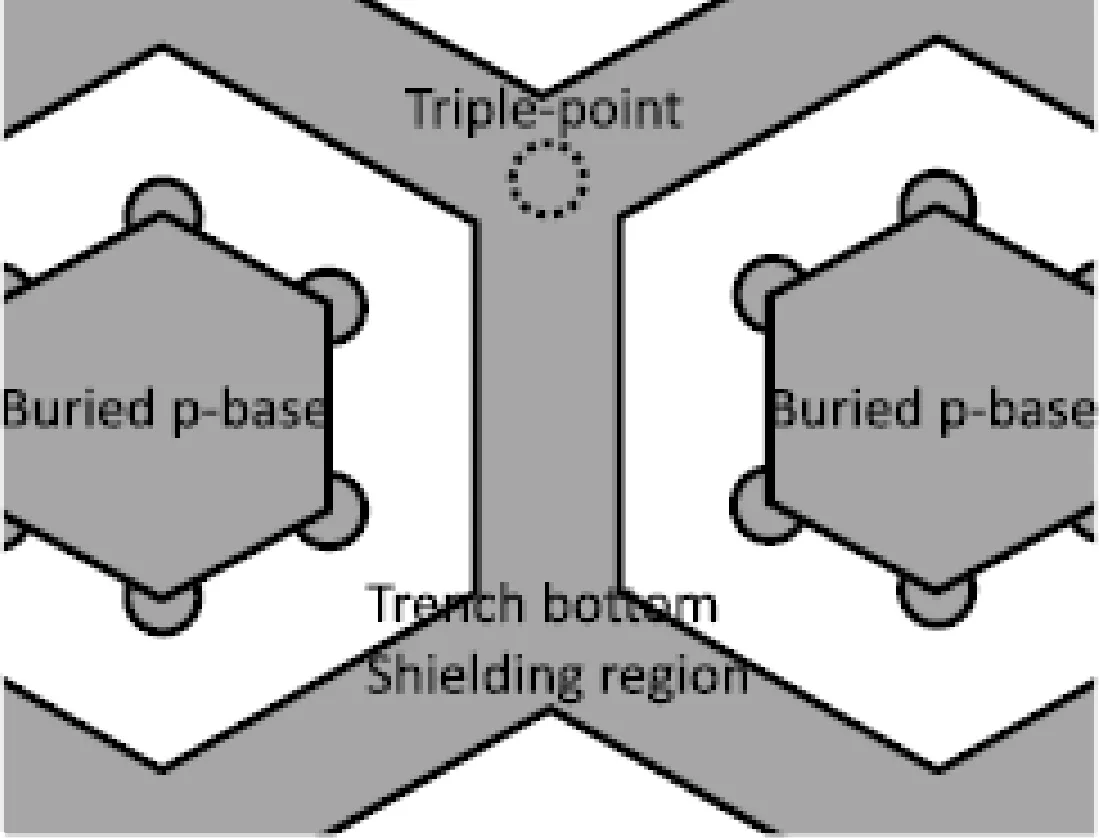

在降低栅氧层电场方面,2011年,日本Rohm公司在IEDM会议上推出了具有超低通态电阻的双沟槽MOSFETs[20],除了栅沟槽之外,在源极沟槽底部注入一个比栅沟槽更深的P区形成第二个沟槽,降低了栅沟槽底部的电场[4],如图8所示。基于此结构实现的600 V、1 200 V SiC MOSFETs,导通电阻均低于传统结构MOSFETs器件。2013年,日本丰田公司的Takaya等人[21]通过加厚MOS沟道底部的氧化层厚度降低电场,所研制的UMOSFETs阻断电压达到1 400 V,特征通态电阻为4.4 mΩ·cm2。2014,日本三菱的Kagawa等人[22]在MOS栅槽氧化层下引入P型保护层(Bottom P-Well),有效降低了氧化层内的电场,提高了器件的阻断电压。2016年,日本AIST的Harada等人[23]通过MeV离子注入引入六方埋层P型基区和沟槽底部保护降低栅氧层的电场,如图9所示,所实现的器件阻断电压3 800 V,特征通态电阻8.3 mΩ·cm2。

图8 Rohm公司推出的双沟槽MOSFETs

(a) 结构

(b) 六方埋层基区俯视

2 SiC MOSFETs的关键制备工艺

制备SiC MOSFETs器件,需要经过外延、掺杂、刻蚀、氧化和高温退火、金属接触等多步工艺,其中选择性掺杂、低缺陷刻蚀和高质量氧化层制备是最重要的三步工艺。

2.1掺杂

掺杂是SiC MOSFETs制备中极其重要的工艺。由于SiC材料中,Si-C键的结合能很高,导致杂质在SiC中的扩散温度极高(1 800℃以上)。因此,SiC器件制作过程中很少采用扩散的方式进行掺杂,而是通常采用外延和离子注入两种方法,其中离子注入是实现选择性掺杂的重要手段。目前,通过注入氮元素已经实现了性能较好的N型SiC材料,氮离子的注入损伤也可以通过退火工艺有效消除,而P型SiC的实现仍然是国际研究热点。

可用来形成P型SiC的掺杂元素有铝(Al)和硼(B)两种元素,两者各有优缺点。B原子小于Al原子,所以注入引起的晶格损伤较小,而且同注入剂量时注入深度也较大,但Al的电离能小于B,所以注入后要求的激活温度小于B。不管是Al还是B注入形成的P型SiC,都需要在较高温度(1 500~1 700℃)下进行退火,以实现杂质的激活,为了在高温退火过程中保护SiC的表面,一般会在退火前引入耐高温的AlN或C作为掩膜,防止SiC表面退化。P型SiC注入杂质的选择和激活、减小注入损伤、提高P型SiC材料迁移率,是SiC MOSFET研制中需要解决的重要问题。

2.2刻蚀

刻蚀是SiC MOSFETs研制中的重要工艺步骤。由于SiC的硬度高,化学稳定性强,所以刻蚀难度较大,目前采用较多的是干法刻蚀,其中感应耦合等离子刻蚀(ICP)和反应离子刻蚀(RIE)是最主要的刻蚀方法。ICP刻蚀采用SF6和O2混合气体,而反应离子刻蚀通常采用氟化气体和氧气的混合气体。如何形成高质量刻蚀台面、降低刻蚀损伤和控制刻蚀深度是目前SiC MOSFETs器件刻蚀工艺中需要解决的问题。

2.3氧化

前面的介绍中已经提到,能够通过热氧化形成氧化物材料SiO2是SiC在研制MOSFETs方面比其他宽禁带半导体材料更具优势的重要原因之一,但是栅氧化层的质量问题同时也是目前影响SiC MOSFETs性能的重要问题。一方面,作为氧化物材料,SiO2的介电常数小于SiC,所以同样电压条件下SiO2内的电场更高,更容易发生击穿。另一方面,SiO2和SiC的界面,界面态密度很高,导致器件导通能力降低。而且,SiC研制过程中,高温退火也容易引起SiO2和SiC的界面粗糙度增加,使载流子迁移率降低。

界面态密度的高低是评价SiC MOSFETs氧化物质量的重要指标。Fiorenza等人[24]研究发现,氧化后的特殊气体退火可以使栅氧层的界面态密度大幅降低。很多研究者对栅氧后退火工艺进行了研究,NO、N2O和POCl3是经常采用的退火气氛[25-26]。

3 SiC MOSFETs的实用化情况

自1993年Palmour等人[1]首次报道了SiC MOSFETs之后,基于这种宽禁带半导体材料的MOSFETs已经发展了20年多。随着单晶衬底材料、外延材料生长技术的不断发展和器件制备工艺的不断进步,器件的阻断电压越来越高、电流越来越大、通态电阻不断降低,已经逐步走向市场。

日本Rohm公司 2010年在国际上最早推出了SiC MOSFETs产品。目前,其产品共有8种,阻断电压有400 V、650 V、1 200 V和1 700 V共4种。2016年最新推出的1 700V N沟功率MOSFETs(SCT2H12NZ), 通态电阻为1.15 Ω,电流3.7 A。

继Rohm之后,美国Cree公司在2011年推出第一代SiC MOSFETs CMF20120D系列产品,耐压最大为1 200 V,最大工作电流33 A,导通电阻80 mΩ。 2013年发布了第二代产品(C2M系列),耐压1 200 V、导通电阻为25 mΩ或80 mΩ,在整个工作温度范围内导通电阻的整体增量仅为20 %,更适用于高电压环境。目前Cree公司的MOSFETs产品有近20款,阻断电压在900~1 700 V之间。

英飞凌是欧洲致力于SiC功率器件研发的代表性公司。他们从1992年开始开展SiC功率器件研究,2016年推出了CoolSiC MOSFET系列产品,阻断电压均为1200 V,通态电阻在11 mΩ到45 mΩ之间。

另外,国际上还有意法半导体(ST)、三菱电机(Mitsubishi Electric)、住友(Sumitomo)等公司已经推出或即将推出SiC MOSFETs产品。

4 结语

随着SiC单晶和外延材料制备工艺以及器件制造工艺的不断进步,基于宽禁带半导体材料SiC的MOSFETs器件性能和可靠性也逐步提高,已经从实验室走向市场。提高SiO2/SiC界面质量、降低栅氧化层电场强度、优化注入和刻蚀等工艺将是进一步提升现有结构的SiC MOSFETs性能的研究热点方向。

[1]PALMOUR J W, EDMOND J A, CARTER J C H. Demonstrating the potential of 6H-Silicon Carbide for power devices[J/OL]. IEEE Transactions on Electron Devices, 1993, 40(11): 2129-2130[2016-05-08].http://dx.doi.org/10.1109/DRC.1993.1009604.

[2]CASADY J B, AGARWAL A K, ROWLAND L B, et al. Sillicon Carbide Power MOSFET Technology[C/OL]//1997 IEEE International Symposium on Compound Semiconductors, CA San Diego: IEEE, 1998: 359-362[2016-05-08].http://dx.doi.org/10.1109/ISCS.1998.711654.

[3]SHENOY J N, COOPER J A, MELLOCH M R, High-Voltage Double-Implanted Power MOSFET’s in 6H-SiC[J/OL]. IEEE Electron Device Letters, 1997, 18(3): 93-95[2016-05-08].http://dx.doi.org/10.1109/55.556091.

[4]MATIN M, SAHA A, COOPER J A. A self-aligned process for high-voltage, short-channel vertical DMOSFETs in 4H-SiC[J/OL]. IEEE Transactions on Electron Devices, 2004, 51(10): 1721-1725[2016-05-08].http://dx.doi.org/10.1109/TED.2004.835622.

[5]RYU S H, AGARWAL A, RICHMOND J, et al. 10 A 2.4 kV Power DiMOSFETs in 4H-SiC[J/OL]. IEEE Electron Device Letters, 2002, 23(6): 321-323[2016-05-08].http://dx.doi.org/10.1109/LED.2002.1004222.

[6]RYU S H, AGARWAL A K, KRISHNASWAMI S, et al. Development of 10 kV 4H-SiC power DMOSFETs[J/OL]. Materials Science Forum, 2004, 457-460:1385-1388[2016-05-08].http://dx.doi.org/10.4028/www.scientific.net/MSF.457-460.1385.

[7]RYU S H, KRISHNASWAMI S, LOUGHLIN M O, et al. 10 kV, 123 mΩ·cm24H-Sic Power DMOSFETs[J/OL]. IEEE Electron Device Letters, 2004, 25(8):556-558[2016-05-08].http://dx.doi.org/10.1109/LED.2004.832122.

[8]CHENG L, RYU S H, JONAS C, et al. 3300 V, 30 A 4H-SiC Power DMOSFETs[C/OL]// 2009 ISDRS, USA MD College Park: IEEE, 2009: 1-2[2016-05-08].http://dx.doi.org/10.1109/ISDRS.2009.5378284.

[9]RYU S H, KRISHNASWAMI S, DAS M, et al. 10.3 mΩ·cm2, 2 kV Power DMOSFETs in 4H-SiC[C/OL]// 2005 Proceedings of the 17th International Symposium on Power Semiconductor Devices & IC’s, CA Santa Barbara: IEEE, 2005: 275-278[2016-05-08].http://dx.doi.org/10.1109/ISPSD.2005.1488004.

[10] SAHA A, COOPER J A. A 1-kV 4H-SiC Power DMOSFET Optimized for Low On-Resistance[J/OL]. IEEE Transactions on Electron Devices, 2007, 54(10): 2786-2791[2016-05-08].http://dx.doi.org/10.1109/TED.2007.904577.

[11] RYU S H, CHENG L, DHAR S, et al. 3.7 mΩ·cm21500 V 4H-SiC DMOSFETs for Advanced High Power, High Frequency Applications[C/OL]// 2011 Proceedings of the 23rd International Symposium on Power Semiconductor Devices & IC’s, San Diego CA:IEEE, 2011: 227-230[2016-05-08].http://dx.doi.org/10.1109/ISPSD.2011.5890832.

[12] RYU S H, KRISHNASWAMI S, HULL B, et al. 10 kV, 5 A 4H-SiC power DMOSFET[C/OL]// 2006 Proceedings of the 18th International Symposium on Power Semiconductor Devices & IC’s, Italy Naples: IEEE, 2006: 1-4[2016-05-08].http://dx.doi.org/10.1109/ISPSD.2006.1666122.

[13] HOWELL R S, BUCHOFF S, CAMPEN S V, et al. Demonstration of 10 kV, 50 A 4H-SiC DMOSFET with stable subthreshold characteristics across 25~200 ℃ operating temperatures[C/OL]// 2007 ISDRS, USA MD College Park: IEEE, 2007: 1-2[2016-05-08].http://dx.doi.org/10.1109/ISDRS.2007.4422414.

[14] HULL B, CALLANAN R, DAS M, et al. 20 A, 1200 V 4H-SiC DMOSFETs for Energy Conversion Systems[C/OL]// 2009 IEEE Energy Conversion Congress and Exposition, NC Durham: IEEE, 2009: 112-119[2016-05-08].http://dx.doi.org/10.1109/ECCE.2009.5316036.

[15] CHENG L, AGARWAL A K, SCHUPBACH M, et al. High Performance, Large-Area, 1600 V/150 A, 4H-SiC DMOSFET for Robust High-Power and High-Temperature Applications[C/OL]// 2013 Proceedings of The 25th International Symposium on Power Semiconductor Devices & ICs, Kanazawa: IEEE, 2013: 47-50[2016-05-08].http://dx.doi.org/10.1109/ISPSD.2013.6694395.

[16] SHEN H J , TANG Y C, PENG Z Y, et al. Fabrication and Characterization of 1700 V 4H-SiC Vertical Double-Implanted Metal-Oxide-Semiconductor Field-Effect Transistors[J/OL]. Chinese Physics Letters, 2015, 32(12): 109-112[2016-05-08].http://dx.doi.org/10.1088/0256-307X/32/12/127101.

[17] HUNG C C, YEN C T, LEE L S, et al. Characteristics Improvement of 4H-SiC using Termination with P-Well Enclosure in P-Plus Floating Guard Rings for 1700V DMOSFETs[C/OL]// 2014 Proceedings of the 26th International Symposium on Power Semiconductor Devices & IC’s, Hawaii Waikoloa: IEEE, 2014: 217-220[2016-05-08].http://dx.doi.org/10.1109/ISPSD.2014.6856015.

[18] LI Y, COOPER J A, CAPANO M A.High-voltage (3 kV) UMOSFETs in 4H-SiC[J/OL]. IEEE Transactions on Electron Devices, 2002, 49(6): 972-975[2016-05-08].http://dx.doi.org/10.1109/TED.2002.1003714.

[19] KHAN I A, COOPER J A, CAPANO M A, et al. High-voltage UMOSFETs in 4H SiC[C/OL]// 2002 Proceedings of the 14th International Symposium on Power Semiconductor Devices and ICs, IN West Lafayette: IEEE, 2002: 157-160[2016-05-08].http://dx.doi.org/10.1109/ISPSD.2002.1016195.

[20] NAKAMURA T, NAKANO Y, AKETA M, et al. High performance SiC trench devices with ultra-low Ron[C/OL]// 2011 IEEE International Electron Devices Meeting (IEDM), Washington DC: IEEE, 2011: 26.5.1-26.5.3[2016-05-08].http://dx.doi.org/10.1109/IEDM.2011.6131619.

[21] TAKAYA H, MORIMOTO J, HAMADA K, et al. A 4H-SiC trench MOSFET with thick bottom oxide for improving characteristics[C/OL]// 2013 Proceedings of The 25th International Symposium on Power Semiconductor Devices & ICs, Kanazawa: IEEE, 2013: 43-46[2016-05-08].http://dx.doi.org/10.1109/ISPSD.2013.6694394.

[22] KAGAWA Y, FUJIWARA N, SUGAWARA K, et al. 4H-SiC Trench MOSFET with Bottom Oxide Protection[J/OL]. Materials Science forum, 2014, 778-780:919-922[2016-05-08].http://dx.doi.org/10.4028/www.scientific.net/MSF.778-780.919.

[23] HARADA S, KOBAYASHI Y, ARIYOSHI K, et al. 3.3 kV-class 4H-SiC Mev-implanted UMOSFET with reduced gate oxide field[J/OL]. IEEE Electron Device Letters, 2016, 37(3): 314-316[2016-05-08].http://dx.doi.org/10.1109/LED.2016.2520464.

[24] FIORENZA P, SWANSON L K, VIVONA M, et al. Characterization of SiO2/SiC interfaces annealed in N2O or POCl3[J/OL]. Materials Science Forum, 2014, 778-780:623-626[2016-05-08].http://dx.doi.org/10.4028/www.scientific.net/MSF.778-780.623.

[25] CHUNG G Y, TIN C C, WILLIAMS J R, et al. Improved inversion channel mobility for 4H-SiC MOSFETs following high temperature anneals in nitric oxide[J/OL]. IEEE Electron Device Letters, 2001, 22(4): 176-178[2016-05-08].http://dx.doi.org/10.1109/55.915604.

[26] OKAMOTO D, YANO H, HIRATA K, et al. Improved inversion channel mobility in 4H-SiC MOSFETs on Si face utilizing phosphorus-doped gate oxide[J/OL]. IEEE Electron Device Letters, 2010, 31(7): 710-712[2016-05-08].http://dx.doi.org/10.1109/LED.2010.2047239

[责任编辑:陈文学]

Progress in SiC based MOSFETs

LI Jinping1,WANG Kun2

(1. The Center of Coordination & Support, SASTIND, Beijing 100081, China; 2. Key Lab of Semiconductor Materials Science, Institute of Semiconductors, CAS, Beijing 100083, China)

The silicon carbide metal-oxide-semiconductor field-effect transistors (SiC MOSFETs) have been developing for twenty years,and their processing technologies and properties are improved gradually. Nowadays, some products of this kind have entered the market. The progress of SiC Double-implanted MOSFETs (DMOSTETs) and Trench MOSFETs (UMOSFETs) is reviewed. Meanwhile, the devices’ key processing techniques and the performance of SiC MOSFETs products are also introduced.

power device, MOSFET, breakdown voltage, on-resistance

10.13682/j.issn.2095-6533.2016.04.001

2016-06-01

国家自然科学基金重点项目(61334002)

李金平(1965-),女,高工,从事科研项目咨询评估及管理和信息材料及器件研究。E-mail: lijinpingccsc@126.com

王琨(1987-),女,博士,助理研究员,从事宽禁带半导体材料与器件研究。E-mail:wklq1987@163.com

TN386

A

2095-6533(2016)04-0001-08