射频微系统2.5D/3D封装技术发展与应用*

2016-09-07王从香胡永芳

崔 凯,王从香,胡永芳

(南京电子技术研究所, 江苏 南京 210039)

射频微系统2.5D/3D封装技术发展与应用*

崔 凯,王从香,胡永芳

(南京电子技术研究所, 江苏 南京 210039)

2.5D/3D封装技术是满足未来射频系统更高集成度、更高性能、更高工作频率需求的主要手段。文中介绍了目前微系统2.5D/3D封装技术的发展趋势及硅通孔(TSV)、微凸点/铜柱、圆片级封装等先进的高密度封装技术,并关注了2.5D/3D封装技术在射频微系统领域的应用及挑战,为射频微系统集成封装技术研究提供参考。

2.5D/3D封装;射频微系统;硅通孔;圆片级封装;热管理

引 言

未来电子系统将持续向更高集成度、更高性能、更高工作频率等方向发展,传统的集成封装技术逐渐难以满足要求。随着技术的进步,一些先进的2.5D/3D集成封装技术(TSV、WLP等)应运而生,成为“超越摩尔”最有前景的技术之一。采用TSV、WLP技术的2.5D/3D封装已经在微机电系统(MEMS)、影像传感器(CIS)以及存储器(FLASH、DRAM)等产品中实现工程化应用,并延伸至绘图芯片、多核处理器、电源供应器和功率放大器、FPGA等芯片产品领域。在射频微系统领域,先进2.5D/3D封装技术还未出现系统性工程化应用,但相关应用研究报道已经越来越多。文中介绍了目前微系统2.5D/3D封装技术的发展趋势及硅通孔(TSV)、微凸点/铜柱、圆片级封装等先进的高密度封装前沿技术,并重点关注了2.5D/3D封装技术在射频微系统领域的应用及挑战,为射频微系统集成封装技术研究提供参考。

1 微系统先进封装技术及其发展趋势

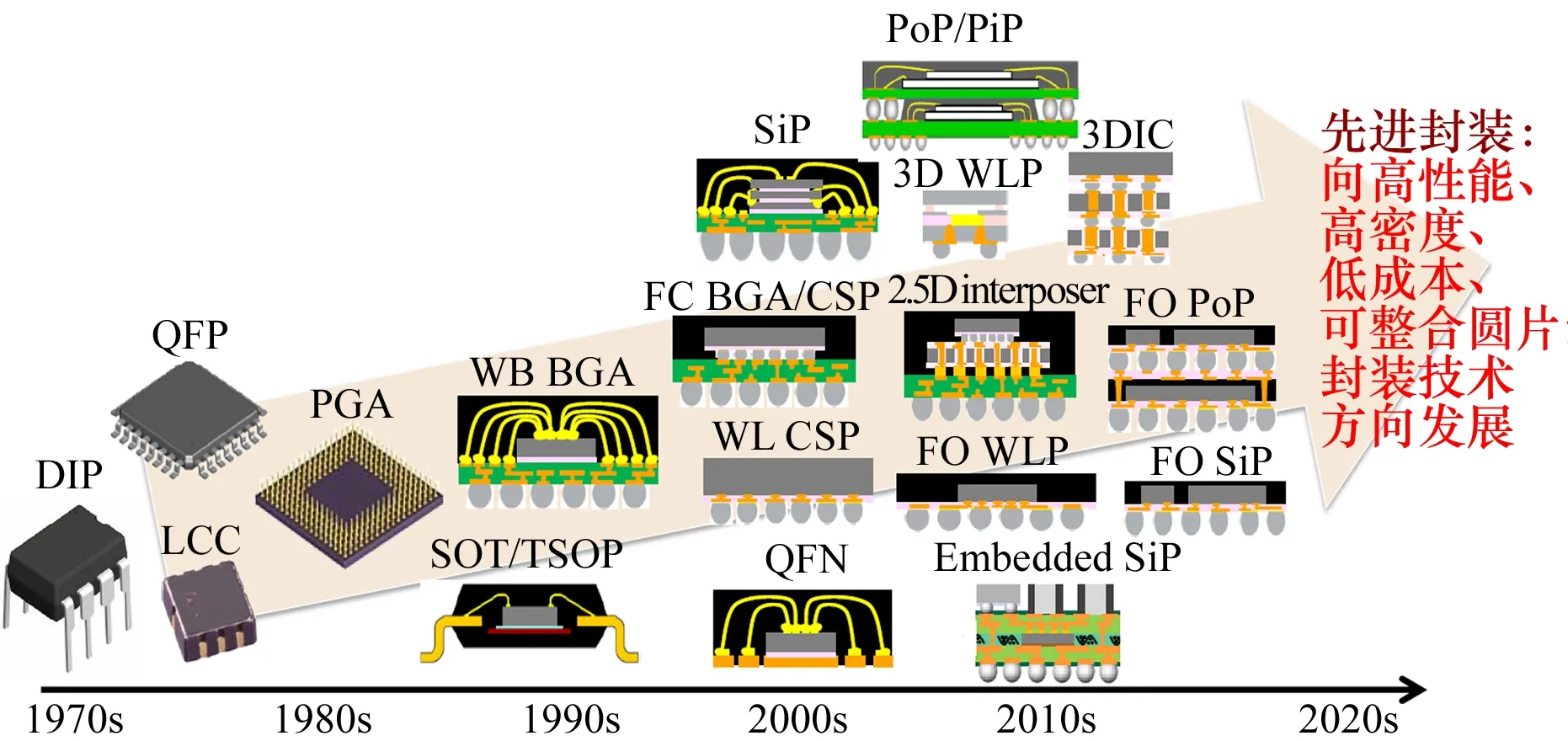

高性能、小型化是所有电子产品持续不断的要求,图1所示为Yole给出的电子封装结构发展趋势,互连密度越来越大,而封装尺寸越来越小。电子封装结构已经由最初的单一芯片封装发展到2D多芯片封装(2D-MCM),随着技术的进步,PoP、SiP、SoC等高密度2.5D/3D封装形态不断发展进步。TSV技术的出现使高密度层间垂直互连成为可能,真正意义上的高密度3D封装时代已经到来。

图1 电子封装结构发展趋势[1]

图2所示的电子封装结构发展路线图进一步说明电子封装结构随着技术进步而不断更新换代,并将继续向着高性能、高集成度、低成本的3D微系统方向发展。持续驱动3D封装技术发展的因素如下:

1)超越摩尔。集成电路特征尺寸已达到极限、成本不断攀升,采用新一代封装技术在提高系统性能的同时不断提高集成度;

2)提高性能。缩短信号传输路径、提高处理速度、提高带宽、降低RC延迟、降低功耗等;

3)异质集成。在一个封装体内,同时集成各种功能器件(RF器件、存储器、逻辑器件、MEMS等)、集成多种材料(Si、GaAs、GaN);

4)成本控制。采用圆片级封装技术可有效降低成本。

图2 电子封装结构发展路线图[2]

图2中DIP(Dual In-line Package)为双列直插式封装;QFP(Quad Flat Package)为四方引脚扁平式封装;LCC(Leadless Chip Carriers)为无阵脚芯片封装;PGA(Pin Grid Array package)为插针网络阵列封装;WB BGA(Wire Bond Ball Grid Array package)为引线键合球栅阵列封装;SOT/TSOP(Small Outline Transistor/Thin Small Outline Package)为薄小外形封装;SiP(System in Package)为系统级封装;FC BGA/CSP(Flip Chip BGA package/Chip Scale Package)为倒装芯片球栅阵列封装/芯片尺寸封装;WL CSP(Wafer Level CSP)为圆片级芯片尺寸封装;QFN(Quad Flat No-lead package)为四方无引脚扁平式封装;PoP/PiP(Package on Package/Package in Package)为封装叠封装/封装内封装;3D WLP(3D Wafer Lever Package)为三维圆片级封装;2.5D interposer为2.5D转接板;FO WLP(Fan-Out WLP)为扇出型圆片级封装;Embedded SiP为芯片埋入式系统级封装;3DIC为三维集成电路;FO PoP(Fan-Out PoP)为扇出型封装叠封装;FO SiP(Fan-Out SiP)为扇出型系统级封装。

目前主流的微系统先进封装形式主要包括以下几种:

1)“封装叠封装”(Package on/in Package,PoP/PiP)[3]。即对2个或2个以上已有封装体进行垂直堆叠。该封装形式封测简便,且有效提高了系统集成度,已经实现工程化应用。如图3(a)所示,iPhone 5的A7处理器即采用PoP/PiP封装形式。PoP/PiP在某种程度上属于3D封装,但是在集成度方面不如以下2种封装形式。

2)片上系统集成(System on Chip,SoC)。从设计的角度出发,将各种不同功能模块集成在一块芯片上,在芯片上实现系统的功能,如图3(b)所示。在理想的情况下,SoC可以实现最低的成本、最小的尺寸和最优的性能。

3)系统级封装(System in Package,SiP)[4]。从封装的角度出发,将各种不同功能模块(芯片)集成在一个封装体内,如图3(c)所示。2005年国际半导体技术发展路线图(ITRS 2005)在组装与封装中对SiP的定义是:“系统级封装是采用任何组合,将多个具有不同功能的有源电子器件、可选择性的无源元件以及诸如MEMS或光学器件等其他器件首先组装成可以提供多种功能的单个标准封装件,形成一个系统或者子系统”。

图3 3种封装形式示意图

迄今为止,在IC芯片领域,SoC是最高级的芯片;在IC封装领域,SiP是最高级的封装。一方面,SiP涵盖了SoC;另一方面SoC也简化了SiP。但是采用SoC的方案还无法解决非硅基芯片(如GaAs、GeSi芯片)和微机电系统(MEMS)芯片的异质集成。而SiP使用成熟的组装和互连技术,把各种集成电路如CMOS电路、GaAs电路、GaN电路、SiGe电路或者光电子器件、MEMS器件以及各类无源元件如电容、电感等集成到1个封装体内,实现整机系统的功能。经过十几年的发展,SiP已经被学术界和工业界广泛接受,成为电子技术研究热点和技术应用的主要方向之一,并被认为代表了今后电子技术发展的主要方向之一[5]。目前iPhone 6已经部分采用SiP封装,iPhone 7将全部采用SiP封装,主板将被取代,从而实现高集成、高性能移动终端微系统。

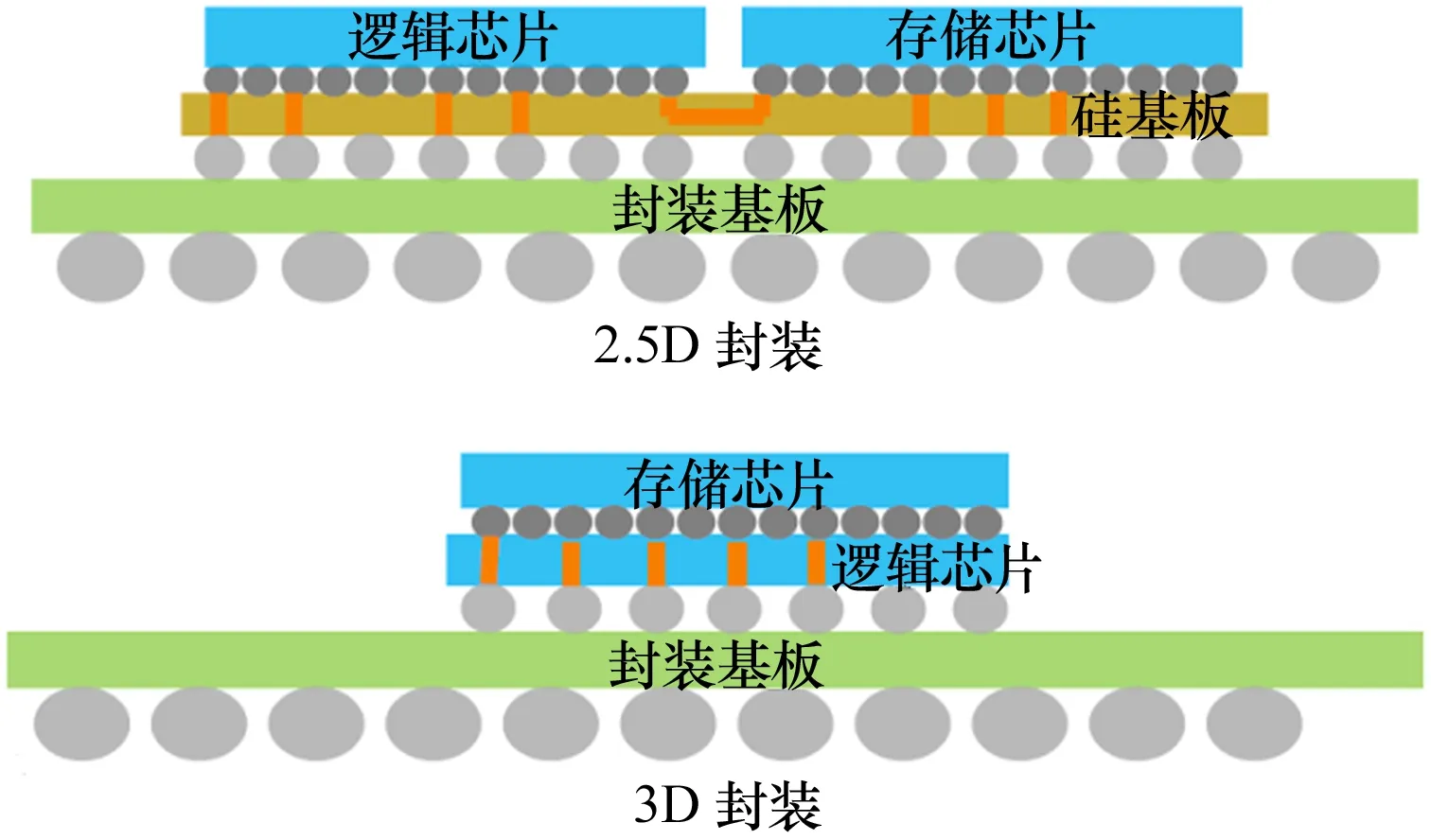

SiP不再是一种单纯的封装技术,而是涉及芯片堆叠(CoC)、圆片级封装(WLP)、硅通孔(TSV)、埋入式基板、微凸点/铜柱、倒装等多种技术的系统整合。目前与TSV技术关联的3D-SiP技术(WLP、微凸点/铜柱等)正面临一个全新的3DIC概念[6-7]。TSV利用垂直硅通孔完成芯片间的互连,能实现更小更薄、性能更好、密度更高的封装效果,在提高封装密度的同时,可改善电学性能,对散热也有帮助。在容许的成本范围内,主流器件设计和生产过程中可采用TSV来实现三维集成。2.5D封装是采用具有TSV结构的转接板作为桥梁,进行多芯片高密度互连,是2D封装技术的升级,可在集成度和性能方面得到巨大的提升;3D封装是自身具有TSV结构的芯片之间垂直堆叠与高密度垂直互连,实现3DIC,2种封装的示意图如图4所示。2.5D封装不仅仅是3D封装的过渡结构,这2种封装结构都是实现微系统封装的必要制程,一般可以同时存在于同一个SiP中。

图4 2.5D和3D封装结构示意图

2 微系统2.5D/3D封装关键技术

2.1 TSV技术

TSV与传统应用于多层互连的通孔有所不同,其通孔尺寸很小,直径通常仅为5~50 μm,深度为10~200 μm,传统工艺难以满足这样的高深宽比要求。得益于先进工艺设备的发展,TSV工艺才得以实现,主要包括通孔刻蚀、通孔薄膜淀积(氧化硅钝化层、阻挡层、种子层沉积)、通孔填充、化学机械抛光(CMP)等关键工序,其工艺流程如图5所示。

图5 TSV工艺流程图

TSV技术为集成电路和其他多功能器件的高密度混合集成提供了可能,可实现芯片与芯片间垂直叠层互连,无需引线键合,有效缩短互连线长度,减小信号传输延迟和损失,提高信号速度和带宽,降低功耗和封装体积,是实现多功能、高性能、高可靠且更轻、更薄、更小的半导体系统级封装的有效途径之一[8]。

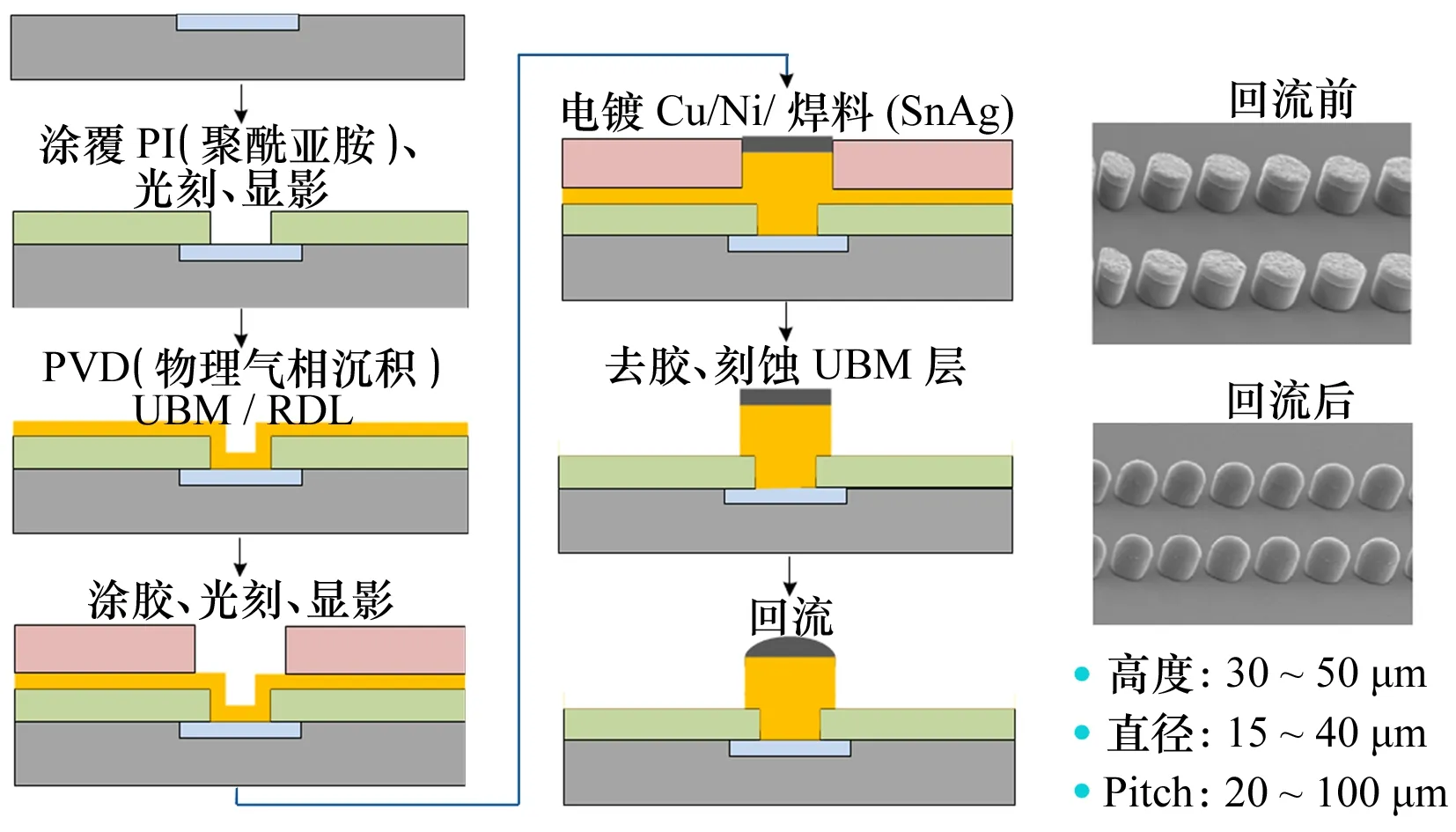

2.2 微凸点/铜柱技术

为了进一步提高封装集成密度,通常2D封装所采用的引线键合带来的尺寸限制及可靠性问题不容忽视。与一般2D封装技术相比,倒装焊技术可以在纵深方向上得到更大的发展空间,而不会增加器件的投影面积,因此可以将组件制作得更加复杂,功能更多,并提高组件的集成度。该技术可以不需要额外的引线,在加工圆片时也不用考虑引线键合点的大小和位置,因此内部互连线路更短、更有效,这样减少了寄生电容存在的可能性,提高了电路运行的速度和信号传输的可靠性。随着芯片密度越来越高,芯片之间的间距不断减小,铜柱技术逐渐取代了锡铅凸点,成为倒装焊工艺主流技术。铜柱尺寸更小,互连密度更高,可采用电镀工艺批量制作,具有高尺寸一致性和低成本的优点,其工艺流程如图6所示。得益于Cu材料特性,铜柱相比焊料球具有更高的电导率和热导率,满足当前和未来的高密度封装需求。

图6 铜柱电镀工艺流程

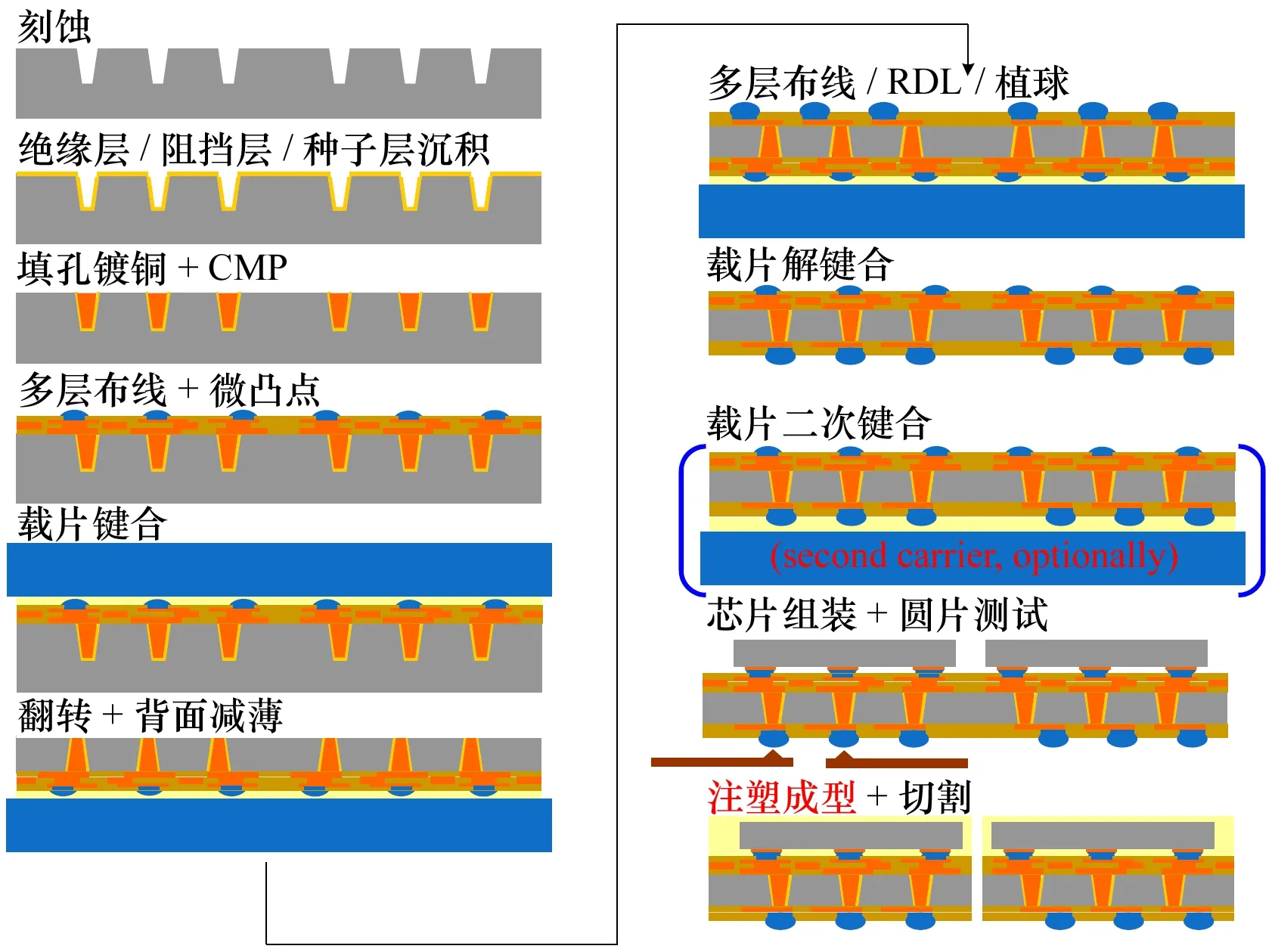

2.3 2.5D/3D WLP技术

WLP[9]技术以圆片为加工对象,在圆片上同时对众多芯片进行封装、老化、测试,最后切割成单个器件。WLP技术与TSV技术的结合有效推动了2.5D/3D封装技术向低成本工程化应用的进程。WLP技术作为SiP先进封装重要组成部分,已经将TSV技术、UBM/RDL(凸点下金属化层/再分布层)技术、微凸点/铜柱技术、倒装焊技术、芯片埋入技术、Fan-out技术、圆片减薄技术、圆片键合技术整合为综合性工艺流程,为微系统工艺整合提供解决方案。图7所示为一种基于TSV转接板的圆片级封装工艺流程。

图7 一种圆片级封装工艺流程

3 射频微系统2.5D/3D封装技术应用

基于TSV的2.5D/3D集成与封装已经在微机电(MEMS)、影像传感器(CIS)以及存储器(FLASH、DRAM)等产品的大规模量产中广泛应用,并延伸至绘图芯片、多核处理器、电源供应器和功率放大器、FPGA等芯片产品领域。在射频微系统领域,2.5D/3D封装技术还未出现工程化应用,但相关应用研究报道已经越来越多。

3.1 3D集成无源器件

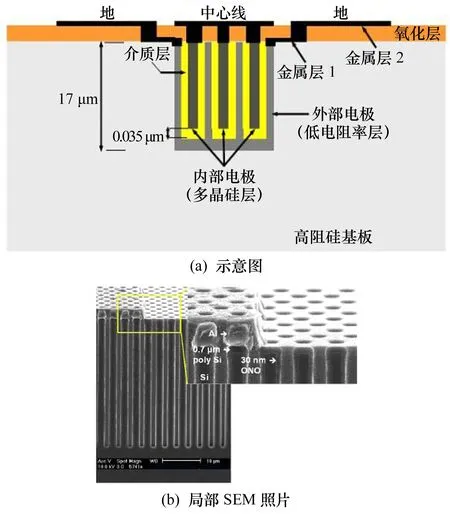

基于TSV的3D互联技术的出现大大推动了高性能集成无源器件的发展。恩智浦半导体公司推出的无源集成器件互连基板(Passive Integrated Connecting Substrates,PICS)技术[10]主要利用TSV相关的深反应刻蚀技术、薄膜淀积技术,直接在硅基转接板上集成3D电感、3D电容等无源器件。相比传统表贴的平面电感、电容,3D无源器件可具备更高Q值电感、更高比容电容,并且直接集成在基板上,取代表贴器件,极大程度减少空间占用,进一步提高射频微系统集成度,减小尺寸、重量及成本。恩智浦半导体公司研制的新型3D电容结构如图8所示,利用深反应刻蚀技术在高阻硅基板上刻蚀高密度TSV阵列,并沉积介质层/多晶硅层/金属层薄膜阵列。这种结构能够在很大程度上提高器件比表面积,从而得到更高比容电容。该3D比容达25~250 nF/mm2,串联电阻低于100 mΩ,串联自感低于25 pH,使用频率达50 GHz。IPDiA公司已经利用这一技术向市场提供适合3D封装的集成无源器件。

图8 基于TSV技术的3D高密度电容结构

恩智浦半导体公司研制的新型3D螺线管[11]同样基于TSV互连技术,如图9所示。

图9 基于TSV的3D螺线管结构

该螺线管利用TSV的垂直互连作用,结合正反面布线技术,形成具有GSG焊盘结构的3D矩形线圈并集成在基板内部。恩智浦半导体公司利用此3D螺线管结构设计并研制了带宽分别为16%和29%的滤波器,并取得优异的性能(带宽为16%的滤波器,中心频率S波段,插入损耗-2.6 dB,回波损耗-16 dB;带宽为29%的滤波器,中心频率V波段,插入损耗-2 dB,回波损耗-18.5 dB)。因此,基于TSV的3D无源器件在高性能毫米波微系统中具有非常优异的应用前景。

3.2 2.5D/3D封装射频微系统

随着TSV技术、微凸点/铜柱技术、WLP技术及其关联技术的系统性整合日趋成熟,微系统集成封装应用逐渐迈向产业化、工程化应用,目前主要集中于CIS、DRAM等低频领域。在射频领域,目前最新的2.5D/3D封装主要集中于利用TSV转接板实现的异构集成射频微系统,但仍处于研究阶段,尚未出现工程化应用。具有TSV结构的转接板作为2.5D/3D封装集成的核心结构,通过TSV提供垂直互连大大缩短了连线长度,同时其热膨胀系数与芯片较好匹配,并兼容圆片级工艺和薄膜多层工艺,可实现无源器件、MEMS、腔体、微流道、多芯片的高性能异构集成。

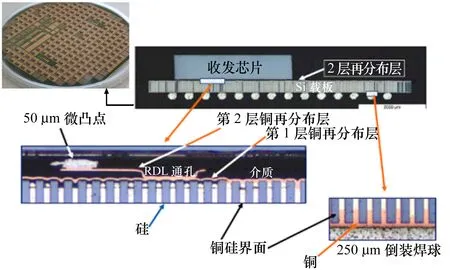

德国Fraunhofer研究所报道了一种利用TSV转接板实现的圆片级异质集成射频发射组件[12],如图10所示。该结构在TSV硅基转接板上通过2层薄膜布线技术实现无源器件集成,TSV直径50 μm,发射芯片通过倒装焊技术组装在转接板上,微凸点采用电镀SnAg焊料,尺寸为50 μm,组件对外接口为250 μm BGA球。

图10 一种圆片级封装射频发射组件

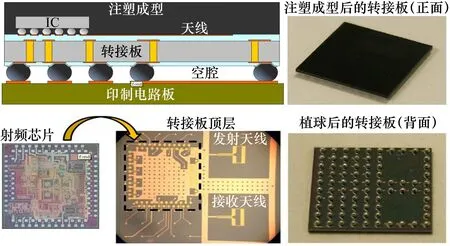

LETI公司研制了基于TSV硅基转接板3D封装的T/R组件(6.5 mm × 6.5 mm × 0.6 mm)[13],如图11所示。TSV转接板采用120 μm高阻硅材料,通过薄膜多层布线技术集成了天线系统,互连微凸点直径80 μm,收发射频芯片倒装于转接板上,转接板通过BGA与印制电路板连通。该组件的高频工作性能优异,阻抗匹配为57~68 GHz(17.6%),57~66 GHz增益为0~5.5 dBi,效率大于80%;在可靠性方面也显示出优异的性能。该组件结构在未来毫米波射频微系统应用中具有很大潜力。

图11 一种相控阵射频前端组件

4 射频微系统2.5D/3D封装面临的挑战——热管理技术

随着微系统集成度提高,体积明显减小,功耗明显降低,但热效应问题却越发突出,可能导致器件性能恶化,甚至失效。军用电子系统大量使用的功率元器件热流密度更大,应用环境也更恶劣,其热管理难度更大。IBM公司认为,如果没有良好的冷却措施,未来芯片温度将达到6 000 ℃,超过太阳表面的温度。因此,微系统性能最终受到散热能力的制约,其热管理技术是目前迫切需要解决的技术难题。针对3D封装微系统,新型散热技术逐渐得到开发,目前正在开发的几种新型热管理技术包括:

1)微导热管,导热量100~300 W/cm2,导热管形式多样,包括折叠式、循环式、振动式,但集成度不高。

2)喷淋散热,导热量100~400 W/cm2,直接向热源喷雾散热,需要低压,实用性不高。

3)热电冷却,导热量> 200 W/cm2,利用热电效应冷却,但导热效率较低。

4)微流道,导热量100~1 300 W/cm2,可采用气体或液体导热,效率高;可与器件工艺同步完成,集成度高。

在对流传热方面,除了增大流量外,通过压缩通道截面以增大热边界层的温度梯度从而提高对流换热系数,或者通过并联更多的通道以增加有效换热面积,都是增强对流传热的有效途径。而微流道技术可将这两方面做到极致,被认为是目前最具潜力的微系统热管理技术。国外研究机构以微系统2.5D/3D先进封装工艺技术为基础,设计并研发了新型硅基微流道结构。

图12是Georgia研究所研制的一种微流道散热结构。该结构为3层TSV转接板堆叠,TSV具备TSEV和TSFV两种功能,TSEV作为信号垂直传输通孔;TSFV作为垂直导热微流道,并将基板表面横向导热沟槽联通起来。各层信号通过微凸点键合实现信号互连,微流道之间通过聚合物管道键合实现冷却液互连,聚合物管道与微凸点高度均为60 μm。

图12 一种微流道散热结构

5 结束语

文章介绍了射频微系统2.5D/3D先进封装技术的发展趋势,以及在集成无源器件、射频前端系统方面的应用及挑战,为射频微系统集成技术研究提供参考:

1)为满足微系统小型化、高集成度、高性能等需求,2.5D/3D先进封装技术将以TSV技术、微凸点/铜柱、圆片级封装等先进的高密度封装技术为主要发展方向;

2)基于TSV技术的2.5D/3D封装已经在MEMS、CIS、DRAM等产品中广泛应用,在射频微系统封装应用中具有良好应用前景,但目前还未进入工程化应用阶段;

3)热管理将是射频微系统2.5D/3D封装技术不容忽视的挑战。

[1] Yole Développement. 3D TSV Interconnects: device & systems[EB/OL]. [2016-07-20]. http://www.i-micronews.com.

[2] Yole Développement. 3DIC & TSV interconnects [EB/OL]. [2016-07-20]. http://www.i-micronews.com.

[3] DREIZA M, YOSHIDA A, ISHIBASHI K, et al. High density PoP (Package-on-Package) and package stacking development[C]//2007 Proceedings of 57th Electronic Components and Technology Conference, 2007: 1397-1402.

[4] 李维平, SCANLAN C, YOSHIDA A. 系统模块(SiP)和三维封装(3D)在移动通讯中的应用[J]. 电子工业专用设备, 2004, 33(7): 10-14.

[5] 蔡坚, 王水弟, 贾松良. 系统级封装(SiP)集成技术的发展与挑战[J]. 中国集成电路, 2006(9): 60-63.

[6] 胡杨, 蔡坚, 曹立强, 等. 系统级封装(SiP)技术研究现状与发展趋势[J]. 电子工业专用设备, 2012(11): 1-6.

[7] 朱健. 3D堆叠技术与TSV技术[J]. 固体电子学研究与进展, 2012, 32(1): 73-77.

[8] 吴向东. 三维集成封装中的TSV互连工艺研究进展[J]. 电子与封装, 2012, 12(2): 1-5.

[9] 童志义. 圆片级封装技术[J]. 电子工业专用设备, 2006(12): 1-6.

[10] WANE S, MÜHLHAUS V, RAUTIO J. Electromagnetic macro-modeling of 3D high density trenched silicon capacitors for wafer-level-packaging[C]//IEEE MTT-S International Microwave Symposium Digest, 2008: 519-522.

[11] TESSON O, DUPLESSIS M, CHARLOT S. Electro-magnetic modeling and design of through silicon vias based passive interposers for high performance applications up to the V-band[J]. International Journal on Advances in Systems and Measurements, 2012, 5: 55-69.

[12] WOLF M J, RAMM P, KLUMPP A, et al. Technologies for 3D wafer level heterogeneous integration[C]//2008 Symposium on Design, Test, Integration and Packaging of MEMS/MOEMS, 2008: 123-126.

[13] DUSSOPT L, EL BOUAYADI O, LAMY Y, et al. Millimeter-wave transceiver module integration in 3D silicon interposer technology[C]//5th Design for 3D Silicon Integration Workshop, 2013.

[14] DANG B. Integrated Input/Output Interconnection and Packaging for GSI[D]. Georgia Institute of Technology, 2006.

崔 凯(1985-),男,博士,工程师,主要从事厚薄膜混合工艺和先进封装工艺技术研究工作。

Development and Application of 2.5D/3D Packaging Technology for RF Microsystem

CUI Kai,WANG Cong-xiang,HU Yong-fang

(NanjingResearchInstituteofElectronicsTechnology,Nanjing210039,China)

2.5D/3D packaging technology is the main method for future RF system demands such as higher integration, better system performance, higher operating frequency. In this paper, the development trend of microsystem 2.5D/3D packaging technology and advanced high density packaging technologies such as TSV, micro-bump/copper pillar, wafer level package are introduced. The application and challenge of 2.5D/3D packaging technology in the field of RF microsystem are also discussed to provide a reference for the research of RF microsystem integration and packaging technology.

2.5D/3D packaging; RF microsystem; through silicon via (TSV); wafer level package (WLP); thermal management

2016-08-25

TN305.94

A

1008-5300(2016)06-0001-06