嵌入式控制系统的串口扩展设计方法

2016-04-20西南技术物理研究所杨光海彭晓乐王之昊

西南技术物理研究所 杨光海 彭晓乐 张 川 王 海 孙 海 徐 丹 王之昊

嵌入式控制系统的串口扩展设计方法

西南技术物理研究所 杨光海 彭晓乐 张 川 王 海 孙 海 徐 丹 王之昊

【摘要】本文以工程应用为出发点,阐述了在嵌入式控制系统中,两种不同的实现UART扩展的方法,从而实现不同方式的多串口扩展,以供工程开发者进行选用。 嵌入式;UART;多串口

0 引言

嵌入式系统(Embedded system),是一种“完全嵌入受控器件内部,为特定应用而设计的专用计算机系统”,根据英国电气工程师协会( U.K. Institution of Electrical Engineer)的定义,嵌入式系统为控制、监视或辅助设备、机器或用于工厂运作的设备。与个人计算机这样的通用计算机系统不同,嵌入式系统通常执行的是带有特定要求的预先定义的任务。由于嵌入式系统只针对一项特殊的任务,设计人员能够对它进行优化,减小尺寸降低成本。

嵌入式控制系统是一个控制程序存储在ROM中的嵌入式处理器控制板。嵌入式控制系统的核心是由一个或几个预先编程好以用来执行少数几项任务的微处理器(DSP或单片机)组成。事实上,所有带有数字接口的设备,如微波炉、录像机、汽车等,都使用嵌入式控制系统,大多数嵌入式控制系统都是由单个程序实现整个控制逻辑。

在嵌入式控制系统中,各部件间的计算机微控制芯片(DSP或单片机)都需要进行数据交换建立通讯联系,使用串行通讯手段是其中一种重要、常用的通讯方式。串行通讯工作方式分为同步方式和异步方式两种,在实际工作中,异步方式用得最多,本文主要讨论异步方式,其包括三个常用的总线标准:RS-232、RS-422、RS-485。

串行通信接口(串口)在嵌入式控制系统数据通信中一直扮演极重要的角色, 具有线路简单、应用灵活、可靠性高等优点,它不仅没有因为技术的进步而被淘汰,反而呈现向速度等极限挑战的趋势。 串口已成为许多高端C PU和低端单片机的标准配置。但是目前的嵌入式芯片,包括单片机或DSP芯片中,目前最多二个串口,几乎没有超过这个数目的,因此,软件模拟串口的收发工作往往是此类系统的扩展多串口的首选方案,但该方案不仅占用资源,且应用效果并不理想,如何在此类系统中扩展串口,以满足其具体应用,无疑具有现实意义。

1 串口实现方法

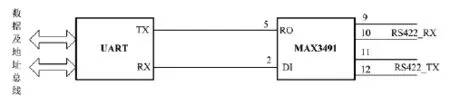

从硬件的角度来说,串口的实现方法是串口驱动芯片配上异步串口收发器UART(Universal Asynchronous Receiver/Transmitter)即可实现。如图1所示,以MAXIM公司的RS422驱动器MAX3491为例,说明一路异步串口实现的方式。实现多路串口,即实现图1所示串口的叠加。

图1 异步串口实现示意图

一般来说,嵌入式系统中实现多路串口的瓶颈在于微控制芯片(DSP或单片机)的UART端口较少,所以,实现串口扩展的关键在于UART的扩展,串口驱动器。实现UART扩展的方法有两种,一种是利用串口扩展芯片实现,这类芯片较多,例如TI公司的UART扩展器16C550、16C552、16C554、16C754等芯片,一片最多能扩展4路串口,本文以TI公司的TL16C554为例,讲述利用UART扩展器扩展串口的方法,另一种是利用FPGA芯片进行串口扩展,在FPGA芯片内以Verilong为硬件描述语言,实现串行通讯的接收模块和发送模块,一颗FPGA芯片可实现多路串口的接收模块和发送模块。上述两种方法的基础上搭配串口驱动芯片,从而实现多路串口的扩展。

2 利用UART扩展器扩展UART的方法

2.1 TL16C654功能特点

TL16C654是TI公司的异步通讯芯片,其主要特点如下:

●具有4通道异步通讯收发器(UART);

●最高可达1Mbits/s的波特率,波特率发生器可软件编程设置;

●16字节的先进先出存储器(FIFO),FIFO均可设置触发中断字节数;

●标准的异步通讯状态位,包括起始位,停止位,校验位;

●每个通道独立控制发送、接收、线态和数据装置中断

●具有可编程的数据格式

数据位长度为5、6、7、8;

可设置为奇校验、偶校验、无校验模式;

停止位长度可设置为1、1.5、2;

●缺省的数据起始位检测;

●每个通道的数据和控制总线采用三态TTL驱动;

●中断优先控制系统;

●Modem 控制功能;

TL16C554的主要引脚的功能说明如下:

A0~A2:片内寄存器的选择信号;

D0~D7:双向8位数据线信号;

CSA、CSB、CSC、CSD:输入片选信号,分别能使4个串行通道读写操作;

XTAL1、XTAL2:晶振或外部时钟输入输出端,该脚可接外部晶振或时钟信号;

INTA、INTB、INTC、INTD:4个串行口中断输出;

RXA、RXB、RXC、RXD:串行数据输入引脚;

TXA、TXB、TXC、TXD:串行数据输出引脚;

RESET:复位信号输入引脚;

IOR、IOW:输入/输出读/写选通脉冲。

TL16C554的每路串行UART通道均有10个寄存器可被CPU访问,这些寄存器分别用于通讯参数的设置、FIFO的控制、对线路及Modem的状态访问、数据的发送和接收、中断管理等功能。编程人员可由A0、A1、A2三条片内寄存器选择线和线路控制寄存器的除法数锁存器访问位LCR及IOR、IOW一起通过多路复用进行访问或控制TL16C554的任何一个寄存器。表1给出了访问这些寄存器的LCR、A0、A1、A2以及读写的状态。

2.2 串口扩展的实现

以TL16C654与其他设备进行串行通讯相关的寄存器作简单介绍。

两个8位波特率因子寄存器以一个16位的二进制格式存贮波特率因子。波特率因子可通过下列算式求出:

波特率因子=基准时钟频率/(16×波特率)

表1 TL16C554的片内寄存器

根据串口波特率,选择合适的晶振频率给16C654芯片提供基准时钟频率,根据上式计算出波特率因子,以便在软件编程时设置。写入波特率因子前必须置线路控制寄存器(LCR)的bit7位为1,写入波特率因子后应将线路控制寄存器(LCR)的bit7位恢复为0。

将TL16C554芯片的串行串行数据输入、输出引脚接在串口驱动芯片的串行数据的输出、输入引脚上,如MAXIM公司的MAX3491芯片的DI、RO引脚上,即可以实现串口的扩展。

3 利用FPGA扩展UART的方法

3.1 概述

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

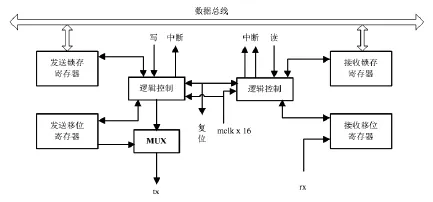

完整的UART接口包括发送锁存器、发送移位寄存器和逻辑控制组成的发送模块,以及由接收锁存器、接收移位寄存器和逻辑控制组成的接收模块,其UART接口结构图如图2所示。

UART的帧格式,一般包括空闲状态(高电平)、起始位(低电平)、5~8位数据位、校验位(可选,高电平或低电平)和停止位(高电平,位数可为1、1.5、2位)。

UART包含一个可编程的波特率发生器,可按照需求配置波特率。波特率发生器给串口数据发送模块和接收模块提供发送数据和接收数据的基准时钟信号,其产生的时钟mclk x 16 是串行数据波特率的16倍,它对系统时钟的n分频,n=系统时钟/波特率 x 16,可根据需要的波特率设置相应的数值。

图2 UART接口结构

3.2 发送模块设计

当数据总线上并行的8位数据从总线写入发送模块后,发送模块将并行数据装入锁存器中,然后在位移寄存器中将数据移位,产生完成的发送序列(包括起始位,数据位,校验位和停止位),以相应的波特率从tx发送。

发送模块部分Verilong程序如下:

.cpu_clk(cpu_clk),

.send_clk(clk_out),

.rst_n(rst_n),

.cpu_write(cpu_write),

.cpu_ce(cpu_ce),

.cpu_data(cpu_data),

.cpu_add(cpu_add),

.send_flag(send_flag),

.uart_txdata(uart_txdata),

.s_full_bit(s_full_bit),

.s_empt_bit(s_empt_bit)

3.3 接收模块设计

接收模块首先捕捉起始位,在mclk x 16时钟下不断检测从rx端输入数据的起始位,当检测到起始位后,接收模块由空闲模式转换为移位模式,并且16分频mclk x 16产生rxlk时钟的上升沿位于串行数据每一位的中间,这样接下来的数据在每一位的中点采样。然后由rxclk控制在上升沿将数据位写入移位寄存器rsr的rsr[7]位,并且rsr右移1位,依次将8位数据全部写入rsr,并且停止产生rxckl波特率时钟。判断检验位、帧结构正确后,rsr寄存器中的数据写入数据锁存寄存器中,最后由8位数据总线输出转换完成的数据。

接收模块部分Verilong程序如下:

.rst_n(rst_n),

.rx_clk(clk_16_out),

.rx_data_ready(rx_data_ready),

.rx_data (rx_data),

.num_to_int(num_to_int),

.aclr(aclr),

.int_choose(int_choose),

.cpu_clk(cpu_clk),

.cpu_read(cpu_read),

.cpu_add(cpu_add),

.cpu_ce(cpu_ce),

.cpu_int(cpu_int),

.r_fifo_bit(r_fifo_bit),

.r_over_bit(r_over_bit)

4 结束语

通过UART的扩展实现了串口的扩展,采用UART扩展器的方法具有工作稳定,具有一定FIFO深度,不需额外增加软件开发、管理的成本,但是使用的灵活不够。采用FPGA扩展UART的方法使用灵活性强,但需额外增加软件开发、管理的成本。用户可以根据实际使用情况选用UART的扩展方法,以提高工作效率。

参考文献

[1]朱学明,丁万山.一种基于TL16C554A的DSP多串口扩展方法[J].微处理机,2006,6:24-27

[2]田红霞,戴彦,鹿玉红.基于FPGA的RS232串行接口设计[J].煤炭技术,2010,9(29):194-196.

[3]李金力,刘文怡,彭旭峰.基于FPGA的RS232异步串行口IP核设计[J].电子设计工程,2009,8(17):31-31,35.

[4]Texas Instruments.TL16C554,TL16C554I ASYNCHRONOUS COMMUNICATIONS ELEMENT.

[5]MAXIM,3.3V-Powered,10Mbps and Slew-Rate-LimitedTrue RS-485/RS-422 Transceivers.

杨光海(1978—),大学本科,工程师,研究方向:嵌入式控制。

作者简介: