多通道雷达数字接收机数字下变频设计*

2016-03-18黄世锋陈章友岳显昌

黄世锋,陈章友,张 兰,2,岳显昌,2

(1.武汉大学 电子信息学院,湖北 武汉 430072;2.武汉大学 地球空间信息技术协同创新中心,湖北 武汉 430079)

多通道雷达数字接收机数字下变频设计*

黄世锋1,陈章友1,张 兰1,2,岳显昌1,2

(1.武汉大学 电子信息学院,湖北 武汉 430072;2.武汉大学 地球空间信息技术协同创新中心,湖北 武汉 430079)

提出一种基于时分复用原理的双频段多通道数字接收机DDC模块的设计方法,并利用FPGA的数控振荡器和FIR滤波器的 IP核完成了 DDC模块的设计与实现。仿真结果表明,该设计实现了数字混频、抽取和滤波的功能,与其他设计方案对比表明,本方案有效地减少了FPGA资源的使用量,降低了硬件设计的复杂度,节约了硬件成本。

数字接收机;同时双频段;多通道;数字下变频;时分复用

0 引言

高频地波雷达利用高频电磁波沿高电导率海水表面的绕射特性,实现对海洋状态环境(如风、浪、流等海洋动力学参数)和海面移动目标的超视距探测[1]。接收机是雷达系统的核心组件,直接影响雷达系统的总体技术指标。传统高频地波雷达接收机常采用高中频结构,通过模拟前端来实现对接收信号的放大、滤波、混频和中频输出等。随着软件无线电技术与超大规模集成电路的迅速发展,接收机的全数字化已成为一种趋势[2]。全数字接收机通过对接收天线所收到的回波信号进行直接采样后,后续的处理如信号的混频、滤波、抽取等部分由数字下变频(Digital Down-Converter,DDC)模块来完成。全数字化接收机模拟前端设计大大简化,在减小了设备的体积和复杂度的同时,也有利于提高系统的通道一致性,相对于传统接收机,在系统的可靠性、稳定性、平台通用性等方面均具有明显的优势。因此,目前高频地波雷达接收机的设计逐渐开始采用全数字化设计。

DDC模块作为接收机的一个关键部分,相对于单通道接收情况,双频多通道接收机 DDC功能的实现要复杂得多。文献[3]采用4个DDC模块来实现同时双频段8通道DDC。利用可编程门阵列(Field Programmable Gate Array,FPGA)可较方便地实现单通道 DDC,但该方案采用并行方式,每个通道单独使用一个下变频模块,虽然实现起来简单,但会占用过多 FPGA资源,而且会增加功耗。FPGA数控振荡器(Numerical Controlled Oscillator,NCO)和有限冲击响应(Finite Impulse Response,FIR)滤波器的 IP核都支持多通道时分复用功能[4],可借此完成多通道DDC。

本文提出一种基于时分复用的思路完成双频8通道DDC设计的方法,仿真结果表明,基于该方法实现的DDC模块在确保实现预期功能的同时,大大降低了FPGA开销,节省了系统资源。

1 DDC设计原理

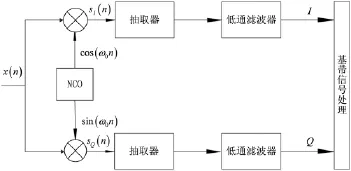

DDC模块包括数字混频器、NCO、抽取滤波3部分[5]。单通道DDC一般结构如图1所示。NCO是信号产生器,产生混频时正交本振信号 cos(ω0n)与 sin(ω0n),其中 ω0为本振频率。数字混频器将接收的高速采样信号 x(n)分别与正交本振信号相乘,产生正交的 I、Q两路信号。

图1 单通道数字下变频结构图

设输入的离散解析信号为:

式中a(n)是信号的幅度,ω0是信号的载波频率,Ψ(n)是信号的基带相位。式(1)乘以载波分量 e-jω0n再经过低通滤波器可下变频到基带,即:

抽取过程可降低混频之后基带信号的数据率,方便后续信号处理。设正交混频之后信号s(n)的频谱为S(ejω),经整数 D倍抽取后信号 sD(m)频谱为SD(ejω),则:

抽取序列的频谱是原始序列频谱经频移和 D倍展宽后D个频谱叠加和。抽取信号经滤波器滤波可以得到基带信号,通常由设计合适的积分梳状滤波器(Cascaded Integrator Comb,CIC)[6]、半带滤波器(Half Band,HB)[7]、或 FIR滤波器来完成,设计滤波器时需防止频谱混叠。

2 多通道接收机DDC设计

2.1 接收机整体设计

设计的高频雷达数字接收机同时工作在高低两个频段,对应两个发射通道,8个接收通道。天线接收的信号首先经过带通滤波器,经 8通道模数转换器(Analogto-Digital Converter,ADC)采样,采样后的信号送至FPGA,完成数字下变频和数据上传。FPGA还完成发射波形的数字产生,数字信号经两通道的数模转换器(Digital-to-Analog Converter,DAC)转换成模拟信号,最后经过带通滤波器滤波送至发射机。

2.2 NCO

NCO产生两路正交线性调频信号的同相分量和正交分量。接收端是高低频段同时工作,混频时需要两个NCO,分别产生高低两个频段的两路本振信号。NCO IP核支持多通道时分复用功能,用一个IP核即可。经 ADC转换的信号数据率是 48 MS/s,NCO产生的本振信号数据率也是 48 MS/s,NCO IP核的工作时钟定为96 MHz,通道数设为2。

2.3 数字混频器

采用正交混频机制,正交混频可避免实信号频谱存在正负对称频率问题[8],混频时对高低频段进行时分复用,即单通道接收的高低两个频段信号在一个混频器里进行混频,可减少一半混频器的数目。混频器输入信号的数据率是48 MS/s,数字混频器的工作频率设为96 MHz。这样每一通道经混频将高低频段的信号分开,采用正交混频,会产生 I、Q两路信号,因此原来的每通道数据经过混频之后变成了4通道数据,抽取滤波的通道数变为32。

2.4 抽取滤波器组

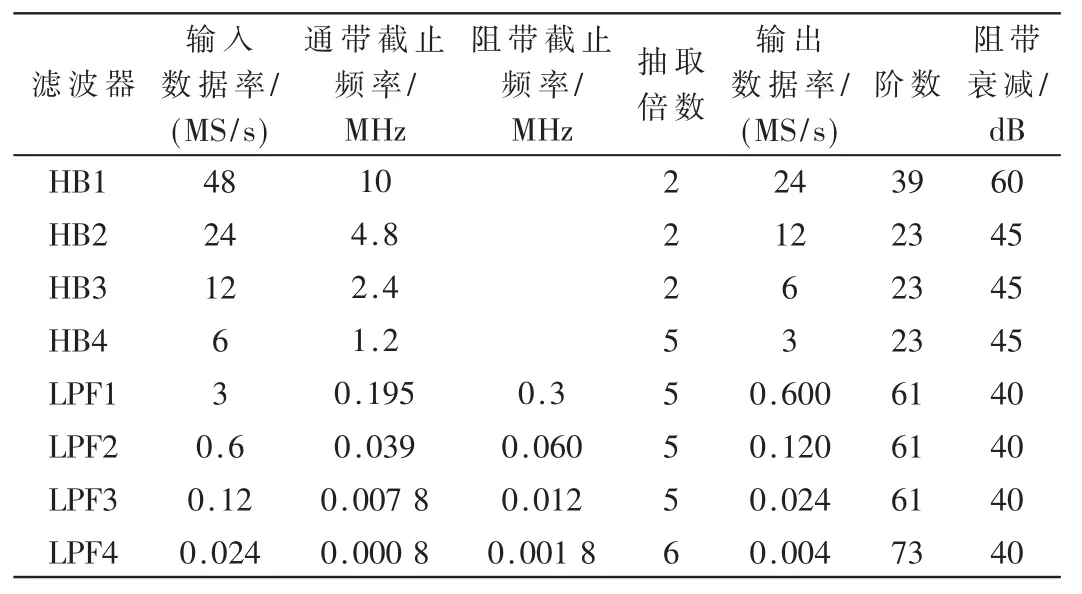

正交混频后通道数为32,每通道的数据率为48 MS/s,DDC之后进行1 024点的快速傅里叶变换,发射波形周期是250 ms,则变换之前的数据率为1 K/250 ms=4 KS/S,故 DDC抽取倍数为48(MS/S)/4(KS/S)=12 000。为实现12 000倍的抽取与滤波,我们设计了 8级滤波器级联方式的抽取滤波器组,如图2所示,前四级使用 HB滤波器,每级抽取 2倍,第五级到第七级 FIR滤波器抽取倍数均为5,最后一级 FIR滤波器抽取倍数为6。具体来看,系统抽取滤波模块的工作时钟是144 MHz,针对HB1来说,输入 HB1信号数据率为48 MS/S,它的时分复用因子 M=3,要完成 32通道的抽取滤波需要HB1数目为11,依次可以计算出每级滤波器的数目:6个 HB2,3个HB3,2个HB4,LPF1、LPF2、LPF3、LPF4的数目都是1。

图2 抽取滤波器组结构图

各级滤波器的设计通过MATLAB的FDATool工具箱完成,相应参数如表1所示。

表1 DDC滤波器组各滤波器参数表

3 TDM多通道DDC实现

在 Quartus里例化相应 IP核,搭建整个DDC模块,模块寄存器传输级(RTL)框图如图3所示。fmcw_gen模块是数字本振模块,产生高低两个频段正交混频需要的本振信号;mixer模块是数字混频器模块,实现 8通道的数字混频;ddc模块是8级 FIR滤波器构成的抽取滤波模块,完成 32通道的抽取滤波功能。

图3 DDC RTL图

4 结果分析

4.1 多通道DDC仿真结果

多通道 DDC仿真由 Modelsim完成。由于调频连续波周期为250 ms,在Modelsim里仿真起来耗时特别长,仿真简化处理如下:用单一频率的正弦波来代替线性调频中断连续波,8通道只仿真第一个通道,即只给第一个通道提供数据,其他通道输入为零。

仿真参数设定:低频段本振信号 7.53 MHz,高频段信号11.56 MHz;混频输入的测试信号是11.560 4 MHz和7.529 9 MHz两个正弦波的叠加。将Modelsim仿真的数据导入MATLAB做频谱分析,结果如下。

经计算,混频之后高频段信号有4个频率:f1=400 Hz、f2=4.031 MHz、f3=19.159 MHz、f4=23.124 MHz;低频段信号有4个频率:f1=100 Hz、f2=4.030 4 MHz、f3=15.059 9 MHz、f4=19.090 4 MHz。LPF4的通带截止频率是 0.8 KHz,经过LPF4输出只有100 Hz和 400 Hz的信号,图4是 LPF4的输出结果,从图中看到高频段只有 400 Hz的信号,低频段只有100 Hz的信号,表明抽取滤波结果正确。

LPF3的输出,理论上高频段只有 400 Hz的信号,低频段只有100 Hz的信号,仿真结果与理论值一致。由于篇幅限制这里未给出,其他滤波器的仿真结果也与理论值吻合,这里未一一列出。整体的仿真结果表明本文提出的多通道数字下变频实现方法是可行的。

4.2 时分复用与并行单通道模式资源对比

Quartus编译工程可以查看时分复用和并行单通道(以后简称并行模式)两种模式下资源的使用情况。在并行模式下,仅计算后四级FIR滤波器对资源的使用情况,表2给出了时分复用方式与并行方式滤波器组 FPGA资源的使用情况。

时分复用情况下,虽使用了较多的 HB1和 HB2滤波器,但 HB滤波器有一半的系数为零,比对称 FIR设计时的计算量少了一半,且 HB滤波器阶数不高,因此整体对FPGA资源消耗不大。后四级FIR滤波器虽然阶数稍高,但每一级的滤波器数目都是1,对资源消耗少。整体上节省资源。从表中可看出并行方式下存储块的使用是时分复用方式的近12倍,结果表明采用时分复用滤波器组的方式可节省较多FPGA资源。

图4 第八级高(上)低(下)频段抽取滤波结果

表2 FPGA资源占用情况比较

5 结论

本文针对同时双频多通道全数字接收机,提出了一种比较节省 FPGA资源的多通道 DDC实现方法,其核心是对NCO、混频器及FIR滤波器 IP核的时分复用,用一个滤波器组完成了 32通道数据的抽取滤波处理,把数据的速率从 48 MS/s降为4 kS/s。时分复用方式和传统并行方式进行DDC时FPGA资源使用情况对比分析表明,时分复用方式节省较多 FPGA资源,是一种比较有效的设计。仿真结果表明,本文设计的 DDC仿真结果与理论吻合。时分复用 FIR滤波器 IP核进行多通道DDC是一种比较可取的方式,通道数继续增加时,该方法仍然适用,可相应提高 IP核的工作时钟频率,增加 IP核的通道数。这种方法会在多通道全数字接收机里得到比较广泛的应用。

[1]施春荣,周涛,孙勇,等.高频地波雷达数字接收机设计[J].雷达与对抗,2008(4):36-38.

[2]王凡,高火涛,周林.基于 FPGA的多信道全数字高频雷达接收机[J].华中科技大学学报(自然科学版),2011,39(3):75-78.

[3]匡宏印,张庆祥.基于FPGA的多通道双频数字化接收机研制[D].哈尔滨:哈尔滨工业大学,2013.

[4]陈镜,曹芳菊.基于 IP核的滤波器复用模块的设计和实现[J].无线电工程,2010,40(4):26-29.

[5]屈有萍,周端.基于 FPGA的数字下变频研究实现[D].西安:西安电子科技大学,2007.

[6]侯永宏,侯春萍,曹达仲,等.数字下变频及抽取的 FPGA实现[J].电路与系统学报,2005,10(1):123-126.

[6]李林,杨万麟.基于FPGA的数字下变频的电路设计与实现[D].成都:电子科技大学,2006.

[8]薛年喜.MATLAB在数字信号处理中的应用[M].北京:清华大学出版社,2003:1-50.

Design of multi-channel digital down-converter of digital radar receiver

Huang Shifeng1,Chen Zhangyou1,Zhang Lan1,2,Yue Xianchang1,2

(1.School of Electronics and Information,Wuhan University,Wuhan 430072,China;2.Collaborative Innovation Center of Geospatial Technology,Wuhan 430079,China)

A digital down-converter(DDC)module in a multi-channel digital radar receiver executed at two frequencies is designed based on time division multiplexing(TDM)technique,this new DDC designed by using intellectual?property(IP)cores of the numerical controlled oscillator(NCO)and the finite impulse response(FIR)filter of a field programmable gate array(FPGA).Simulation of this new designed DDC shows that these functions,such as digital mixer,decimation and filter have been achieved.Furthermore,this new DDC reduces the occupation of FPGA resources,simplifies the complexity of hardware design and reduces the cost of hardware.

digital receiver;two working bands synchronously;multi-channel;digital down-converter;time division multiplexing

TN957

:ADOI:10.16157/j.issn.0258-7998.2016.06.012

黄世锋,陈章友,张兰,等.多通道雷达数字接收机数字下变频设计[J].电子技术应用,2016,42(6):46-48,55.

英文引用格式:Huang Shifeng,Chen Zhangyou,Zhang Lan,et al.Design of multi-channel digital down-converter of digital radar receiver[J].Application of Electronic Technique,2016,42(6):46-48,55.

2015-12-17)

黄世锋(1991-),男,硕士研究生,主要研究方向:无线电海洋遥感。

国家高技术发展研究计划(863计划)(2012AA091701);国家自然科学基金青年基金项目(61401316)

陈章友(1969-),男,副教授,主要研究方向:电磁场与微波技术。

张兰(1982-),通信作者,女,博士,实验师,主要研究方向:无线电海洋遥感,E-mail:zhanglan@whu.edu.cn。