1394总线三节点仿真设备设计与实现*

2016-03-18辛永利靳伟平陈飞茹

辛永利,靳伟平,贾 钊,陈飞茹

(1.中航工业西安航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点实验室,陕西 西安 710068;3.西安翔腾微电子科技有限公司,陕西 西安 710068)

1394总线三节点仿真设备设计与实现*

辛永利1,2,靳伟平3,贾 钊3,陈飞茹3

(1.中航工业西安航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点实验室,陕西 西安 710068;3.西安翔腾微电子科技有限公司,陕西 西安 710068)

由于单纯依靠机载环境进行1394总线验证测试不仅成本高、风险大、资源有限,而且具有很大的局限性,所以急需开发相应的地面仿真设备进行总线系统综合化仿真测试。结合1394协议在领域的需求,研发了一种满足1394协议的总线三节点仿真设备,该设备实现控制计算机(CC)、远程节点(RN)、总线监控(BM)、加载维护(LM)一体化设计,集节点数据收发、配置加载、故障注入、通信监控、拓扑显示、远程加载等功能于一体,可用于实验室环境下搭建完整的1394总线通信系统,构建各机载子系统设备之间复杂的互联情况,全面系统地完成总线仿真应用测试,为领域的机载总线应用提供支持与保障。

1394总线;仿真设备;三节点

0 引言

在机载、防务领域,仿真技术已经成为武器装备研制与试验中的一项核心关键技术,在综合化仿真环境和仿真系统的研制和建设中尤为重要。1394总线三节点仿真设备源于我国新型飞机综合化仿真环境的研制需求,产品从需求出发,结合多种复杂仿真应用环境,设计满足多个机载领域1394总线产品的试验验证需求,全面系统地实现机载网络环境的综合化仿真、测试,并辅助完成系统联试、试验。

本文从硬件设计、逻辑设计、软件设计三方面阐述1394总线三节点仿真设备的设计与实现过程,并通过搭建仿真试验环境,完成产品及系统级综合验证。

1 产品设计

1394总线三节点仿真设备主要应用于地面仿真环境下,实现1394总线系统中的控制计算机、远程节点、监控节点以及加载维护节点的虚拟仿真功能。产品设计中通过软硬件协同模式实现1394总线数据的收发功能[1],其链路层和物理层采用商业协议处理芯片实现了IEEE1394b总线链路层和物理层协议处理功能,传输层采用基于 FPGA逻辑电路实现 AS5643协议处理功能。同时每个产品配置 3条独立的总线接口,各总线拥有独立的软件及硬件接口资源,每条总线提供3个独立的端口(Port),支持S100B、S200B、S400B 3种传输速率。

1.1 硬件设计

1394总线三节点仿真设备硬件模块设计中主要包括:FPGA电路、电源电路、复位电路、时钟电路、1394接口电路,具体如图1所示。FPGA电路实现1394总线协议处理,通过链路层组包/解包,再由物理层进行编解码处理后通过接口电路发送到总线上,实现1394总线数据交互。

图1 仿真设备原理框图

(1)主机接口

PCI接口采用标准的PC卡接口金手指连接器,主机通过金手指连接器获得电源、访问板卡资源并与板卡进行数据交互,完成FPGA与主机的通信。PCI接口逻辑部分由FPGA实现,采用32 bit/33 MHz的PCI总线接口。

(2)电源电路

仿真设备采用PC提供的5 V直流供电,经过电压转换器件产生 FPGA+LLC+PHY所需的1.0 V电压和3.3 V电压。电压转换器选用LTC公司的LTM4616IV#PBF,该器件为两路输出,最大输出电流均为8 A。

(3)复位电路

仿真设备支持两种复位,分别是上电复位和总线复位。FPGA、三路链路层的上电复位和三路物理层的上电复位相互独立均采用 RC上电消抖复位,复位延时为10 ms;主机总线复位信号来自主机接口的复位输出,这两种复位信号均引入FPGA。

(4)时钟电路

49.152 MHz的晶体提供给仿真设备的1394B总线协议芯片,50 MHz晶振作为FPGA的本板晶振,该时钟在FPGA内部作为调度时钟,避免与1394接口时钟混用,便于逻辑分块实现。为了能够给晶振提供更稳定的电源,晶振电源输入端增加磁珠隔离,并添加滤波电容,晶振的1管脚将其上拉为高电平。

(5)1394接口电路

仿真设备中1394信号通过矩型连接器引出,9个端口分别采用 9根1394专用电缆引出,每根电缆的引线定义相同。同时1394总线信号采用变压器耦合方式,提供 Bilingual或Beta端口,端口模式可配置。1394总线信号通过矩型连接器插头转圆形连接器电缆引出到连接器上。

1.2 逻辑设计

仿真设备逻辑设计如图2所示,主要集成了主机接口和DMA模块、配置表模块、AS5643协议处理等模块。

图2 仿真设备处理流程示意图

其中主机接口主要负责填写 FPGA内部配置表内容、对 FPGA内部寄存器进行读写操作和中断操作,以及将链路层寄存器映射到主机接口的地址空间开放给主机访问;DMA模块负责主机主存与片外DPRAM之间的数据搬运。

配置表模块主要是用于存储总线发送接收配置表,配置表信息在初始化阶段由主机加载完成,在总线收发调度逻辑来时供逻辑查询调度,完成数据的匹配功能。

AS5643协议处理模块实现了主机与链路层接口设备之间的通信,满足基于IEEE-1394b的用法和需求建立的航空领域网络传输数据总线标准 SAE AS5643。FPGA逻辑配合软件实现了 AS5643总线网络协议定义的异步流包、固定帧速率、STOF包同步、带宽预分配、纵向奇偶校验 VPC、匿名签署消息、通道号的静态分配[2]、VPC与CRC错误注入、心跳字初始值自设定、数据收发控制、容错检测等功能。

子系统主机通过主机总线桥接口完成板卡资源的访问、板卡状态控制、状态信息读取,同时将节点配置表内容写入片内 DPRAM中,完成发送、接收、通信参数的配置功能,如图2线①所示。在数据处理方面,为了提高数据处理效率,设计中采用DMA方式完成数据搬运工作,发送数据时主机软件将待发送的数据按要求封装完成后,启动DMA控制器,将数据存入片外DPRAM中,在发送逻辑到来后完成数据组包及调度发送,如图2中线②所示;接收数据时,主机软件实时检测接收消息状态,在新的有效消息到来时,启动DMA控制器将数据从片外DPRAM搬运至主机内存,供主机软件处理,如图2线③所示。

1.3 软件设计

仿真设备软件的作用是让宿主机操作系统识别硬件设备,并且能够完成对硬件资源的访问,包括硬件资源初始化、硬件控制,以完成仿真设备正常通信功能。在进行软件设计时,采用分层设计的思想,每一层软件完成各自的功能,软件层次之间采用简单的接口进行交互,较低层次的软件为高一层的软件提供服务,如图3所示。应用软件为用户提供可视化界面,通过调用1394驱动软件来完成数据的发送;WDM驱动软件一方面与1394驱动软件完成数据及命令的交互,另一方面通过主机PCI能够直接访问AS5643逻辑。

图3 应用软件与1394驱动软件的调用关系

1.3.1 WDM驱动软件设计

WDM驱动软件主要提供了设备存储空间的读写访问、应用层事件挂接、接收例程数据初始化、获取数据等功能[3],同时在数据搬运时,为了提高软件的运行效率及健壮性,在程序的设计上尽可能地减少软件开销,将数据处理交由板卡逻辑进行处理,软件只进行状态监控及数据整理。

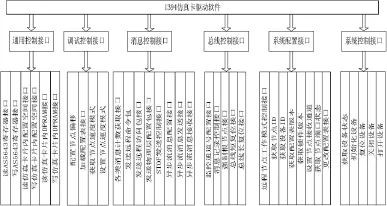

1.3.2 1394驱动软件设计

1394驱动软件使用 Win32标准 API接口来访问设备的硬件资源,完成主机端与 FPGA之间的数据交互,以函数接口的形式提供给上层应用程序使用,使应用层不必关心仿真设备硬件逻辑及数据流转的细节,只需要处理应用层数据的组织即可,其主要包括:通用控制接口、调试控制接口、消息控制接口、总线控制接口、系统配置接口、系统控制接口,具体如图4所示。

1.3.3 应用软件设计

仿真设备上层应用程序按照功能划分为配置表模块、状态监控模块、数据捕获模块、数据发送模块和拓扑显示模块,如图5所示。各功能模块如下:

(1)Commander(拓扑显示及控制):通过获取仿真设备链路层芯片在总线节点状态发生变动后产生的自标识包信息,解析出当前总线的连接拓扑关系并进行图形化显示,同时可发起总线长复位、短复位、复位风暴以及进行总线端口禁止、使能等;

(2)Monitor(状态监控):对当前仿真设备的状态信息进行实时监控,包括指定类型、指定速率数据包个数统计、错误包个数、总线复位次数统计、VPC错误统计、数据包负载错误统计等;

(3)Generator(数据发送):构造符合 AS5643协议的数据包的各个字段,发送给目的终端,用于测试总线数据的发送功能;

(4)Recorder(数据记录):将仿真设备接收到的数据包进行实时显示,并按照1394协议的标准形式进行协议解析及分析;

(5)Recvcfg(配置表模块):体现AS5643协议带宽预分配策略,节点的发送消息、接收消息、消息偏移等配置参数的生成及修改;

(6)TicLoad(加载维护):提供总线网络维护及节点配置表、逻辑文件远程管理功能。

图4 1394驱动软件

图5 应用软件

2 验证与测试

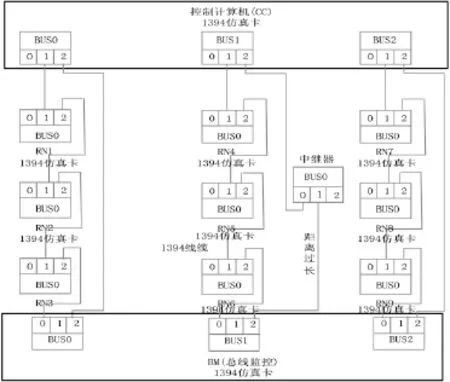

通过上述1394总线三节点仿真设备搭建地面验证测试系统环境,从拓扑构建、组网通信、总线容错、加载维护等方面进行产品功能及网络仿真验证,如图6所示,该演示环境由1个控制计算机、9个远程节点和1个监控维护模块组成基本的网络拓扑,每个功能模块均采用1394总线三节点仿真设备实现。

(1)拓扑构建

拓扑构建模块中对总线系统中的总线拓扑结构显示、节点状态、端口速率显示以及对各个端口进行禁止、使能、挂起等功能进行验证测试。

(2)组网通信

图6 地面验证测试系统示意图

组网通信模块中基于总线测试系统,在远程节点仿真中对其通道配置、配置加载、STOF包接收、数据偏移修改、异步流数据收发等功能进行验证测试;控制计算机中对其配置加载、STOF包的配置发送、异步流数据收发、节点同步等功能进行验证测试;总线监控中对其网络数据异步流包、STOF包以及总线复位的数据监控及数据过滤等功能进行测试;同时在该总线中加载完整的通信配置表进行总线模拟仿真测试。

(3)总线容错

总线容错测试中通过仿真设备进行数据错误故障注入以及总线竞争等异常总线通信功能测试。

(4)加载维护

加载维护测试中主要测试总线节点信息的管理及加载功能,测试包括:节点标识、节点网络状态以及进行远程节点配置表及逻辑文件加载测试。

基于上述总线仿真测试环境,分别对总线系统中的远程节点、控制计算机、监控节点的功能及性能进行全面有效的测试,同时通过在实验室组网模拟机载系统工作,并且接入到机载网络中模拟其中的总线控制节点。经过大量的试验及系统联试,结果表明仿真设备的功能、性能均满足试验验证需求。

3 结论

本文就1394总线三节点仿真设备的设计与实现技术进行了研究,从硬件、逻辑及软件等方面进行了分析。通过搭建1394总线地面仿真验证环境,实测设备的各项功能、性能指标,完成总线系统综合化仿真测试。

经大量试验验证表明,该产品相比于国内外同类产品集成度高,通用性强,在仿真应用中有效降低了实验成本,提高了验证效率,进而为在地面仿真环境下构建1394总线系统提供了强有力的保障,可以推动1394总线通信技术在机载系统中的应用,对于进一步研制和开发1394总线具有重要意义。

[1]张少峰,田泽,杨峰,等.基于 AS5643协议的Mil-1394仿真卡设计与实现[J].计算机技术与发展,2013,8(23):168-171.

[2]Society of Automotive Engineers.IEEE1394b interface requirements for military and aerospace vehicle applications[S]. SAE Aerropace Standard 5643,2004.

[3]张帆,史彩成.Windows驱动开发计数详解[M].北京:电子工业出版社,2008.

Design and implementation of1394 three-node simulation card

Xin Yongli1,2,Jin Weiping3,Jia Zhao3,Chen Feiru3

(1.AVIC Computing Technique Research Institute,Xi′an 710068,China;2.Aviation Key Laboratory of Science and Technology on Integrated Circuit and Micro-System Design,Xi′an 710068,China;3.Xi′an Xiangteng Microelectronics Technology CO.,LTD,Xi′an 710068,China)

It has high cost and risk to make a military1394 bus verifation test which is based on a airborne environment,as well as great limitations.It is deeply necessary to develop a corresponding ground simulation device for bus system of integrated simulation test.This paper combines the demand of1394 protocol in the military field developed a military1394 three-node simulation card.This device achieves integration design of the control computer,remote node,the bus monitoring and load maintenance,which makes data transceiver,configuration load,fault injection,communication monitoring,topology display,remote loading,and other functions into one.It can be used in the laboratory environment to build a complete military1394 bus communication system,and build the airborne subsystem device between the complicated situation of the internet.The completion of a comprehensive system bus simulation application test provides support and guarantee in the field of military.

Mil1394;simulation device;three-node

TP393

:ADOI:10.16157/j.issn.0258-7998.2016.06.005

辛永利,靳伟平,贾钊,等.1394总线三节点仿真设备设计与实现[J].电子技术应用,2016,42(6):17-20.

英文引用格式:Xin Yongli,Jin Weiping,Jia Zhao,et al.Design and implementation of1394 three-node simulation card[J].Application of Electronic Technique,2016,42(6):17-20.

2016-03-09)

辛永利(1969-),男,工程硕士,高级工程师,主要研究方向:计算机应用。

靳伟平(1989-),男,助理工程师,主要研究方向:嵌入式系统设计与开发。

贾钊(1989-),男,助理工程师,主要研究方向:嵌入式系统设计与开发。

陈飞茹(1991-),女,大专,主要研究方向:嵌入式系统设计与开发。

航空科学基金(2015ZC51036);中国航空工业集团公司创新基金(2010BD63111)