航电1394总线节点设计实现*

2016-03-18易宁宁魏艳艳

赵 彬,易宁宁,郑 斐,魏艳艳

(1.中航工业西安航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点实验室,陕西 西安 710068;3.西安翔腾微电子科技有限公司,陕西 西安 710068)

航电1394总线节点设计实现*

赵 彬1,2,易宁宁3,郑 斐1,2,魏艳艳1,2

(1.中航工业西安航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点实验室,陕西 西安 710068;3.西安翔腾微电子科技有限公司,陕西 西安 710068)

机载总线节点接口模块作为系统总线网络的接入节点,其功能性能的完备性、可靠性对于总线网络系统的构建有着至关重要的作用。1394总线作为新一代飞机航空电子系统的网络传输总线,其节点模块设计的重要性不言而喻,以1394总线协议为依据,结合总线系统的需求背景,设计了一种航电1394总线节点接口模块。该模块基于标准化、通用化的设计思想,提取用户共性需求,结合1394总线协议层次结构,确定最终的产品架构。总线节点功能设计中采用 CC/RN/BM一体化设计,提供 PCI/PCIE主机接口,支持 S100B/S200B/S400B可配置总线通信速率,设计灵活,为用户提供标准软硬件接口,有效降低了设计、维护成本。

1394总线;AS5643协议;航电1394总线节点

0 引言

1394总线主要由机载网络接口子卡连接组成,航电1394总线节点产品为主机使用1394网络通信服务提供软、硬件接口,完成主机设备与1394总线间的信息交互能力,实现对1394总线网络系统运行的集中管理、时统控制、网络结构维护和网络数据通信功能,满足任务系统对1394网络的需求。该节点采用标准化、通用化及软硬件协同的设计思路,由驱动软件和 FPGA逻辑共同实现SAE AS5643协议要求的CC、RN、BM一体化功能,提供PCI和PCIE两种主机接口,支持S100B/S200B/S400B总线通信速率,并通过电气特性验证及可靠性与环境试验验证,满足高可靠性机载环境使用的需求。

本文从硬件、逻辑构架和软件三方面详细介绍了航电1394总线节点的设计与实现过程,并通过网络验证平台对节点功能、性能进行验证。

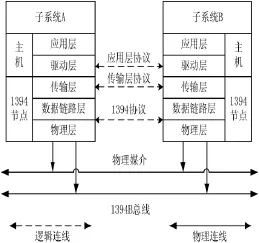

1 节点设计

航电1394总线节点作为接入总线系统中的通用1394通信模块,具备航电系统CC/RN/BM角色,实现1394总线网络的控制、数据传输等功能。其设计遵循航空电子通信系统的层次结构划分(见图1),实现了系统物理层、数据链路层、传输层和驱动层的功能,其中,物理层与数据链路层由硬件实现,传输层(AS5643协议)通过可编程逻辑实现,应用软件和驱动软件驻留在上位机中,应用软件与特定的子系统有关,通过调用驱动软件实现子系统功能要求。

图1 Mil-1394通信系统层次结构

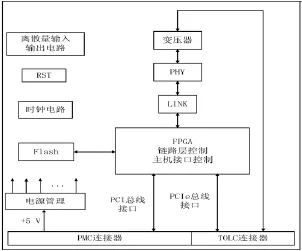

1.1 硬件设计

航电1394总线节点硬件设计采用标准化、通用化及软硬件协同的设计思路,实现了CC/RN/BM功能统一设计,提供标准 PCI及 PCIE主机接口,具有1394总线AS5643协议解析、1394电气信号驱动和消息存储功能。其主要硬件结构设计如图2所示。

图2 硬件结构示意图

节点设计采用FPGA逻辑实现 AS5643协议处理功能,完成应用系统与主机接口连接。其中1394接口信号经过变压器耦合方式输出,每个节点对外提供 3个端口,端口符合 IEEE1394B规范要求,支持 S100、S200和S400 3种传输速率;1394链路层功能和1394物理层功能分别由符合协议规范的接口集成电路实现;提供4路离散量输出信号和4路离散量输入信号,用于抢权控制和功能扩展;配置1片 4 Mbit Flash存储器,用于存储总线配置表[1]。

各主要模块功能如下:

(1)主机接口电路模块:主机接口可以采用32 bit/33 MHz工作方式PCI接口;也可以提供兼容PCIe1.1的1x规格、高速2.5 Gb/s接口。采用主机提供的二级直流电源(+5 V),经过电压转换器件产生 3.3 V、2.5 V、1.8 V、1.2 V、1 V等各种电压,满足不同功能电路使用。

(2)时钟电路模块:主要由FPGA时钟使用单端输出的30 MHz晶振提供,便于逻辑功能分区实现。1394物理层时钟按照协议规范,可选晶振或晶体提供49.152 MHz时钟信号输入。

(3)复位电路模块:复位电路可根据实际的复位时间要求进行选择,节点设计包含两个复位:复位一为确保FPGA逻辑加载在全局复位结束前完成,采用监控芯片实现电压控制和复位输出;复位二为满足单一复位时间要求,采用 RC复位电路与施密特反相器配合消抖实现总线物理层接口复位。

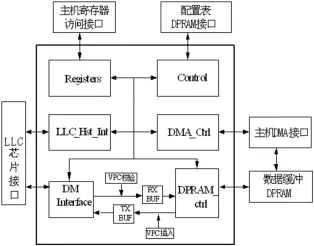

1.2 逻辑设计

FPGA逻辑结构设计主要集成了主机接口模块和AS5643协议处理模块两部分,其功能框图如图3所示[2]。主机接口模块是主机与AS5643协议处理模块进行数据交互的接口,实现主机对AS5643协议处理模块所有资源的访问。

图3 AS5643协议处理模块功能框图

AS5643协议处理单元模块是 FPGA逻辑设计的主要实现单元,该模块采用 CC/RN/BM节点一体化设计,完成主机与链路层接口芯片之间的通信, 实现了AS5643协议定义的总线同步、总线通信、总线系统容错等关键技术,支持 S100B、S200B或S400B模式通信。

FPGA逻辑结构采用共享主机存储工作方式,具备DMA引擎,实现数据在FPGA双口与主机RAM之间的高速搬移;提供片内DPRAM存储配置表信息,最大支持收发各128条消息,根据总线配置表进行消息调度;消息负载长度可配置,S100B模式下支持最大 512 B,S400B模式下最大 2 KB。

1.3 软件设计

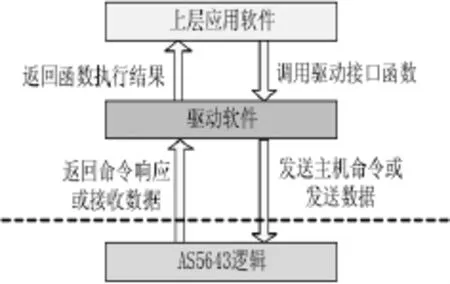

节点软件由应用软件和驱动软件组成。驱动软件主要完成主机端与1394节点之间的数据交互,是主机应用层与AS5643逻辑的中间层,提供API接口函数给上层应用调用,将应用层和硬件与逻辑之间的交互分开[3]。上层应用软件与特定的子系统有关,应用软件通过调用驱动软件实现节点功能。软件体系结构如图4所示。

图4 软件设计的体系结构关系图

驱动软件作为主机访问1394接口子卡硬件资源和数据收发的接口,主要实现1394B总线数据通信和网络管理,可提供对1394节点内程序的调度,对1394节点状态的报告等处理,由主机应用层软件进行调用。软件采用CC/RN/BM节点功能兼容设计,支持VxWorks、ACoreOS、ACoreOS653等多种操作系统环境。

驱动软件按功能模块分为设备管理模块、消息控制模块、网络管理模块、时统管理模块和中断处理模块等,如图5所示。

图5 驱动软件接口

节点软件实现首先完成主机接口初始化,实现板卡资源的访问、状态及信息的控制与读取。其次上层应用软件通过调用驱动软件实现1394节点功能,包括按照系统需求设置节点角色、网络工作模式及加载系统配置表进行逻辑内部寄存器配置等来完成正常的网络管理及数据通信。即 CC节点能够正确获取网络控制权,处理网络节点状态,发布网络时间,发送和接收异步流消息;RN节点能够发送上下网请求,获取网络时钟,发送和接收异步流消息[4]。软件流程如图6所示。

2 技术优势

与其他总线节点相比,该设计实现的总线节点主要技术优点如下:

(1)提出了 PCI/PCIE接口复用设计电路,满足多种主机接口需求;

(2)产品功耗较低(不大于 6 W),体积小(68mm×68mm),重量轻(不超过 60 g),可靠性高,使得产品应用范围更广,满足机载及地面环境下的多重应用需求;

(3)针对机载总线传输高可靠要求,按照S100B、S200B、S400速率下的电气特性指标,完成1394接口物理层信号完整性分析、设计及验证,有效地提高了总线信号传输质量,保障了数据传输可靠性;

(4)实现按照预分配的偏移时刻定时发送的事件消息,实现 Mil-1394总线网络管理、网络时统以及流数据传输的方法及电路;

(5)为提高产品的应用灵活性,在软件、逻辑、硬件设计中首次采用CC/RN/BM一体化设计;

(6)设计实现了一种支持总线多节点的总线配置表结构和加载方案,满足机载产品在线加载的应用要求;

(7)从总线系统、总线信号质量和线缆/连接器测试三方面构建总线验证系统,进行网络通信测试、产品电气特性测试以及线缆连接器测试。

图6 节点软件流程

3 测试及验证

航电1394总线节点测试主要针对板卡性能和功能进行测试,以保证该节点设计满足协议功能需求和高可靠性、实时性的性能要求。

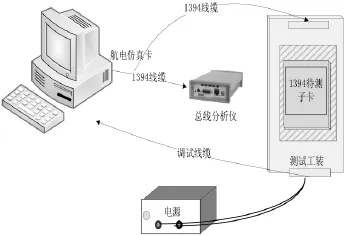

验证环境由航电1394总线节点测试系统、1394航电仿真卡测试系统、连接线缆等组成,其中1394总线分析仪作为监控节点接入测试网络。图7为一个简易的验证环境连接图。

图7 验证环境连接图

针对Mil-1394总线对总线信号质量的要求,进行了环境试验下的总线电气特性测试和可靠性试验等测试,保证其在恶劣复杂工作环境下的正常通信。该测试保证了总线信号传输质量,保障数据传输的可靠性。

功能测试通过搭建1394航电仿真卡与待测试子卡进行点对点测试,以及在验证环境中加入多个待测子卡,组成网络测试1394总线系统通信功能是否正常。主要测试待测子卡是否满足 AS5643协议的需求,包括STOF包发送/接收、总线网络管理、时统管理、异步流消息的发送/接收、总线配置表文件加载、总线故障注入等。经验证,1394总线节点能够实现航电系统1394总线节点功能,并且通过1394总线协议分析仪监控结果分析得知功能正常。

4 结论

本文就航电1394总线节点的设计及实现技术进行研究,从硬件架构、逻辑设计及软件实现等方面进行了分析。经1394总线验证平台实测,结果表明该航电1394总线节点实时性强、准确性高、性能稳定,并通过国军标软件工程化标准测试,可为各类机载安全关键和任务关键子系统提供高可靠、高确定、高带宽的系统级总线接口,并为相关产品开发提供设计思路和实践经验。

[1]张大朴,王晓,张大力,等.IEEE1394协议及接口设计[M].西安:西安电子科技大学出版社,2004.

[2]赵彬,田泽,杨峰,等.基于 AS5643协议的接口模块设计与实现[J].计算机技术与发展,2013,23(8):100-102.

[3]冯莎,卢选民,王兴亮.一种基于 SAE AS5643总线协议的驱动程序设计[J].测控技术,2013,31(10):98-100.

[4]张少峰,田泽,杨峰,等.基于 AS5643协议的 Mil-1394仿真卡设计与实现[J].计算机技术与发展,2013(8):168-171.

Design and implementation of avionics1394 node

Zhao Bin1,2,Yi Ningning3,Zheng Fei1,2,Wei Yanyan1,2

(1.AVIC Computing Technique Research Institute,Xi′an 710068,China;2.Aviation Key Laboratory of Science and Technology on Integrated Circuit and Micro-System Design,Xi′an 710068,China;3.Xi′an Xiangteng Microelectronics Technology CO.,LTD,Xi′an 710068,China)

Airborne bus node interface module as system bus network access nodes,its performance of completeness and reliability has the vital function for bus network system construction.1394 bus as a new generation of aircraft avionics bus network transmission,the importance of the node module design is obvious.The paper combines protocol with demand of bus system background,and designs a kind of avionics bus1394 node interface module.This node module is based on standardization and generalization design, extracts the user demand,and is combined with1394 protocol hierarchy to make the final product architecture.Founction in the design of bus nodes using CCRNBM integration design,providing PCIPCIE host interface,supporting S100S200S400 configurable bus communication speed,and flexible design to provide users with software and hardware interface standard,which effectively reduce the design and maintenance costs.

Mil1394;AS5643;Mil-1394 node

TP393

:ADOI:10.16157/j.issn.0258-7998.2016.06.004

赵彬,易宁宁,郑斐,等.航电1394总线节点设计实现[J].电子技术应用,2016,42(6):13-16.

英文引用格式:Zhao Bin,Yi Ningning,Zheng Fei,et al.Design and implementation of avionics1394 node[J].Application of Electronic Technique,2016,42(6):13-16.

2016-03-09)

赵彬(1985-),男,硕士,工程师,主要研究方向:集成电路设计、嵌入式软件开发。

易宁宁(1989-),女,助理工程师,主要研究方向:嵌入式软件设计与开发。

郑斐(1986-),男,硕士,工程师,主要研究方向:数字集成电路设计和验证。

魏艳艳(1986-),女,硕士,工程师,主要研究方向:数字集成电路设计和验证。

航空科学基金(2015ZC51036);中国航空工业集团公司创新基金(2010BD63111)