图形处理系统中主机接口设计及应用

2016-02-24马超,王婷,田泽,王静

马 超,王 婷,田 泽,王 静

(1.中国航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点试验室,陕西 西安 710068;3.西安现代控制技术研究所,陕西 西安 710065)

图形处理系统中主机接口设计及应用

马 超1,2,王 婷1,2,田 泽1,2,王 静3

(1.中国航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点试验室,陕西 西安 710068;3.西安现代控制技术研究所,陕西 西安 710065)

图形处理技术被广泛应用于电影、视频、游戏以及动画的制作等领域,而图形处理系统(GPU)的出现极大地增加了SoC设计及验证的复杂度。作为SoC对外的总线接口,PCI主机接口的设计实现的难度也随之增加,并成为图形处理SoC设计过程中的功能、性能以及进度保证的瓶颈。PCI主机接口结构设计是否合理则会直接影响到图形处理SoC的功能、性能以及进度的关键因素之一。文中阐述了一种基于图形处理系统应用的主机接口架构。从图形处理系统设计角度,提出了总线架构下主机接口的设计,实现了图形处理系统通过总线与CPU之间的交互,完成了主机通过配置通路对图形处理系统的中断控制以及主机通过调试通路加载命令解析程序等功能。在系统设计阶段,有效提高了准确性和验证的完备性。

图形处理系统;主机接口;调试通路;配置通路

0 引 言

GPU系统的不断发展使得计算机系统复杂度急速增加,前期设计测试验证的难度也随之增大[1-2]。

主机接口在GPU中的应用,对GPU整体的功能、性能的提高起到了关键性的作用。对于GPU内部而言,其内部处理单元众多,各个处理单元之间数据交互同样异常复杂[3-4]。

主机接口作为图形处理系统的外部接口,通过总线完成与外部处理器的通信功能[5]。实现客户端与图形处理系统间的OpenGL命令传输,以及模板、纹理等图形数据的传输。另外,外部主机通过主机接口对图形处理系统进行配置,从而实现图形处理功能[6]。

1 主机接口设计

主机接口实现OpenGL命令和图形数据的传输。实现主机对图形处理系统内部体系结构寄存器的配置;PCI核后端逻辑与图形处理器IP核流水线各级的接口关系,实现了二者之间的数据传输。最终完成外围设备与PCI总线的连接,在CPU与图形处理系统之间建立了快速通信链路,完成图形处理系统中用户可访问寄存器的配置及CPU与图形处理系统之间大批量数据传输等功能[7-8]。

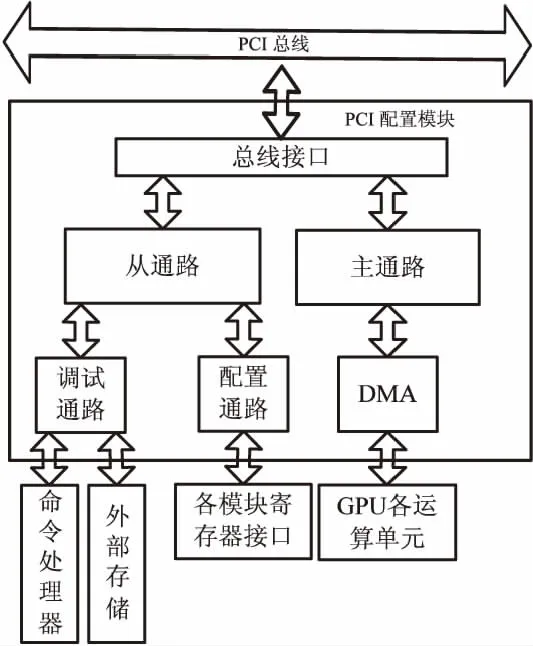

主机接口架构如图1所示。

图1 主机接口架构图

2 主机接口从通道设计

2.1 配置通路设计

配置通路实现PCI总线对图形处理系统寄存器的读写访问[9]。根据各个模块的不同时钟实现异步时钟同步处理。配置通路架构如图2所示。

图2 配置通路架构图

配置通路包括地址译码、时钟同步以及寄存器实现。

主机发起寄存器访问操作,经过地址译码将寄存器访问控制信号、数据及地址由总线时钟同步到相应时钟域,并输出至图形处理系统各个模块的寄存器接口[10]。

图形处理系统的控制寄存器也在配置通路内完成,这部分控制寄存器实现了图形处理系统与总线的中断机制以及基本控制功能。

2.2 调试通路设计

2.2.1 概 述

调试通路实现外部主机对图形处理系统中命令处理单元和存储管理与控制单元的数据读写访问[11]。

调试通路架构如图3所示。

图3 调试通路架构

2.2.2 命令处理器通路设计

外部主机通过调试通路命令处理器通路将命令处理单元解析OpenGL命令所需的汇编指令写入命令处理单元内部缓存中,为避免访问命令处理器与访问存储管理控制通路冲突,添加使能命令通路寄存器,以保证访问命令处理器与访问存储管理与控制通路相互独立,避免了测试及应用中因通路互相影响引起功能问题。

访问命令处理器通路时,支持主机单拍及Burst操作,在上电复位撤销后,由主机加载命令解析程序,用来判断、透传OpenGL命令[12]。

2.2.3 存储管理与控制通路设计

主机通过调试通路通过存储控制与管理单元对外部存储进行读写操作[13]。

主机访问存储管理与控制单元,由于作为调试通路,对存储管理与控制单元而言,主机操作在其内部仲裁时优先级最低;所以为保证主机能够正常对高速DDR进行读写操作,达到调试目的,在主机接口后端逻辑设计中需对读操作进行独立控制,以满足主机发起读写操作时存储管理与控制单元暂时未能正常响应的条件[14]。

3 主设备通道设计

图形处理系统通过主设备通路在命令处理单元和DMA控制单元之间建立快速数据传输链路,将绘图命令和绘图数据从外部主设备传输至图形处理系统内部,完成快速数据传输功能。

命令处理单元与DMA控制单元分别作为主设备请求总线时,完成主机端与图形处理系统之间的大批量数据传输。

命令处理单元与DMA控制单元同时作为主设备时占用PCI总线的数据通路选择功能。

主设备通路架构如图4所示。

图4 主设备通路架构图

4 结 论

通过文中所述PCI主机接口的架构设计,对GPU系统的设计验证工作提出如下两点:

(1)将针对GPU内部各个运算单元的异步时钟同步处理统一由PCI主机接口配置通路完成,在一定程度上保证了主机接口与GPU各个运算单元之间的寄存器接口保持了结构上的统一,有效减少了后端设计、后仿真阶段的工作量。

(2)调试通路的应用使得主机能够在设计初期完成对外部存储资源的验证。同样,增加的由主机直接读写命令寄存器命令加载通路,能够允许主机以更灵活地将命令处理单元解析OpenGL命令所需的汇编指令写入命令处理单元内部缓存中,在功能验证的源头

保证了命令解析的正确性,同时也增强了自主验证的灵活性。

5 结束语

综上所示,基于总线接口架构的图形处理系统,通过主机接口设计,将跨时钟域统一处理,减轻了图形处理系统各个逻辑运算单元的复杂度。通过调试通路的设计,主机能够更加自由地加载命令解析程序,增加调试的灵活度。在系统设计初期能够较完备地对图形处理系统OpenGL命令的支持度进行验证,访问DDR能够最大限度地保证图形处理系统与DDR之间的数据可见性,便于前期调试以及后期芯片的测试。

[1] 蔡士杰,宋继强,蔡 敏.计算机图形学[M].第3版.北京:电子工业出版社,2007:10-21.

[2] 刘 鑫,许华荣.基于GPU的特征点提取与匹配算法比较[J].计算机辅助设计与图形学学报,2013,25(10):1496-1502.

[3] Wolf W. High performance embedded computing architectures,applications,and methodologies[M].New York:Elsevier,2007.

[4] 徐新海,林宇裴,易 伟.CPU-GPGPU异构体系结构相关技术综述[J].计算机工程与科学,2009,31(A1):24-26.

[5] PCI local bus specification revision 2.3[S].[s.l.]:[s.n.],2001.

[6] 马安国,成 玉,唐遇星,等.GPU异构系统中的存储层次和负载均衡策略研究[J].国防科技大学学报,2009,31(5):38-43.

[7] 王 鹏,伊 鹏,金德鹏,等.基于三级存储阵列缓存高速数据包及性能分析[J].软件学报,2005,16(12):2181-2189.

[8] Wolberg G.Digital image warping[M].Los Alamitos California:IEEE Computer Society Press,1990:208-209.

[9] Danielsson P E,Hammerin M.High accuracy rotation of images[J].CVGIP,1992,54(4):340-344.

[10] 刘海华,陈心浩.异步非透明PCI-PCI桥的应用研究[J].微计算机应用,2006,27(4):478-480.

[11] 张立倩,白凤山.基于PCI总线的数据传输系统设计[J].内蒙古大学学报:自然科学版,2005,36(1):84-88.

[12] 张伟栋,王国庆,崔红利.一种基于IP内核的PCI总线接口设计方法研究[J].航空计算技术,2008,38(5):115-118.

[13] 贾 真,林 清.PCI总线应用设计与研究[J].现代电子技术,2008,31(10):85-87.

[14] 柳 钰,梅策香,吴继侠.PCI总线从设备控制器的设计与实现[J].微计算机信息,2009,25(7-2):278-280.

Design and Application of Host Interface in Graphic Processing System

MA Chao1,2,WANG Ting1,2,TIAN Ze1,2,WANG Jing3

(1.Aeronautics Computing Technique Research Institute,Xi’an 710068,China;2.Aeronautics Science and Technology Key Laboratory of Integrate Circuit and Micro-system Design,Xi’an 710068,China;3.Xi’an Modern Control Technology Research Institute,Xi’an 710065,China)

Graphic processing techniques has been implemented in movie,video,game and cartoon industry.The implementation of Graphic Processing Unit (GPU) would hugely lead the design and verification of SoC to be more complex.As the only interface of GPU system,the design and implementation of PCI bus would also be paid more attention as it could be considered as the key point in improving the function,performance and project schedule guarantee.A structure of host interface based on graphic processing system application is proposed.According to the method,the data interactive between CPU and GPU via PCI Bus would be achieved.The function of interrupt controlling via configuration-channel and loading CMD program via debug-channel would also been achieved.This would enhance the completeness in verification and veracity in design.

graphic processing unit;host interface;debug channel;configuration channel

2015-06-16

2015-09-22

时间:2016-05-05

中国航空工业集团公司创新基金(2010BD63111)

马 超(1984-),男,工程师,研究方向为集成电路设计与验证;田 泽,博士,研究员,中航首席技术专家,研究方向为SoC设计、嵌入式系统设计、VLSI设计。

http://www.cnki.net/kcms/detail/61.1450.TP.20160505.0814.006.html

TP39

A

1673-629X(2016)05-0125-03

10.3969/j.issn.1673-629X.2016.05.026