用于神经信号采集的高PSRR及CMRR植入式模拟前端*

2015-12-19吴朝晖谢宇智赵明剑李斌

吴朝晖 谢宇智 赵明剑 李斌

(华南理工大学 电子与信息学院, 广东 广州510640)

神经信号采集芯片内的模拟前端用于对神经信号的采集、放大,其设计对信号的提取精度及抗干扰能力有较大的影响,是植入式神经信号采集芯片的关键组成模块.目前,先进的植入式微系统一般通过体外和体内的线圈,采用电磁感应的方式给体内的电路模块供电[1-2].此供电方式会产生较大的电源噪声干扰,因此体内电路系统应具有良好的电源抑制比(PSRR).此外,生物体是个充满噪声的环境,电极附近受刺激的肌肉产生的电信号有时会比所需要的神经信号大几个数量级[3],由此产生很大的共模干扰.因此,植入式模拟前端需要有很高的共模抑制比(CMRR).

神经信号为低频微弱信号,其幅值分布范围为10~500μV,频率分布范围为200 Hz ~10 kHz,因此,电路中的低频噪声对生物信号的采集产生较大的干扰.对于CMOS 工艺来说,主要通过增大器件尺寸或使用斩波调制技术来实现对低频噪声的抑制[4-5].通过加大器件面积来抑制噪声会增加模拟前端的面积,而采用斩波调制技术不会引入过大的面积消耗,因此比前者更适用于植入式的应用.然而,采用斩波调制技术后,电路的失调电压会由于受到调制而在电路的输出端形成纹波,对信号采集造成严重的干扰.目前,抑制斩波调制技术引起的输出纹波的方法有低通滤波、自动调零技术、添加纹波抑制环路等,其中自动调零技术和纹波抑制环路对纹波的抑制效果较好.自动调零技术会引起噪声折叠,增加电路的低频噪声[5].现有纹波抑制环路有的通过积分器来降低输出纹波[6-7],有的通过电流数模转换器(DAC)来抑制输出纹波[8],前者需要大尺寸的电容,不适用于多通道的植入式生物信号采集系统,而后者用于全差分放大器中会引起电流不平衡.

文中研究与设计的模拟前端包括前置放大器、低通滤波器、可变增益放大器和基准电流源等模块.为确保具有较好的CMRR 和PSRR 性能,该模拟前端采用全差分结构设计,其中的前置放大器采用斩波调制技术来抑制电路中的低频噪声,并通过带电流DAC 的纹波抑制环路来抑制输出纹波.带电流DAC 的纹波抑制环路用在全差分放大器中会引起电流不平衡,导致晶体管进入线性区.为此,文中通过在纹波抑制环路中加入共模反馈调节模块来确保晶体管工作在饱和区,避免电流不平衡.

1 系统设计

文中设计的模拟前端系统框架如图1所示,它包含3 级电路.第1 级为前置放大器,采用了电容耦合-反馈结构[9-11]斩波放大器,一方面隔绝了由传感电极引入的直流失调电压,另一方面有效抑制了电路中的低频噪声.此外,为提高前置放大器的性能,加入了带电流DAC 的纹波抑制环路来抑制放大器的输出纹波,以及采用正反馈环路来提高放大器的输入阻抗.第2 级为低通滤波器,用于抑制输出信号带宽,防止由于模数转换器(ADC)采样引起的信号混叠.第3 级为可变增益放大器,用于增加模拟前端的动态范围,以满足采集不同幅值等级的生理信号的需求.此外,系统还包括基准电流源及偏置电路等模块.

图1 植入式模拟前端系统框图Fig.1 System block diagram of the proposed implantable analog front-end

2 电路设计

2.1 前置放大器

前置放大器的结构如图2所示,其核心电路为电容耦合-反馈斩波放大器.此外,前置放大器还包含带电流DAC 的纹波抑制环路以及输入阻抗提高环路.

前置放大器的增益为反馈电容和输入电容的比值Cfb/Cin,文中设计的前置放大器增益为40 dB,其中输入电容Cin=20 pF,反馈电容Cfb=0.2 pF.反馈电容Cfb与电阻RMOS并联形成了一个低频的高通极点,用于隔绝电极的直流失调电压.RMOS由两个背靠背的二极管连接的MOS 管构成,MOS 管工作在亚阈值区,实现了GΩ 数量级的阻值.除了形成高通极点外,RMOS还为主运放输入端提供直流偏置.

图2 前置放大器结构Fig.2 Architecture of the preamplifier

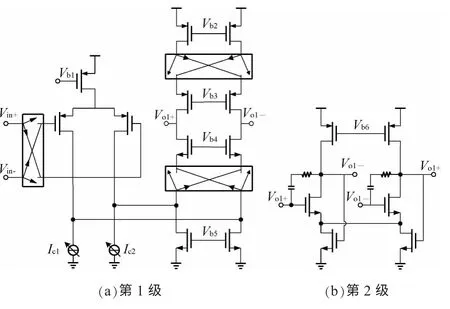

前置放大器中的主运放为斩波放大器,其原理如图3所示.斩波放大器采用两级运放结构,第1 级采用折叠式共源共栅放大器作为增益级,第2 级采用共源放大器作为输出级.其中第1 级加入了斩波调制器,将电路中的低频噪声调制到斩波频率处,从而有效地抑制低频噪声.

图3 斩波放大器原理图Fig.3 Schematic diagram of chopper amplifier

放大器中的噪声主要由MOS 管的热噪声和闪烁噪声构成.闪烁噪声主要通过斩波调制技术来抑制,而热噪声则通过增大主运放输入对管跨导与其他MOS 管跨导的比值来抑制.在相同的偏置电流下,偏置在弱反型层的MOS 管跨导比偏置在强反型层的MOS 管跨导要大,因此输入对管偏置在弱反型层.此外,由于PMOS 管的闪烁噪声系数比NMOS 管小,因此主运放的输入对管采用PMOS 管.

采用斩波调制技术后,运放的失调会在运放的输出端以纹波的形式出现.为了抑制输出纹波,在前置放大器中加入了带电流DAC 的纹波抑制环路,其结构如图4所示,它由比较器、SAR 逻辑以及7 位的电流DAC 构成.初始状态下,在斩波时钟信号的正半周期,比较器对运放的输出电平以及参考电平Vcm进行比较,SAR 逻辑根据比较结果调节电流DAC 的输出电流.经过电流DAC 校正后,静态下放大器的输出电平将接近于参考电平Vcm,从而抑制输出纹波.通过引入参考电平Vcm与输出电平进行对比,引入了共模反馈机制,在抑制输出纹波的同时避免了MOS 管由于电流不平衡而进入线性区.

图4 带电流DAC 的纹波抑制环路Fig.4 Ripple reduction loop with current DAC

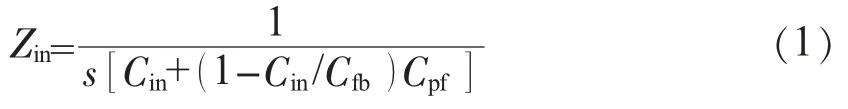

为避免由传感电极内阻引起的信号衰减,前置放大器需要有很大的输入阻抗.通过电容Cpf以正反馈的形式连接放大器的输入、输出端,如图2所示,可有效地增大前置放大器的输入阻抗.前置放大器的输入阻抗为

取电容Cpf=Cfb=0.2 pf,则输入阻抗为1/(sCpf).在没有输入阻抗提高环路的情况下,放大器的输入阻抗为1/(sCin).因此,加入输入阻抗提高环路可使输入阻抗提高100 倍.

2.2 低通滤波器

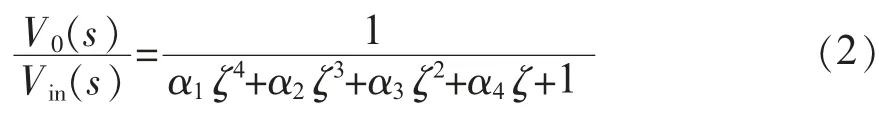

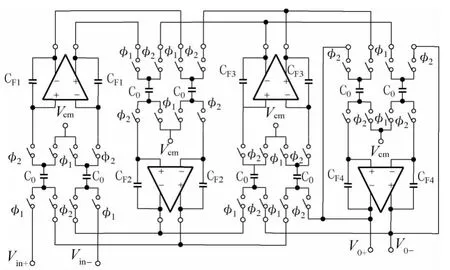

开关电容滤波器无需片外元件即可实现很大的时间常数,因此比RC 有源滤波器更适用于低频的生理信号滤波.文中采用的四阶全差分开关电容低通滤波器结构如图5所示.它由3 个开关电容积分器和1 个一阶开关电容低通滤波器通过首尾相连的方式构成,模拟了1 个四阶的RLC 低通滤波器.

滤波器的传输函数为

式中,ζ=sT,T 为开关时钟周期,α1=CF1CF2CF3CF4/C40,α2=CF1CF2CF3/C30,α3=CF1CF2/C20+CF1CF4/C20+CF3CF4/C20,α4=CF1/C0+CF3/C0.

由式(2)可知,开关电容滤波器的传输特性由电容比例及开关时钟周期决定,具有精度高、截止频率可调节的优点.文中设计的开关电容低通滤波器采用两路周期为1 MHz 的不交叠时钟进行驱动,实现了10 kHz 的低通截止频率.

图5 全差分四阶开关电容低通滤波器结构Fig.5 Architecture of fully differential fourth-order low pass switch capacitor filter

2.3 可变增益放大器

可变增益放大器用于增大模拟前端的动态范围,以满足神经信号幅值分布范围内的放大需求.文中设计的可变增益放大器采用全差分电阻比例放大器结构,如图6所示.增益由电阻比例来确定,通过改变反馈电阻的阻值来改变电阻比例,从而实现增益的改变.反馈电阻由多个不同阻值的电阻串联而成,通过控制与不同电阻组合并联的开关即可实现增益的调节.该可变增益放大器实现了4 种增益(6、12、20、26 dB),通过与前置放大器级联实现了4种可调增益(46.35、52.18、60.02、65.95 dB).此外,当可变增益放大器的增益变小时,其带宽也会随之增加.为了限制放大器的带宽,放大器的反馈电阻并联上1 个可变的电容,根据不同的增益调节电容值使得带宽保持不变.该结构通过采用电阻和电容复用的方法来降低电路的面积.

图6 可变增益放大器结构Fig.6 Architecture of the variable gain amplifier

2.4 偏置电路

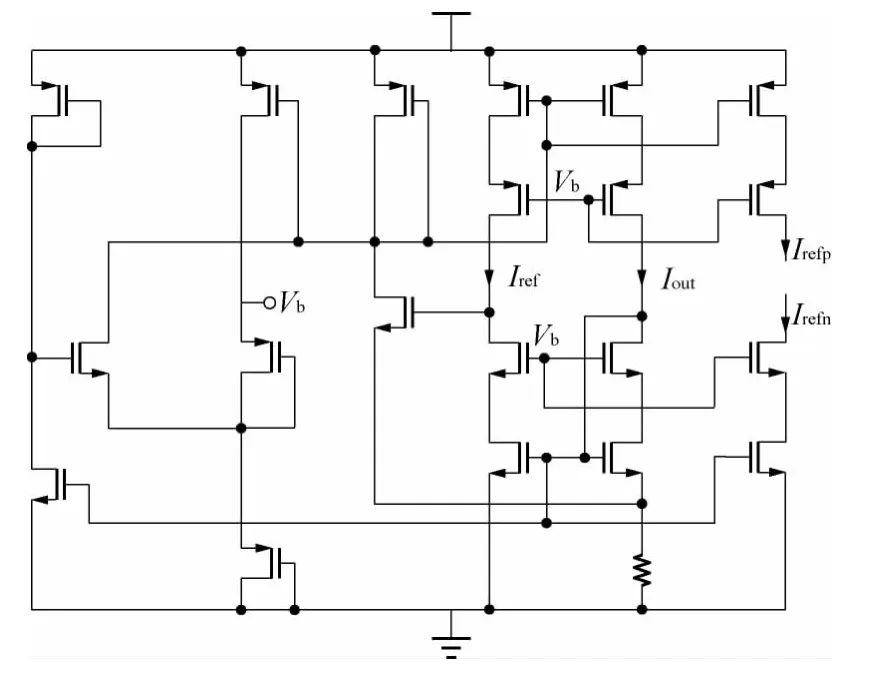

为系统提供偏置电流的基准电流源如图7所示.它采用了三支路共源共栅基准电流源结构,通过共源共栅结构来减小沟道长度调制效应以及负反馈环路来减少输出基准电流随电源电压的变化[12].

图7 三支路共源共栅基准电流源Fig.7 Three branches cascade current reference

3 性能仿真结果

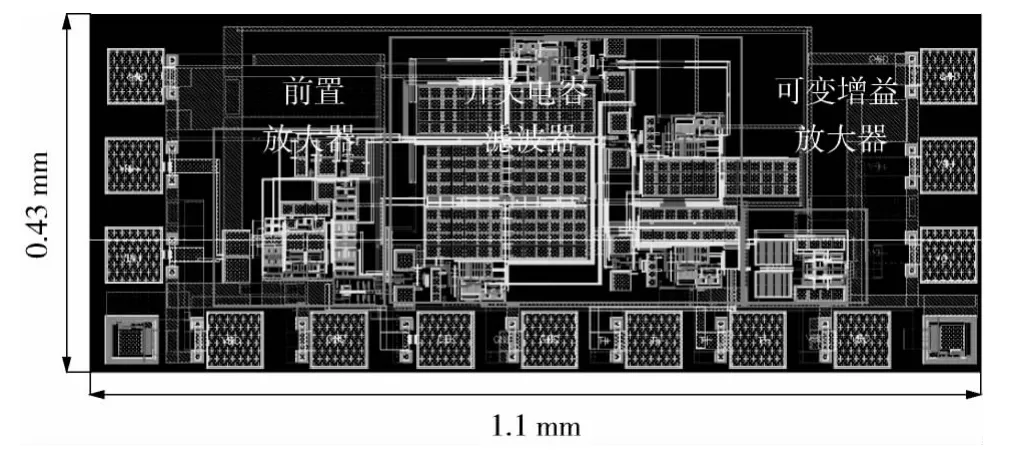

文中提出的用于神经信号采集的植入式模拟前端采用0.18 μm CMOS 工艺进行物理验证,芯片的总面积为0.473 mm2,版图如图8所示.

图8 模拟前端芯片版图Fig.8 Layout of the analog front-end chip

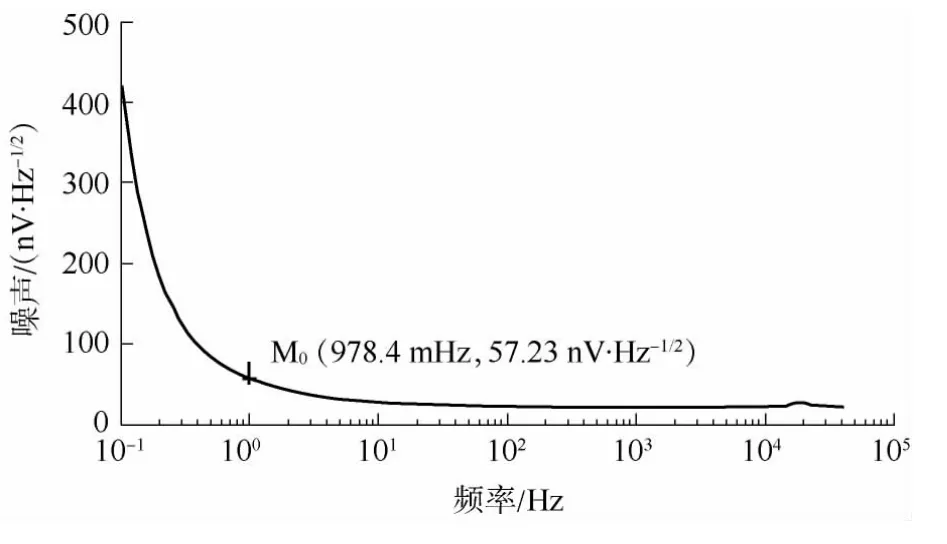

对所设计的模拟前端进行版图后仿真,其等效输入噪声谱如图9所示.在0.1 Hz~10 kHz 频率范围内对噪声进行积分,可得到该频率范围内的等效输入噪声为2.59 μV.

图9 等效输入噪声谱仿真结果Fig.9 Simulated result of equivalent input noise spectrum

模拟前端的传输特性曲线如图10所示.其低频高通截止频率为0.6 Hz,高频低通截止频率为9.7 kHz,实现了4 种可调增益(46.35、52.18、60.02、65.95dB).

图10 传输特性仿真结果Fig.10 Simulated results of transfer characteristic

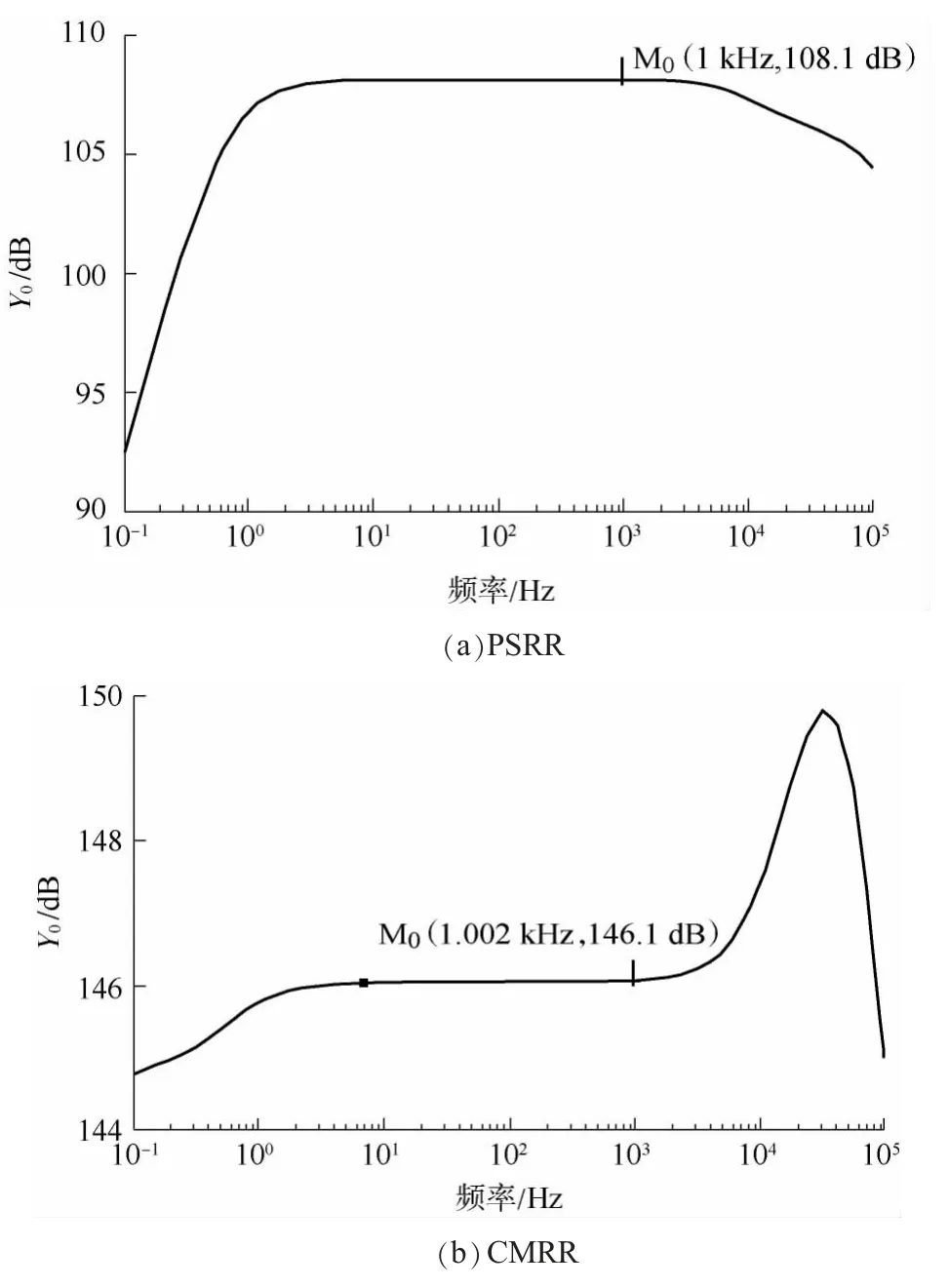

在65.95 dB 的增益下,对模拟前端芯片进行PSRR 和CMRR 仿真,结果如图11所示,通频带处的PSRR 为108dB,CMRR 为146dB.

图11 模拟前端芯片的PSRR 和CMRR 仿真结果Fig.11 Simulated results of PSRR and CMRR of the analog front-end chip

表1给出了文中设计的模拟前端性能与现有文献的对比情况.文献[13]中设计了一款100 通道神经信号采集系统,其中的模拟前端具有较好的噪声性能,所占用面积较小,但其CMRR 及PSRR 比较低,实际应用时抗干扰能力较差.文献[14]中的设计采用0.8 V 供电,由此获得较低的功耗,但其低功耗是以较大的噪声为代价.文献[15]中的设计具有噪声低、CMRR 高的优点,但其芯片面积较大,且通频带较窄,处理信号频率适应性受限.综合比较可知,文中设计的模拟前端具有较低的噪声以及较高的PSRR 和CMRR.

表1 文中设计的模拟前端性能与现有文献对比1)Table1 Comparison of performance between the proposed analog front-end and the references

相比其他文献,文中所设计的模拟前端功耗相对较大.因为植入生物体内的器件一般采用电池供电或采用无线能量传输进行供电,若模拟前端功耗较大,会影响植入生物体内的器件整体使用时间,使它在植入式微电极阵列应用中受到一定限制.本设计模拟前端的后一级为ADC.为了适应多通道生物信号采集的需要,笔者所在课题组所采用的ADC的采样频率比较低.为防止后级ADC 采样引起信号混叠,模拟前端要求有比较好的信号带宽外抑制能力,故文中设计的开关电容滤波器采用了四阶结构,使得模拟前端整体功耗及面积较大.若后级ADC 能采用较高的采样频率,则其对前级模拟前端的带外抑制能力的要求会降低,这时可以采用较低阶数的开关滤波器,从而使模拟前端的功耗及面积得到较好的改善.

4 应用结果

将所设计的模拟前端芯片与导联传感器连接,应用于心电信号的测试,采用RIGOL DS2202 示波器进行测试,结果如图12所示.

图12 所设计前端芯片应用于心电信号的测试波形Fig.12 Tested waveform of ECG amplified by the proposed front-end chip

从测试波形可以看出,所设计的芯片对噪声有较好的抑制能力.经测试,所设计的模拟前端放大倍数约为5000,从图12可以看出,放大后的信号峰-峰值为2.04V,故可推算出所测量的心电信号的峰-峰值为400μV 左右.

5 结论

文中采用0.18 μm CMOS 工艺完成了一款具有较好PSRR 和CMRR 的用于神经信号采集的植入式模拟前端.该设计通过采用斩波调制技术来实现低噪声的性能,使用带电流DAC 的纹波抑制环路进行输出纹波的抑制,并引入了共模反馈机制,从而避免了MOS 管由于电流不平衡而进入线性区.该模拟前端的等效输入噪声为2.59 μV,通频带处的PSRR为108 dB,CMRR 为146 dB,可满足植入式神经信号采集的要求.

[1]吴朝晖,梁志明,李斌.一种植入式神经控制信号传输的数据编码方法[J].华南理工大学学报:自然科学版,2009,37(9):62-66.Wu Zhao-hui,Liang Zhi-ming,Li Bin.A data coding method for transmitting implantable neural control signals[J].Journal of South China University of Technology:Natural Science Edition,2009,37(9):62-66.

[2]薛凯峰,黄平.微机电系统二维线圈的能量接收性能[J].华南理工大学学报:自然科学版,2010,38(8):89-94.Xue Kai-feng,Huang Ping.Energy-receiving performance of two-dimension coil in micro electromechanical systems[J].Journal of South China University of Technology:Natural Science Edition,2010,38(8):89-94.

[3]Nielsen J H,Bruun E.An implantable CMOS front-end system for nerve-signal sensors [J].Analog Integrated Circuits and Signal Processing,2006,46(1):7-15.

[4]Yamu H,Sawan M.CMOS front-end amplifier dedicated to monitor very low amplitude signal from implantable sensors[C]//Proceedings of the 43rd IEEE Midwest Symposium on Circuits and Systems.Lansing:IEEE,2000:298-301.

[5]Enz C C,Temes G C.Circuit techniques for reducing the effects of opamp imperfections:autozeroing,correlated double dampling,and chopper stabilization[J].Proceedings of the IEEE,1996,84(11):1584-1614.

[6]Wu R,Makinwa K A A,Huijsing J H.A chopper currentfeedback instrumentation amplifier with a 1 mHz 1/f noise corner and an AC-coupled ripple reduction loop [J].IEEE Journal of Solid-State Circuits,2009,44(12):3232-3243.

[7]Fan Q,Sebastiano F,Huijsing J H,et al.A 1.8μW 60nV/Hz capacitively-coupled chopper instrumentation amplifier in 65 nm CMOS for wireless sensor nodes [J].IEEE Journal of Solid-State Circuits,2011,46(7):1534-1543.

[8]Xu J,Yazicioglu R F,Grundlehner B,et al.A 160 μW 8-channel active electrode system for EEG monitoring [J].IEEE Transactions on Biomedical Circuits and Systems,2011,5(6):555-567.

[9]Harrison R R,Charles C.A low-power low-noise CMOS amplifier for neural recording applications [J].IEEE Journal of Solid-State Circuits,2003,38(6):958-965.

[10]Chae M,Kim J,Liu W.Fully-differential self-biased biopotential[J].Electronics Letters,2008,44(24):1390-1391.

[11]Do A T,Tan Y S,Lam C,et al.Low power implantable neural recording front-end [C]//Proceedings of 2012 International SoC Design Conference.Jeju Island:IEEE,2012:387-390.

[12]王忆,何乐年,严晓浪.温度补偿的30 nA CMOS 电流源及在LDO 中的应用[M]// 何乐年,王忆.模拟集成电路设计与仿真.北京:科学出版社,2008:269-271.

[13]Yin M,Borton D A,Aceros J,et al.A 100-channel hermetically sealed implantable device for chronic wireless neurosensing applications [J].IEEE Transactions on Biomedical Circuits and Systems,2013,7(2):115-128.

[14]El-Kholy A,Ghoneima M,Sharaf K.A 0.8V 6.4μW compact mixed-signal front-end for neural implants [C]//Proceedings of 2012 IEEE International Symposium on Circuits and Systems.Seoul:IEEE,2012:2223-2226.

[15]Pu X,Zhang H,Qin Y,et al.An 8-channel readout frontend for long-term sleep quality monitoring [C]//Proceedings of 2011 IEEE Biomedical Circuits and Systems Conference.San Diego:IEEE,2011:385-388.