雷达数据处理单元主机系统的设计与实现

2015-11-22周小武花纹波

周小武 花纹波

(中航工业航空计算所,陕西 西安710068)

雷达数据处理单元主机系统的设计与实现

周小武 花纹波

(中航工业航空计算所,陕西 西安710068)

雷达数据处理单元是飞机雷达处理机中的重要糸统,要求具有很高的性能和集成度,而其核心部分主机模块的功能强大与否影响着整个雷达系统的性能。文章讨论一种的雷达数据处理单元的构成与原理。其主机模块采用高性能处理器作为数据处理中心,同时拥有LBE总线和VME总线两个总线接口电路,以实现控制内却从设备和与外部系统进行数据交换两个功能。

数据处理;双总线接口系统;机模块设计

近些年来,随着现代航空工业的不断发展,大量先进的机载设备不断装备到飞机上,因此使得机载系统的电子化、集成度不断提高,同时,对其性能的要求也越来越高。雷达数据处理单元作为飞机雷达综合处理机中的重要部分,其性能及集成度尤为重要。其中,主机模块是核心部分,不仅要通过内部总线控制雷达数据处理单元的各个从设备,还要承担起与外部设备的数据交换任务,因此,其功能的强大与否影响着雷达系统甚至整个机载设备的效率。

1 雷达数据处理单元系统结构组成

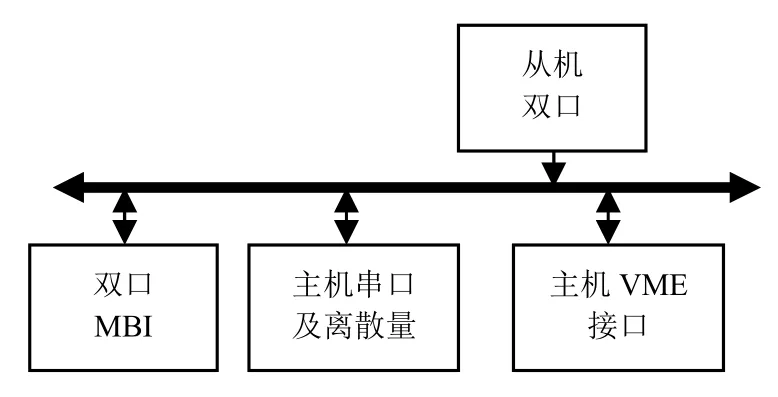

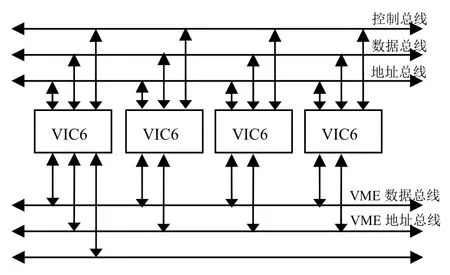

雷达数据处理单元是雷达综合处理机中的数据处理部分,由 3个模块组成,分别是:主机模块、从机模块和接口模块。各模块之间通过LBE总线相连,主机模块通过从机板和接口板上的双口RAM进行数据传送,模块内通过CPU内总线互连,其中接口模块不仅具有多路总线接口的功能,还包括主机模块的 6路串口及若干离散量资源,该资源只有主机模块可通过LBE总线直接访问。系统结构如图l所示。

图1 某雷达数据处理单元的组成结构

2 主机模块的构成

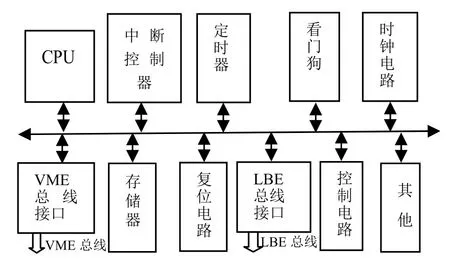

在此雷达数据处理单元组成中,主机数据处理器模块作为LBE总线上的唯一主控设备。其硬件组成结构如图2所示。

图2 主机模块的组成

需要管理LBE总线上的资源,并可作为VME总线的主/从设备,通过母板VME总线与外部信号处理部分进行通讯,它对整个数据处理单元做管理,分配和处理的作用,所以是整个系统的核心部分,主机数据处理器模块是其中的难点,本文重点讨论它的设计思路及实现方法。

2.1处理器的选择

中央处理器CPU是主机数据处理器模块的核心部件,选用Intel公司的通用高性能徽处理器MD80486芯片(+5v供电)。设计其工作在保护模式下,Cache不使能,其外部时钟最高频率为33MHz。

2.2复位信号处理

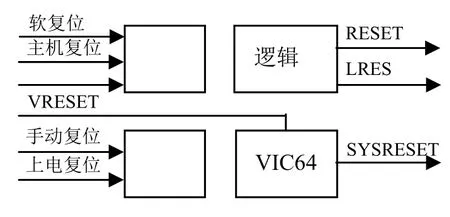

处理机核心部件的复位包括:软件复位、主机模块复位、系统复位和上电复位。其中,软复位由I/O写端口产生;上电复位是由复位电路MAX791监视电源,在VCC>4.65V时产生一个长度为200ms的复位脉冲。主机模块复位和系统复位由主机模块不同的复位按钮产生,其中主机模块复位还要通过主机模块的RESET信号复位接口板的主机资源,系统复位来自机箱面板的RSTIN信号,LBE总线的LRES信号复位接口板和从机板。如图 3所示。同时,主机模块复位添加了去抖动电路,选用合适的电阻和电容组成,保证了主机模块复位信号的稳定。

同时,主机模块可通过写 VIC64寄存器的方法产生SYSRESET信号,用来复位VME总线上的SHARC板,但不复位主机模块(VIC64除外)。

图3 复位逻辑

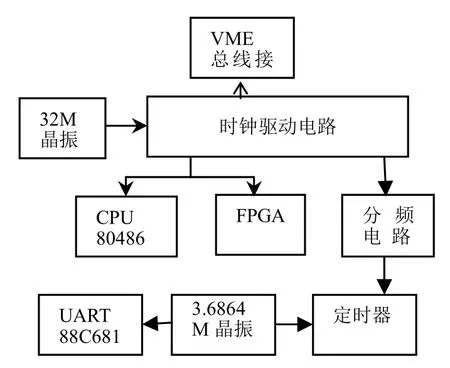

2.3时钟信号实现

处理器CPL工作主频由时钟电路产生,考虑到主机模块的VME总线接口电路最高使用64MHz时钟,该时钟可由CPU的工作主频32 MHz时钟倍频后产生,为减少时钟种类,提高系统工作可靠性,设计时将32 MHz作为基本时钟,一方面直接提供给 CPU;另一方面经过倍频产生 64MHz时钟提供给VME总线接口电路,且该基本时钟还将用于时序逻辑电路的同步和访问超时电路。同时,对高频时钟信号在靠近源处串接33欧姆电阻,增强信号的稳定性。另外,还没计添加1个3.6864MHz的晶振.以此提供3.6864MHz的时钟给通用异步串行通讯口(UART)芯片。如图4所示。

图4 时钟电路

2.4看门狗电路

为了实现软件运行轨迹的可靠性,处理机核心部件提供看门狗电路,定时周期100ms(50nf电容)。看门狗电路由硬件实现,在地面调试状态下自动禁止,但可用软件设置使能/禁止;在实时状态下自动使能,当看门狗有效后产生非屏蔽中断并点亮本模块故障灯。

2.5中断

主机主要提供1个非屏蔽中断,15级可屏蔽中断的处理能力,因此选用2片8259A中断控制器,通过主从式级联来实现处理15级可屏蔽中断的功能。可屏蔽中断由8259A中断控制器管理,非屏蔽中断由看门狗电路和总线超时电路触发产生,直接接到CPU的MNI引脚,为区分非屏蔽中断的类区分非屏蔽中断的类型(看门狗/总线超时),可查询状态寄存器来判定。

2.6总线接口

主机有LBE总线和VME总线2个接口,从机只有LBE总线接口。主机是LBE总线的唯一主设备,从机只是LBE总线的从设备。

2.6.1LBE总线接口

LBE总线用于雷达数据处理单元内的数据传输,采用16位数据宽度,且根据应用需要,设计只采用LBE总线中的部分信号。LD15-LD0提供LBE总线主设备与其他模块间的数据通路;LA15-LA0由主设备发出,为寻址存储器或IO提供地址;LADS由主设备发出,表示1个总线访问周期开始;LMEN由主设备发出,表示访问存储器空间;LIOCS由主设备发出表示访问IO空间,LW/R由主设备发出,表示写/读操作(“1”表示写/“0”表示读),LDEN由主设备发出。表示数据有效,通常用于控制总线收发器;LRDY由从设备发出,表示从设备允许主设备结束总线访问周期,从设备通过三态门输出该信号;LRES*由主设备发出,表示LBE总线复位; LCLK由主设备发出,它是LBE总线系统时钟。使用该信号产生LRDY;GSE是一个输入信号,指示当前运行状态,高电平表示实时运行状态,低电平表示地面调试状态。特别注意的是,主机模块还定义了GO/NOGO信号,该信号由LBE总线主设备发出,高电平表示主设备能正常运行,低电平表示主设备模块不能正常工作,该信号作为接口板的输入。

2.6.2VME总线接口

VME总钱接口是主机模块的重要组成部分,也是整个模块的关键技术之一。主机模块的VME总线接口能够实现以下功能:总线控制器功能;主/从设备功能;中断处理器功能;A32/D32/单字传送和块传送能力。因此,在设计时,选用以VIC64为主协议芯片,以配套的CY7C964作为扩展芯片,整个VME总线接口可用一片VIC64和三片CY7C964顺次级联来实现,VIC64作为主协议芯片,三片CY7C964作为VME总线的数据和地址扩展。VME总线接口的实现框图如图5。

图5 VME总线接口电路

采用这种方案,主机模块既可以做系统控制器,叉可以做总线主设备、总线从设备,还可以做中断请求者、中断处理者,满足了系统设计技术要求。

2.7逻辑控制电路

2.7.1局部总线控制逻辑

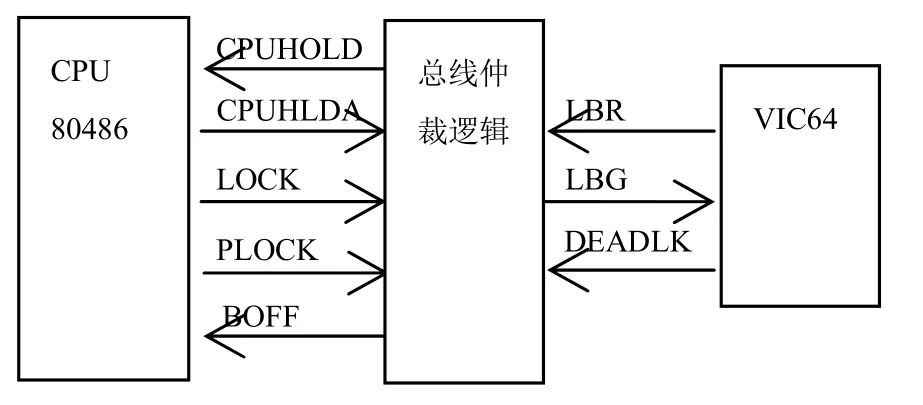

主机模块内局部总线可由CPU、VME接口芯片中的任何一个来占用,局部总线仲裁电路的设计也是主机模块详细设计中的一项要点。考虑到VME是整个系统信息交换的重要通道,它的利用率的高低直接决定了系统的性能所以将其优先权定为最高,只要CPU不处于总线锁定(LOCK#或PLOCK#为低)状态,它就可以获得总线占用权,此外,一旦系统出现了死锁状态,则无论 CPU是否处于总线锁定(LOCK#或PLOCK#为低)状态,总线仲裁逻辑都会强制CPU放弃总线(将 BOFF#信号置低),以解除死锁。CPU承担着所有的数据处理和管理任务,其性能的发挥也对整个系统的性能有着决定性的作用,因此将其优先权定位最高。局部总线仲裁逻辑如图6所示。

图6 总线仲裁

2.7.2主机模块控铡逻辑

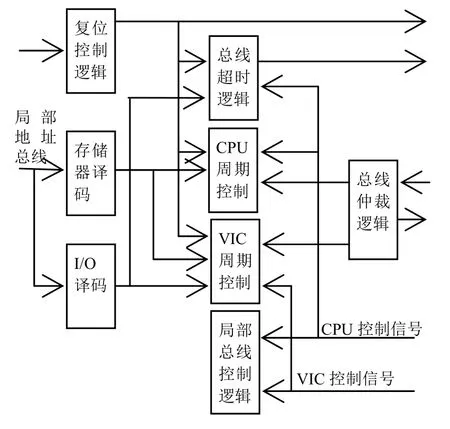

主机模块逻辑控制器采用了XILINX公司的FPGA芯片XC4010E,控制逻辑结构如图7所示。

图7 核心控制逻辑结构框图

主机模块逻辑核心控制器是整个主机模块的控制核心,它将模块上的全部控制逻辑都集成在内,其中包括复位产生逻辑、存储器译码,I/O译码、CPU总线周期(存储器读写、I/O都写)控制,总线仲裁逻辑、CPU总线周期控制信号到VME接口控制信号的转换逻辑。

3 系统的软件设计

该雷达数据处理单元在设计时采用嵌入式实时操作系统VxWorks及配套的开发环境Trnado,由实时多级多任务操作系统,自测试程序,地面支持系统组成,负责控制管理包括中央处理器,存储器,中断源,接口等资源,使整个系统安全、可靠、正常的运行,为整个系统提供实时,正确的软件运行环境和软件开发,系统维护平台。 系统软件可工作在 3种状态下,具体工作状态由设置状态离散量来控制:

a.空中运行状态:装机后的工作状态,系统进行上电BIT测试、启动操作系统、启动已驻留的应用程序。

b.地面单机调试:系统处于地面调试工作模式,进行上电BIT测试后启动操作系统及Tornado调试环境支持程序。此种工作模式便于用户进行高级符号调试。

c.地面多机调试:系统处于地面调试工作模式,进行上电BIT测试后启动操作系统及地面多机支持系统,进行系统调试。

4 结束语

本文讨论了一种数据处理计算机的设计思路和具体结构,介绍了此种高速数据处理计算机的设计实现方法和具体工作原理。此系统拥有的双总线系统,进行内外数据交换,这种设计优点有着数据交换灵活,总线利用率高,设计结构运用,易维护等特点。为机载数据处理系统的设计提供较为清晰的结构和思路参考。

[1] 汪小燕,王俊峰,徐文.VME总线数据上行中断传输及从设备接口设计[J].微电子学与计算机,2007,24(3):208-209.

[2] 丁岐娟,王志红.雷达数据处理的双系统设计[J].雷达科学与技术,2005,(4):240-243.

[3] Hans-Peter Hoffmann.Rational Harmony for Systems Engineering Deskbook[M].Release 3.IMlIBM software GROUP,2010.

[4] American National Standard.Secretariat VMEbus international tradeassociation[M].American Naiional Standard lnstitute Inc,1995.

Design and implementation of the host system

the radar data processing unit is an important issue in the plane radar system, requirements of high performance and integration, and its core part of the host called naan piece of powerful or not affects the performance of the whole radar system. We are here to discuss a ray even the composition and principle of data processing unit. The host module adopts the high-performance processor as a data processing center, also has the LBE bus and VME bus two bus interface circuit, in order to realize the control from the equipment and within two functions for data exchange with the external system.

Data processing;Double-bus interface system; desktop module design

TN95

A

1008-1151(2015)04-0019-03

2015-03-12

周小武,男,中航工业航空计算所助理工程师,从事航空计算机硬件研究。