双轴集成加速度计结构设计

2015-11-14曹延磊丁兰

曹延磊+丁兰

摘 要:该文基于一种集成CMOS MEMS加工方式上,设计了一个双轴平面内加速度计。加速度计结构呈对称结构,有一个主体质量块、四个小质量块、8个弹簧和感应电极组成。理论上此加速度计可以提供X和Y方向相同的检测灵敏度。

关键词:加速度计 MEMSPost CMOS

中图分类号:V241.4 文献标识码:A 文章编号:1672-3791(2015)07(c)-0059-03

IT业的未来主要集中在可穿戴设备、车联网、智能家居、云计算这几方面。最几年,随着智能手机与可穿戴设备的兴起,集成惯性传感器的应用领域从最初的汽车工业和航空已。经拓展到消费电子领域。可以预见集成惯性传感器未来会深入到人类生活各个方面。

加速度计是目前产量最大的惯性传感器,它们已经被广泛应用于汽车而工业和消费电子。而低生产成本、单片集成、低功耗和高信噪比的加速度计仍是最近的研究热点。

1 集成加速度计制备方式

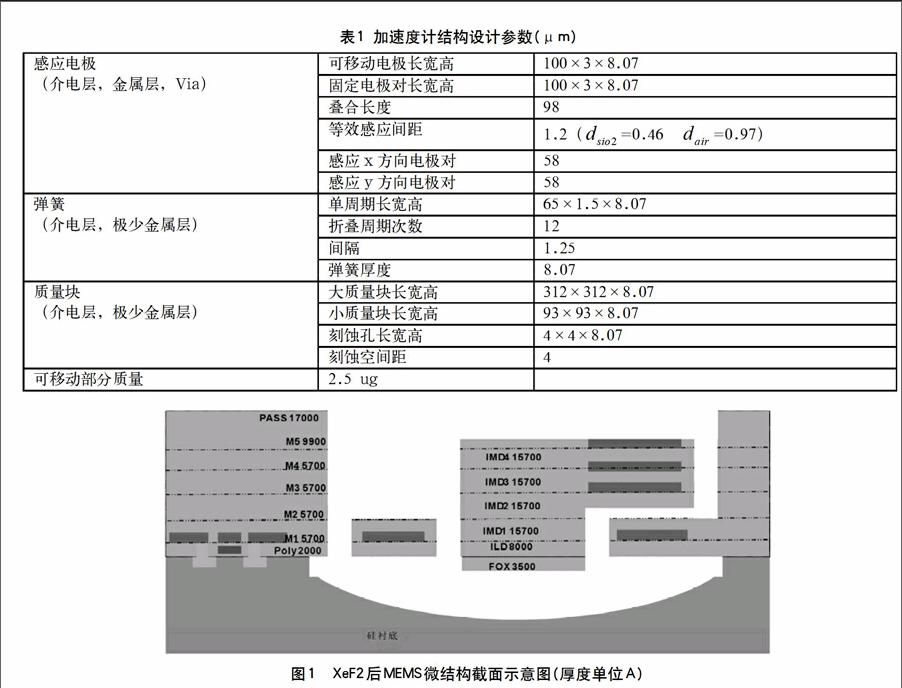

CMOS工艺中主要堆叠的材料有,单晶硅衬底,多晶硅层(Poly)、金属层(Al)、氧化层(Fox,氧化栅极和USG介电层),钨通孔等。由图1可知,顶层金属(M5)的顶部到FOX的距离8.07μm。这样的SiO2厚度足可以做薄膜加速度计的质量块。CMOS MEMS加速度计工艺步骤如下:

(1)将CMOS工艺线上回来的器件投入硫酸(H2SO4)双氧水(H2O2)的溶液中。直到金属刻蚀完成。

(2)刻蚀后需要防止粘附。用纯水中将硫酸溶液稀释置换出来。再用异丙醇溶液将纯水置换。然后放到加热器中将异丙醇蒸发干净。到此金属牺牲层刻蚀完成。

(3)金属牺牲步骤完成后,需要对悬浮结构中的钝化保护层去除。去除钝化层的方法采用反应离子刻蚀(RIE)去除,从去除覆盖微结构处的PASS,顶层金属裸露出来。此步骤工艺完成后如图1示意图所示。进行完RIE后,MEMS微结构仍未悬浮,必须进行(4)步骤的硅衬底刻蚀才能完成释放。

(4)采用反应离子刻蚀(RIE)对衬底进行刻蚀释放结构。衬底刻蚀完成后微结构释放悬浮起来,如图1所示。

2 结构设计

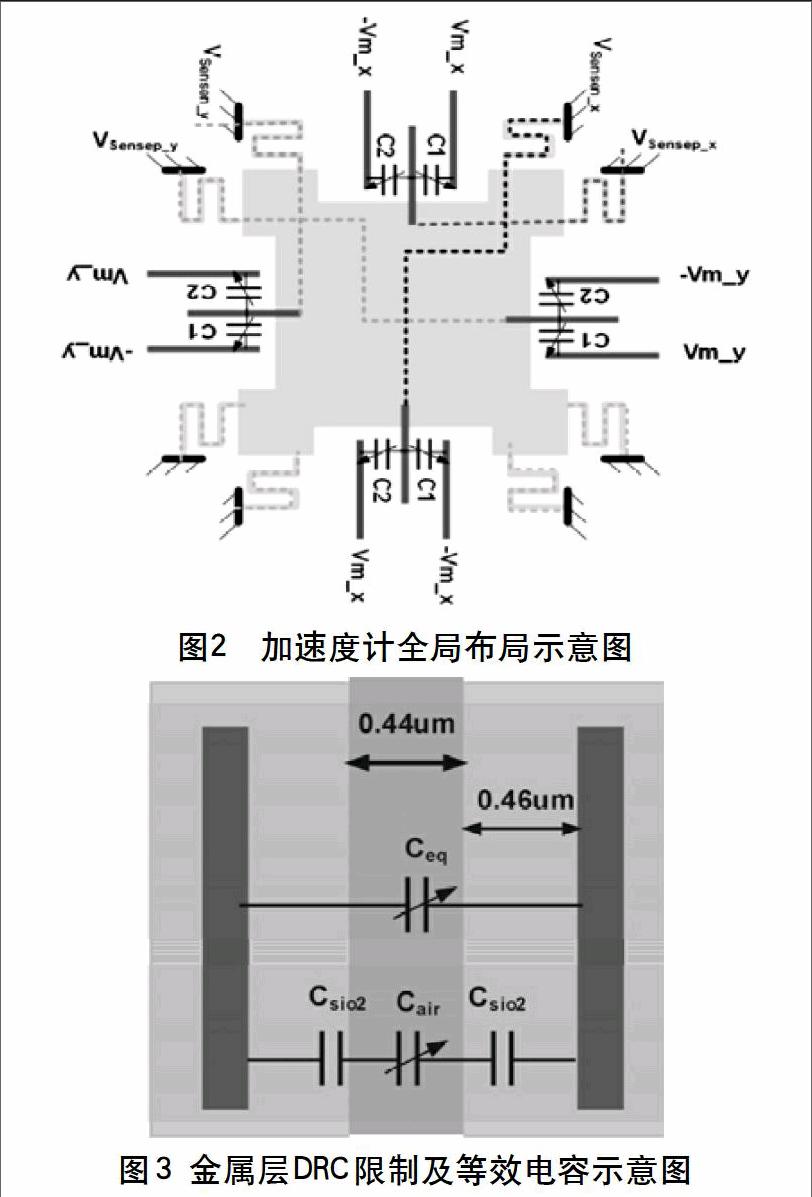

图2为加速度计整体结构示意图。外部电路向加速度计提供的信号有:用于x方向的和-;用于感测y方向和-。加速度计向外部电路输出的信号有:感测x方向运动的和差分输出信号;感测y方向运动的和差分输出信号。其中有四个弹簧没有用于信号输出,在这4个弹簧中需要加入金属线保证整体的弹性常数对称。

2.1 质量块设计

质量块是加速度计重要组成部分。当加速度计受到外加速度作用时,质量块会产生位移。在电容式加速度计中,较大的位移会产生较大的变化电容,较大的变化电容会产生较大的Vsense。但是质量块位移大小一般由两个因素决定,(1)质量块的质量;(2)弹簧的弹性系数。质量块中布满了小孔阵列,其目的有两个:(1)便于在后制程中更容易释放整个质量块微结构,(2)对质量块起阻尼作用。与实现电学连接的Via通孔不同,质量块中的Via通孔起牺牲层的作用。标准的DRC约束Via的大小为0.36×0.36μm2大小,间隔不小于0.35μm,这样才能实现较好通孔填充,但是这样的约束无法满足做牺牲层的条件,因此Via做牺牲层时需要违反DRC规则。

为了获取较大的质量块,在本论文中,质量块结构由Metal5统一位置的的Passivation层一直向下到ILD层构成。3 ug的质量块需要的版图面积为13 000μm2。考虑到刻蚀空以及可移动电极的周边的去除,版图面积还要增大。质量块有1个大质量块和四个位于四角的小质量量块构成。

2.2 弹簧设计

加速度计检测的加速度方向在XOY平面内,为了保证检测的精度和敏感方向,弹簧在设计时需要保证在z方向的弹性常数大于在XOY平面内的弹性常数。并且x和y方向的弹性常数不能过小,过小会增加系统的热噪声。另外对于本文采用的电容检测方式的结构,当受到外界加速度时z方向的位移应当远远小于感应电极的高度,以保证x和y方向的电容不会受到影响,从而提高交叉轴灵敏度。

MEMS中由悬臂梁构成的弹簧同螺旋弹簧类似,如果采用多个弹簧构成弹簧系统,弹簧并联时系统的弹性常数为所有各个弹性常数之和;弹簧串联时,系统弹性常数的倒数为各个弹性常数倒数和。因此,可以采用多个弹簧并联来增加。另外,为了获得较高的灵敏度,通常选择增加l,折叠弹簧可以有效的增加l,并能减小弹簧所占的版图面积。低复杂度的弹簧外形图2所示。弹簧采用折叠形式,弹簧折叠周期N=12,半周期长度l=64μm,宽度w=1.5μm。

在该论文中,弹簧的工艺层和质量块一样,采用了最多的堆叠层(从ILD到与Metal5同位置的Passivation层),从而增加了厚度t,降低z方向的弹性系数。弹簧是连接可移动质量块与锚定端的桥梁,可移动单元上的信号只能由弹簧传递给处理电路.

2.3 感应电极设计

该文设计的加速度计的感测方向为XOY,所以感应电极采用平行感测分布。对于平行板电容有:

极板的重合面积越大,极板间距越小就能获得越大的电容;极板间距越小可以获得更高的灵敏度。较多的感应电极和增加感应电极产度可以使总体电容增加。需要指出,感应电极不能过细,也不能过长,由于残余应力的存在,过细过长会增加感应电极曲率,导致感应电极在水平方向上失配。

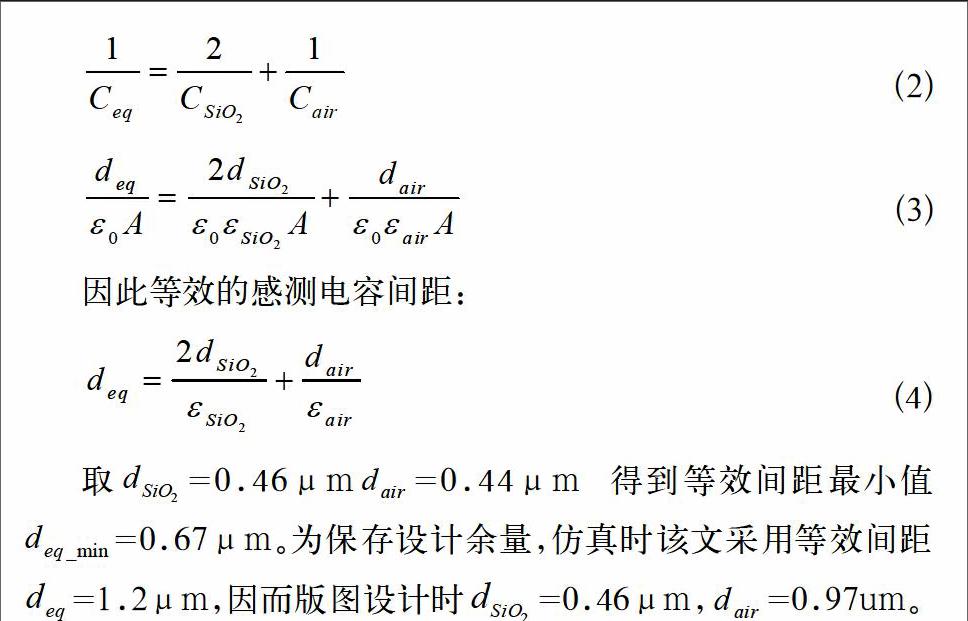

在Post CMOS中,极板间距受到设计规则和限制,顶层金属的最小线宽为0.44μm,另外,由于电容极板含有金属,金属必定被氧化物包围,因此感应电极的间距不是两侧金属面之间的距离。下面引入等效间距,对感应电极间距进行讨论。如图3所示。由于介电层SiO2的介电常数近似等于4,所以等效的感测电容:

取=0.46μm=0.44μm 得到等效间距最小值=0.67μm。为保存设计余量,仿真时该文采用等效间距=1.2μm,因而版图设计时=0.46μm,=0.97um。

为了得到更多感应电极重叠面积,从厚度上来考虑应当采用顶层金属。该文感应电极的感应厚度从CONTACT底部到顶层金属Metal5,共8.07μm。同质量块中起牺牲作用的Via不同,制作感应电极时Via有些起电学连接作用,有些Via只其牺牲层作用。起电学连接的Via,一定要遵循CMOS的DRC规则,因为Via的间距限制,从而感应电极的有效面积比从CONTCAT(连接Metal1和有源区的通孔)的底部到Metal5的顶部构成面积小。

2.4 加速度计整体结构总结

3 结语

该文首先叙述应用需求,从而分析出集成加速度计的优越性。然后结合一种牺牲金属和各向同性刻蚀硅衬底的加工方式,设计的加速度计有一个主体质量块、四个小质量块、8个弹簧和感应电极组成。理论上此加速度计可以提供X和Y方向相同的检测灵敏度。应当指出加速度计的设计和仿真是相互结合反复修改的过程,物理尺寸不仅需要满足产线的工艺能力,还需要满足消费电子使用的应用场合。

参考文献

[1] 张兴,黄如,刘晓彦.微电子学概论[M].北京:北京大学出版社,2010.

[2] Brand O(著), Fedder G K(著), 黄庆安(译), 秦明(译). CMOS MEMS技术与应用[M].南京:东南大学出版社,2007.

[3] Tsai Ming-han, Liu Yu-chia, Fang Weileun. A Three-Axis CMOS-MEMS Accelerometer Structure With Vertically Integrated Fully Differential Sensing Electrodes [J].Journal of Microelectromechanical Systems,2012,21(6):1329-1337.