基于图像分块的CL4小波实时处理及FPGA实现

2015-07-09李小明等

李小明等

摘 要: CL4矢量小波具有的一系列优异特性,在红外图像弱小目标预处理中应用广泛,但它的实时性使其应用受到限制。在分析了CL4小波算法结构基础上,研究了小波系数的量化方法,提出一种将原始图像分块小波处理的方法,在FPGA中采用流水算法实现,并对关键算法进行了ModelSim仿真,提高了CL4小波算法的实时性。

关键词: 图像分块; 矢量小波; CL4; FPGA

中图分类号: TN919?34; TP391 文献标识码: A 文章编号: 1004?373X(2015)08?0016?03

CL4 wavelet real?time processing and FPGA realization based on image blocking

LI Xiao?ming1, 2, LIU Hai?yan3

(1. Army Officer Academy, Hefei 230031, China; 2. Anhui Key Laboratory of Polarized Light Imaging Detection Technology,

Army Officer Academy, Hefei 230031,China; 3. Detachment 52, Unit 73101 of PLA, Xuzhou 221008, China)

Abstract: CL4 wavelet has some excellent characters and is widely applied to infrared image processing of small weak targets, but its worse real?time performance limits its application. The quantification method of wavelet coefficient is researched on the basis of structure analysis of CL4 wavelet algorithm. A method which blocked the original image into some sections is proposed according to CL4 algorithm, which is realized by the pipeline algorithm used in FPGA. The key algorithm was simulated with ModelSim. The method improved real?time performance of CL4 algorithm.

Keywords: image blocking; vector wavelet; CL4; FPGA

0 引 言

红外探测设备获取的红外偏振原始图像受探测器噪声、电路噪声和背景噪声等影响,图像的信噪比下降,在进一步获取目标信息之前,首先需要对图像进行降噪等预处理,抑制退化图像的干扰信号。图像的降噪主要采用基于单帧图像滤波的预处理方法,即采用滤波器对原始图像卷积,选用的滤波器性能对预处理效果有决定性影响。常用滤波器主要包括高斯滤波器、均值滤波器、中值滤波和双边滤波或者是它们的改进形式。CL4(Chui?Lian4)等矢量小波兼有正交性、对称性、紧支撑性、高阶消失矩和多重多分辨率等特性[1?2],在红外图像降噪处理中效果良好,由于CL4小波算法复杂度较高,其时性不强,在目标实时跟踪等方面应用受到限制。FPGA具有可编程重置,可通过牺牲规模换取算法时间,适合用于以乘加算法为主的小波卷积运算。本文研究了CL4算法在FPGA中的实现方法,并对关键算法进行了仿真,通过对原始图像进行分块流水操作,大大提高了算法的实时性。

1 矢量小波算法原理

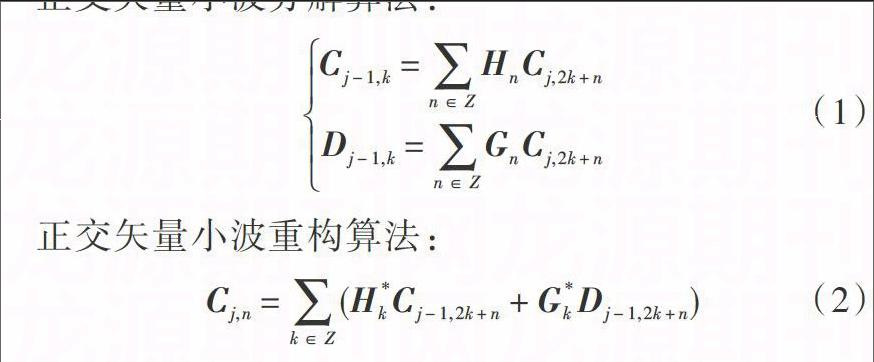

矢量小波理论基于多分辨分析(MRA)思想,采用两个或两个以上的函数作为尺度函数生成的小波[3],其多分辨分析空间由这多个尺度函数张成。将正交标量小波的分解与重构算法推广至正交矢量小波,可以得到正交矢量小波分解与重构算法,如式(1)和式(2)所示。

正交矢量小波分解算法:

[Cj-1,k=n∈ZHnCj,2k+nDj-1,k=n∈ZGnCj,2k+n] (1)

正交矢量小波重构算法:

[Cj,n=k∈Z(H*kCj-1,2k+n+G*kDj-1,2k+n)] (2)

式(1)和式(2)中[Cj,k=(c1,j,k,…,cr,j,k)T]为矢量小波分解和重构的低频系数矩阵;[Dj,k=(d1,j,k,…,dr,j,k)T] 为矢量小波分解和重构的高频系数矩阵;[Hn和Gn]分别是低通滤波器系数矩阵和高通滤波器系数矩阵。[H*k与G*k]分别为[Hn和Gn]的复共轭矩阵。

2 CL4小波去噪方法

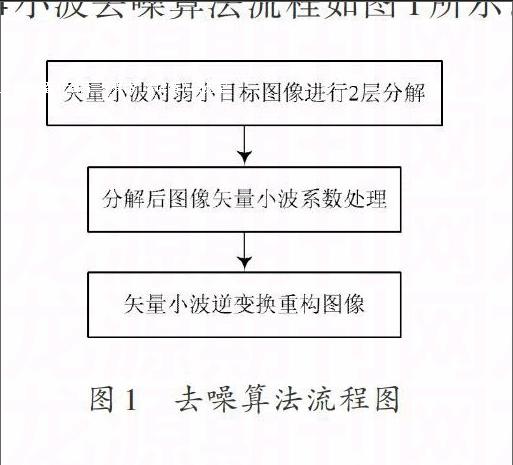

CL4小波去噪分为以下几个步骤:首先对原始图像进行矢量小波分解;其次对分解得到的小波系数进行舍低频、小波去噪和增强等处理;最后进行小波逆变换重构图像。CL4小波去噪算法流程如图1所示。

3 FPGA实现考虑的几个问题

3.1 系数的量化

FPGA是一种二值逻辑器件,只适合处理二进制整数,而矢量小波去噪算法中的小波分解和小波重构卷积运算滤波器系数都是小数,因此,需要将滤波器系数转换为有限长的二进制整数,另外输入数据、滤波器系数、临时变量及运算结果也需用有限字长量化。因此,需要分析量化滤波器系数对滤波器的影响,以量化单位脉冲响应系数对性能的影响进行分析[4?5]。

用转置结构设计的低通滤波器,采用舍入量化系数,可能最大阻带衰减为:

[Amax<20log(2-BN) dB]

取阻带衰减>50 dB,N=32,求得B=12位,即所要求的字长为12位。量化后,通带的最坏情况的峰值纹波Rmax和阻带衰减Amax可以表示为:

3 dB纹波:[20log(1+δp)≥δp=0.412 54]

50 dB衰减:[-20log(1+δs)≥δs=0.003 162]

[Rmax=20log(1+δp+|E(ω)|) dB =20log(1+0.412 54+0.001)=3.003 162]

因此,通带最坏情况时峰值纹波[Rmax]仅增加了0.003 162,将滤波器系数均乘以212,将结果舍入最近的整数进行量化。检查量化后滤波器的频率响应,仍然满足要求,尤其是阻带衰减,量化前和量化后的变化不大。对于CL4的高通滤波器系数,按照相同的原则求取量化位数也为12位。

分析CL4矢量小波的滤波器系数可以发现,其32个滤波器系数的绝对值只有8个不相同的小数,每组滤波器系数都这8个数按照不同的顺序和不同的符号的排列。将这8个小数量化成12位,可将CL4小波滤波器系数表示为表1所示。

表1 CL4小波量化后的滤波器系数

3.2 图像的分块

CL4多小波变换是一种二维卷积变换,行变换后再进行列变换。由CL4小波算法和滤波器结构可知,CL4小波是以每8个图像数据为一组与滤波器进行卷积,因此列变换最快也需要8行图像完成小波行变换后才能进行。对每个变换后的小波系数的处理,需要用到该小波系数所属子块中的所有小波系数,而只有完成所有行和列卷积运算后,才能得到每个子块的所有小波系数[6],即小波分解完成后才能进行小波系数处理,对于320×240大小的红外图像,则至少需要76 808个时钟周期延迟,才能开始小波系数处理,难以满足系统实时处理的要求。

设计中采用图像分块处理技术[7],首先将一幅红外图像分成若干小块,同时对每个小块图像进行CL4小波分解、系数处理及重构,最后将重构得到的若干小块图像合并成完整的红外图像。硬件实现中根据CL4小波算法特点,将原始图像分成8×8大小的小块,图像分块原理如图2所示,其中A1~A8…H1~H8为D触发器。

由于采用了分块工作模式,因此在图像处理过程中,并不需要存储整幅图像,只需要存储经过分割的图像小块,视频输入图像经过由D触发器和列移位寄存器组成的阵列后,每行的D触发器延时8个时钟周期,列移位寄存器延时316个时钟周期,从数据流进入图像分块模块,经过2 248个时钟周期,D触发器组成的缓冲器阵列恰好构成一个经过分割的图像小块,此时,由触发时钟将缓存在D触发器中的图像块写入到存储RAM中由后续矢量小波变换模块处理。此后,每隔8个时钟周期,D触发器组形成新的一块子图,直到这8行数据图像分块完成开始下8行数据图像的分块。

4 CL4小波FPGA实现

4.1 嵌入式阵列模块的实现

Altera 公司的Stratix 系列 FPGA 器件是该公司的高端器件,除了逻辑功能块(LAB)之外,还采用嵌入式阵列块(EAB)[8]。每个LAB由10个LE、LE进位链、LAB控制信号、1个局部互联、LUT链和寄存器链连接线构成。Stratix器件的EAB由几列M4K存储器块构成。M4K存储器块可以达到200 MHz的工作频率。每个M4K存储器块能够实现包括双端口RAM、单口RAM、ROM、移位寄存器块和 FIFO 缓冲区等各种不同的功能块。采用标准触发器的常规方法实现大移位寄存器块需要的较多逻辑单元(LE)。使用Stratix器件中的EAB实现移位寄存器可节省大量逻辑单元(LE)和布线资源,实现方法更为简便。1个 w×m×n移位寄存器的大小由输入数据宽度(w)、抽头长度(m)和抽头数(n)来决定。同时,1个w×m×n移位寄存器的大小必须小于或者等于4 608位,并且m×n的大小必须小于或者等于 36 位。当需要更大的移位寄存器块,可以采用级联存储器块方式。数据在时钟的下降沿被写入每个地址区域,在时钟的上升沿被读取,移位寄存器模式逻辑可以自动地控制在一个时钟周期的正边沿和负边沿来进行数据移位,通过调用 QuartusI 软件中的 altshift_taps 宏模块就可以实现移位存储器块

4.2 矢量小波分解及重构

按照CL4小波算法原理,首先需将一组8个输入数据分别与表1中给出的4组滤波器进行卷积运算,可得到4个卷积结果,然后再将这8个输入数据的前4个数据和后4个数据进行互换,再与这几组滤波器进行卷积得到4个结果,这样总共得到8个输出数据。按照上述算法,需要分两步才能实现一组8个输入数据的CL4矢量小波分解变换,不利于模块的实时性。设计中,另外构造了4组和表1中滤波器对称的滤波器,再将一组8个数据分别与表1中的滤波器和构造的滤波器并行卷积,可同时输出8个分解后的小波系数,缩短了卷积算法的延迟。对称滤波器构造的方法是:分别将表1中每组滤波器中的前4个滤波器系数和后4个滤波器系数对调,组成4个新的对称滤波器组。如果在FPGA程序中直接构造这8组滤波器,共需要32个存储空间,分析发现,8组滤波器的系数只是顺序和符号不同,设计中,在FPGA中只存储这8个不相同数的绝对值,卷积时,使用加/减法开关实现系数符号的变换,可节省存储空间。

为了降低卷积算法的延时,采用流水线结构进行小波分解[9?10]。采用如图3所示的转置结构卷积滤波器。将量化后的图像数据每8个为一组,分别流水进入8组滤波器进行卷积。x[n]为流水输入的数据,f[7]~f[0]为滤波器系数,不同的低通滤波器和高通滤波器,f[7]~f[0]分别对应表1中的滤波器系数,y[n]为输入数据该组滤波器卷积结果。

完整的CL4矢量小波分解FPGA实现的ModelSim仿真结果如图4所示,一组图像数据下载到滤波器抽头以后,经过8个时钟周期延迟,同时输出8个滤波器的卷积结果。经过72个时钟周期,输出一个经过分块的图像的分解结果。由于每个分块可以并行运算,大大节省了整幅图像的分解时间。

CL4矢量小波重构也采用带有加减法开关的转置结构卷积滤波器,由于前面对小波系数量化时对小波系数乘了4 096,小波重构后,应该对重构结果除以4 096,即在FPGA中对重构结果向右平移12位。

5 结 语

CL4小波用于图像预处理具有优良的特性。本文根据CL4小波算法结构,利用FPGA易于实现并行流水算法的特点,将原始图像分块进行小波处理。一幅320×240图像,原先需要76 808个时钟周期才能进行小波变换,经过分块处理后,仅需2 248个时钟周期就可以进行小波变换,每块图像经过72个时钟延迟后输出小波变换结果,大大提高了CL4小波算法的实时性。通过ModelSim仿真,验证了算法的可行性。

参考文献

[1] DAUBECHIES Ingrid. Ten lectures on wavelets [M]. Pholadelphia: SIAM, 1992.

[2] 唐惠玲.CL4多小波预处理及其在发电机故障检测中的应用[J].继电器,2007,35(20):43?46.

[3] 崔丽鸿,程正兴.多小波与平衡多小波的理论和设计[J].工程数学学报,2001(12):105?116.

[4] 张丽英,王丽荣.整数小波变换与矢量量化在图像处理中的应用[J].探测与控制学报,2007,29(4):45?48.

[5] 刘毅.基于小波变换与矢量量化的图像压缩算法[D].广州:广州工业大学,2007.

[6] 刘振飞.图像预处理算法的硬件实现[D].哈尔滨:哈尔滨工程大学,2010.

[7] 宋萤,陈科,林江莉,等.基于图像分块的边缘检测算法[J].计算机工程,2010,36(14):196?197.

[8] Altera Corporation. Stratix device handbook [M]. [S.l.]: Altera Corporation, 2003.

[9] 王燕峰,吴新建.基于FPGA的系数对称3×3卷积器的设计[J].光学与光电技术,2004(3):41?43.

[10] 郭书军,王玉花.流水线技术在FPGA设计中的应用[J].北方工业大学学报,2004,16(1):62?64,70.