高动态微弱信标信号载波捕获跟踪的设计与实现

2015-07-09朱斌

朱斌

(第716研究所, 江苏 连云港 222006)

摘 要: 为了研究高动态低信噪比下信标信号的载波捕获跟踪问题,采用两级二阶锁频环(FLL)和一级三阶锁相环(PLL)技术方案。FLL采用基于周期图的鉴频方法,实现极低信噪比下信号载波的捕获。PLL中的三阶锁相环通过对环路压控振荡器(VCO)的输入控制信号进行监测,自适应地调整环路滤波器的带宽,以满足高动态下信号载波频率动态范围大的要求。在基于FPGA构建的信号处理板上验证了上述实现方案,并给出实验结果。

关键词: 载波捕获跟踪; 高动态; 低信噪比; 锁频环; 锁相环

中图分类号: TN911?34 文献标识码: A 文章编号: 1004?373X(2015)08?0012?04

Design and implementation of carrier capture and tracking of weak beacon signal in

high dynamic environment

ZHU Bin

(The 716 Research Institute, Lianyungang 222006, China)

Abstract: To capture and track the signals carrier in high dynamic and low signal?to?noise ratio (SNR) environment, the schemes of frequency locked loop (FLL) with two factorials add phase locked loop (PLL) with three factorials are proposed in this article. To solve the low SNR problem, the frequency discrimination method based on periodogram is used in FLL to realize signals carrier capture under very low SNR. The three?order PLL is monitored by the input control signal of the voltage controlled oscillator (VCO) to adjust the band width of loop filter self?adaptively, so as to meet the requirement of large dynamic range of signal carrier frequency in high dynamic state. The proposed scheme was verified on a signal processing board with FPGAs. The experimental results are presented at last.

Keywords: carrier capture and tracking; high dynamic state; low signal?to?noise ratio; frequency locked loop; phase locked loop

0 引 言

在高动态低信噪比条件下,对信号的载波捕获及跟踪通常先用锁频环(FLL)进行粗捕,使频差小到某一门限值后再切换到锁相环(PLL)进行细捕,从而实现对载波的高精度跟踪[1?3]。考虑低信噪比下高动态信标信号的载频捕获与跟踪,信标信号的多普勒频率及其变化率大,无法直接采用基于频率引导的窄带FLL;信号的多普勒频偏非常大,要求数字锁频环的前置滤波器带宽大,在一定信噪比下,所引入的噪声功率大,使得环路信噪比极低。当噪声电平超过环路工作门限时,无法实现载波捕获与跟踪。文献[4]提出基于FFT鉴频的二阶数字锁频环实现方法,但是环路滤波器的参数固定,系统锁定的带宽有限。文献[5]采用FLL和PLL相结合的方法来实现载波跟踪,对常用的叉积自动频率控制(CPAFC)环进行了改进,改进后的鉴频算法具有更快的捕获速度。文献[6]针对高动态环境下的GPS接收机对信号捕获速度的要求,提出一种基于小波变换和优化FFT的信号捕获方法,提高了运算效率。文献[7]对载波跟踪算法进行综述,分析了三阶的PLL算法,三阶的PLL具有更大的动态范围。为了解决高动态和低信噪比的问题,本文采用两级二阶FLL和一级三阶PLL的实现方案。FLL采用基于FFT周期图的鉴频算法,通过改变FFT的累加次数,来满足更低信噪比的要求;PLL通过对环路压控振荡器(VCO)的输入控制信号进行监测,实现自适应地调整环路滤波器的带宽,以满足信号载波频率动态范围的要求。

1 数学模型

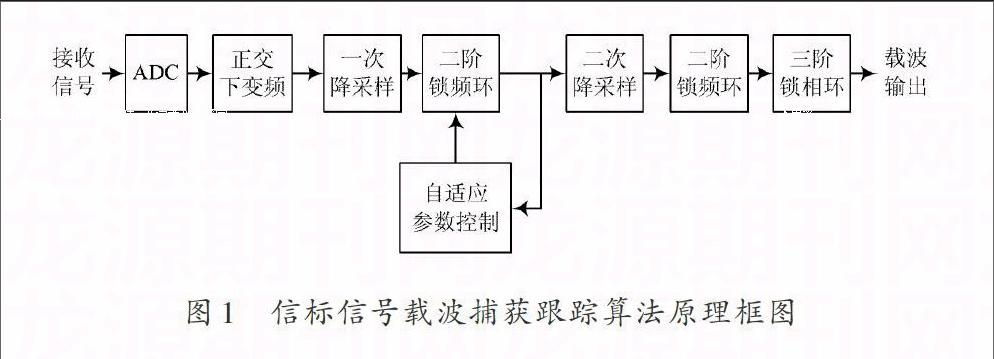

图1为高动态低信噪比下信标信号载波捕获跟踪原理框图。从天线接收的信号经过模拟通道变换到中频后,首先要进行ADC变为数字信号,然后根据信号的载波对信号进行正交下变频,将信号变为基带复信号。再按照信号的多普勒频率及其变化率的范围,确定降采样倍数,对所得的基带复信号进行第一次降采样。然后将信号依次输入FLL和PLL。在第一级FLL后,由于信号的频率大动态变经已经去除,且在可控的小范围内。为了提高频率估计精度,将进行第二次降采样。在经过三阶PLL后,将提取出信标信号的载波输出用于解调空间飞行器的水平和俯仰方位信息。

图1 信标信号载波捕获跟踪算法原理框图

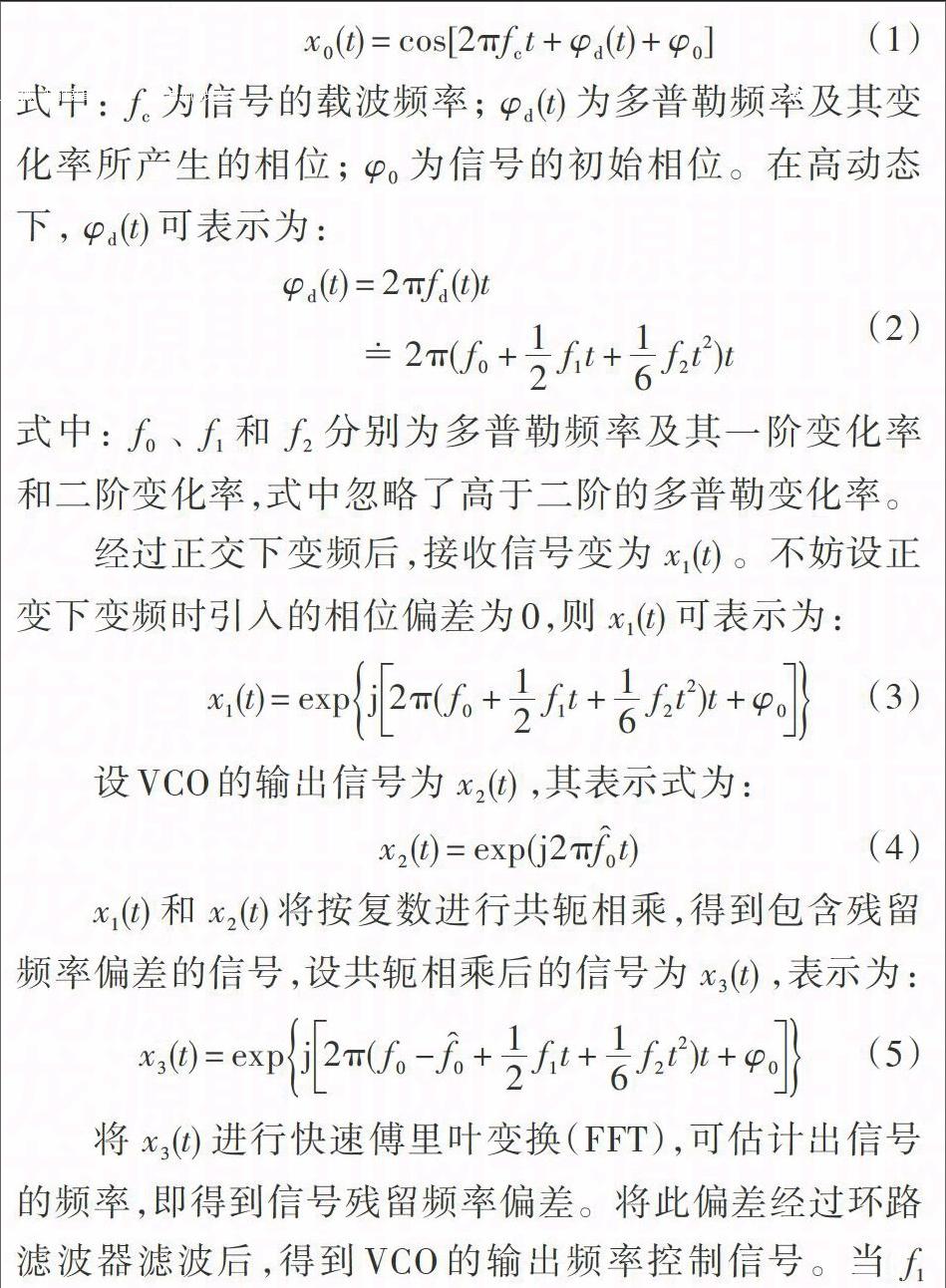

在FLL中,VCO的输入控制信号采用的是残留频差。本算法通过基于快速傅里叶变换(FFT)的频率估计来实现鉴频,从而提取残留频差。接收信号经过模数变换(ADC)后,将按信号的载波频率进行正交下变频,然后将根据信号的带宽进行降采样。设经过ADC后的信号为[x0(t)],表达式为:

[x0(t)=cos[2πfct+φd(t)+φ0]] (1)

式中:[fc]为信号的载波频率;[φd(t)]为多普勒频率及其变化率所产生的相位;[φ0]为信号的初始相位。在高动态下,[φd(t)]可表示为:

[φd(t)=2πfd(t)t ?2π(f0+12f1t+16f2t2)t] (2)

式中:[f0]、[f1]和[f2]分别为多普勒频率及其一阶变化率和二阶变化率,式中忽略了高于二阶的多普勒变化率。

经过正交下变频后,接收信号变为[x1(t)]。不妨设正变下变频时引入的相位偏差为0,则[x1(t)]可表示为:

[x1(t)=expj2π(f0+12f1t+16f2t2)t+φ0] (3)

设VCO的输出信号为[x2(t)],其表示式为:

[x2(t)=exp(j2πf0t)] (4)

[x1(t)]和[x2(t)]将按复数进行共轭相乘,得到包含残留频率偏差的信号,设共轭相乘后的信号为[x3(t)],表示为:

[x3(t)=expj2π(f0-f0+12f1t+16f2t2)t+φ0] (5)

将[x3(t)]进行快速傅里叶变换(FFT),可估计出信号的频率,即得到信号残留频率偏差。将此偏差经过环路滤波器滤波后,得到VCO的输出频率控制信号。当[f1]和[f2]在一定范围内时,通过不断调整VCO的输出频率[f0],可使输出信号的频率控制在一定范围内,即完成对接收信号的频率锁定,从而构成锁频环路。

在第一级FLL中,由于正交下变频后可能的残留频偏范围较大,所以此时采样率较高,设此时的采样率为[fs],FFT的点数为[N],则第一级FLL输出信号频差可控制在[[-fsN,fsN]]以内。在第二级FLL时,在保证信号频谱不发生混叠的条件下,可对信号进行降采样,在FFT点数不变条件下,可提高频率估计精度。设降采样的倍数为[M],则可将输出信号频差可控制在[[-fs(MN),fs(MN)]]以内。经过两级FLL后,此时信号的频偏已足够小,可看作残留的相位偏差,将通过三阶PLL进行去除。在高动态下,由于[f0]、[f1]和[f2]的存在,将使信号的频谱发生扩展。此时,需要根据[f0]、[f1]和[f2]的大小来选择系统采样频率[fs]、FFT点数[N]。选择系统的采样频率[fs]时,需要将信号的带宽及高动态引起的频率扩展统一考虑,使信号满足带通采样定理。由于FFT的点数将直接影响FFT的时间和频率分辨率,点数越大,频率分辨率越高,时间分辨率越低,反之亦然。因此,在选择FFT的点数时,应考虑到时间分辨率和频率分辨率之间的关系。在高动态下,由于接收信号的载波频率实时变化,所以应使FFT的频率分辨率大于信号在一次FFT采样时间内的载波频率变化量,否则进行FFT后在,载波信号在频谱上将不是占一个频点,而是多个频点,将影响频率估计的准确度,从而使残留偏差大于预估值。

2 基于周期图鉴频的FLL

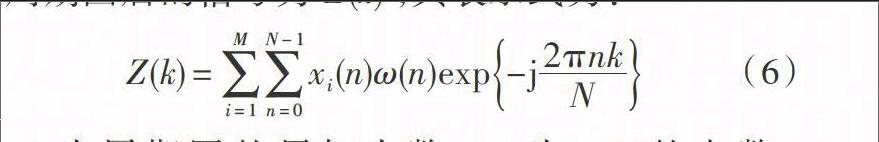

采用周期图方法,通过对多次FFT的结果进行累加,以实现极低信噪比的载波频率鉴频。

设周期图后的信号为[Z(k)],其表示式为:

[Z(k)=i=1Mn=0N-1xi(n)ω(n)exp-j2πnkN] (6)

式中:[M]为周期图的累加次数;[N]为FFT的点数;[xi(n)=x(n+iγ)];[x(n)]为[x(t)]的采样信号;[γ]为计算周期图时每次FFT的更新样点数;[ω(n)]为作周期图时的加权系数。

图2信噪比为-30 dB时不同[M]时的仿真结果,输入载波频率为2.25 MHz。可以看出,在低载噪比时,由于噪声的均值为0,可通过增大周期图参数[M,]来对噪声进行平均,使载波频率更突出,从而提高鉴频的信噪比。可通过增大周期图参数[M,]以满足低信噪比对鉴频的要求。

3 环路带宽的自适应控制策略

对于高动态下信标信号的载波捕获跟踪问题,可将环路工作分为载波捕获阶段和载波跟踪阶段。在捕获阶段时,由于信号的载波频率变化较快,环路将滤波器的带宽设置较大,以达到捕获信号的目的。当完成载波捕获后,环路将转入跟踪阶段,为了提高环路输出信号的精度,环路将滤波器的带宽将设置较小。因此,为了使环路适应高动态的输入信号频率及不同的工作状态,需要根据环路的工作状态对环路滤波器的带宽进行自适应地控制。

图2 不同M取值下的周期图结果

图3为基于自适应参数控制的FLL原理框图,其通过对环路滤波器输出值的均值和方差进行监测,来自适应地控制阻尼因子[ζ]的大小,达到自适应调整环路滤波器带宽的目的,同时达到对高动态下的信标信号进行载波捕获和跟踪的目的。

图3 基于自适应参数控制的FLL

影响环路滤波器的参数主要是滤波器的固有频率[ωn]和阻尼因子[ζ],改变环路滤波器的带宽则可通过改变阻尼因子[ζ]的大小实现。

当阻尼因子[ζ]在一定范围内,环路可收敛,此时环路滤波器可工作在过阻尼和欠阻尼两种状态。当工作在过阻尼状态时,经过环路滤波器的频率偏差值从一个方向收敛到0;当工作在欠阻尼状态时,经过环路滤波器的频率偏差值通过振荡收敛到0。

当阻尼因子[ζ]超出使环路收敛的范围时,系统都不能工作在稳定状态。当阻尼因子[ζ]太小时,环路滤波器输出的频率偏差值一直处于较大的状态,无法跟上信号频率变化,即此时输出值的均值较大,环路无法锁定;当阻尼因子[ζ]太大时,环路滤波器输出的频率偏差值振荡太大,大于信号的频率变化量,即此时输出值的方差较大,环路仍无法锁定。

因此可通过对环路输出值的均值和方差进行监测来自适应地控制阻尼因子[ζ]的大小。在一定时间内,若环路滤波器的输出均值过大、方差较小时,说明此时环路的阻尼因子[ζ]过小,需要将阻尼因子[ζ]调大;若环路滤器的输出均值较大、方差较大且经过一定时间仍不减小时,说明此时环路的阻尼因子[ζ]过大,需要将阻尼因子[ζ]调小;若环路滤器的输出均值和方差均较大时,说明环路正在锁定过程中,不需要调整阻尼因子[ζ];若环路滤器的输出均值和方差均较小时,说明环路已经锁定,阻尼因子[ζ]大小适中,不需要进行调整。

4 设计与实现

采用基于FPGA的通用信号处理板卡设计并实现图1所示的实验方案,信号处理板由2片XC6VLX240T和1片XC5VSX95T构成,XC5VSX95T负责与计算机通过USB接口通信、产生模拟高动态的信标信号。

信号参数通过基于USB接口控制的模拟高动态信标信号源进行设置,软件操作界面如图4所示。控制软件由“信号参数”和“调试参数”两部分组成,“信号参数”用于设置遥测信号的动态参数,包括多普勒频率及其一阶和二阶变化率。“多普勒频率”可设置的频率范围为 0~2 000 kHz;“一阶变化率”为多普勒频率的一阶变化率,可设置的范围为0~200 kHz/s;“二阶变化率”为多普勒频率的二阶变化率,可设置的范围为0~30 kHz/s2。“调试参数”用于设置遥测信号的调制样式、目标飞行器的水平和俯仰角度、接收通道中采用的调制信号频率、环路滤波器参数及解调时的相位延迟。“Mode_sel”用于设置遥测信号的调制方式,可设置参数为0~2;“Uh”和“Uv”为目标飞行器的水平和俯仰角度,“mu”为采用单音或调制信号;“FLL1”、“FLL2”和“PLL”为环路滤波器参数;“延迟”为相位延迟参数,范围为0~31。当系统参数确定后,可点击“设置”将参数传输至FPGA设置信号参数。实验中的多普勒频偏设置为2 MHz,一阶变化率设为200 kHz/s,接收时为了通过一个通道传输俯仰和水平信息,需要加入调制信号,实验时采用1 kHz的方波信号,信道噪声通过外接噪声源直接从信道加入,输入信噪比为-20 dB。图5给出了第一级FLL调试结果的输出信号,系统的采样率为40 MHz,进行正交下变频后,第一次降采样倍数为8,采样率降为5 MHz,FFT点数[N=2 048],此时的频率分辨率为[5 MHz2 048]=2.44 kHz,即可将输出的残留载波频率偏差控制在2.44 kHz以内。图6给出了第二级FLL输出波形及PLL输出结果,此时的数据速率约为40 kHz,第二级FLL中的FFT点数设为1 024,可将输出的残留载波频率偏差控制在[40 kHz1 024]= 39 Hz以内,图中的红色线为第二级FLL的输出信号,蓝色线为PLL锁相环的VCO输出信号,绿色线为经过PLL后的输出信号,可以直接用于俯仰、方位信息的解调。

5 结 语

设计并实现了基于两级二阶FLL和一级三阶PLL的信标信号载波捕获与跟踪,同时满足输入信噪比低、多普勒频率及其变化率大等条件,可直接应用于高机动平台的角跟踪系统。

参考文献

[1] 程乃平,任宇飞,吕金飞.高动态扩频信号的载波跟踪技术的研究[J].电子学报,2003,31(12):2147?2150.

[2] 王兰芳,吴长奇.基于FLL与PLL级联的高动态载波跟踪技术[J].电子测量技术,2009,34(3):25?27.

[3] 王俊,吴土成,孟耘.高动态环境中频数字接收机载波同步研究[J].通信技术,2010,43(1):66?68.

[4] 班华福,王世练,朱江.高动态信标信号的数字FLL技术研究[J].通信技术,2011,44(7):19?24.

[5] 卢辉斌,王伟伟,谷青川.低信噪比高动态条件下的载波同步技术[J].信息与控制,2010,39(4):451?454.

[6] 赵琳,高帅和,丁继成.基于FFT的高动态 GPS信号捕获方法优化[J].系统工程与电子技术,2011,33(1):151?156.

[7] 罗大成,王仕成,王明福.载波跟踪算法综述[J].系统仿真学报,2008,20(22):6023?6028.