Flash型FPGA的单粒子效应测试系统研制

2015-07-07王忠明闫逸华陈荣梅王园明张凤祁郭晓强郭红霞

王忠明,闫逸华,陈荣梅,王园明,赵 雯,张凤祁,郭晓强,郭红霞

(西北核技术研究所强脉冲辐射环境模拟与效应国家重点实验室,陕西西安 710024)

Flash型FPGA的单粒子效应测试系统研制

王忠明,闫逸华,陈荣梅,王园明,赵 雯,张凤祁,郭晓强,郭红霞

(西北核技术研究所强脉冲辐射环境模拟与效应国家重点实验室,陕西西安 710024)

研制了一套Flash型FPGA的单粒子效应测试系统,其具有片上SRAM/Flash ROM单粒子翻转效应测试、D触发器单粒子效应测试、锁相环与时钟网络单粒子瞬态效应测试、单粒子瞬态脉冲宽度测试等功能。本文介绍了该系统的测试原理和软硬件实现方法。

单粒子效应;Flash型FPGA;单粒子瞬态

现场可编程门阵列(FPGA)是一种大规模集成电路,它具有逻辑密度高、设计灵活、成本低廉等优势,在商用和航天等领域均取得了巨大成功。其中,Flash型FPGA在过去几年中取得了很大的发展,在性能和成本上已具备很强的竞争力,可作为空间电子学系统的一种备选方案。但在将其用于空间应用之前,必须对其抗辐射能力进行充分的考察和研究。由于Flash型FPGA出现至今仅10年时间,有关这种新型器件的辐射效应研究亦处于起步阶段[14],国内抗辐射加固领域对这种器件的研究尚未见公开报道。本文研制一套针对Flash型FPGA单粒子效应的在线测试系统,以全面、准确地反映Flash型FPGA的各类辐射失效现象,为深入开展针对Flash型FPGA的单粒子效应的相关研究奠定基础。

1 效应机理分析

Flash型FPGA由可编程逻辑单元、可编程互连资源、可编程I/O模块、片上SRAM、片上Flash ROM等结构组成。其中,逻辑单元称为VersaTile,每个Versa Tile包括一系列CMOS组合逻辑及与之对应的Flash开关,通过改变Flash开关的状态可将1个Versa Tile配置成n输入的组合逻辑。此外,Versa Tile中还包括1个或多个可选的D触发器结构。Flash开关采用浮栅技术来保存开关的状态,1个浮栅开关由两个共用浮栅和控制栅的MOSFET组成,其中一个MOS管通过位选信号控制浮栅上的电子,从而实现编程、擦除和校验等功能,而另外一个MOS管则作为互联开关使用,如图1所示。

根据以往对SRAM型FPGA和Flash ROM等器件的研究经验[5-7],可初步判断Flash型FPGA中可能发生单粒子翻转(SEU)效应的结构至少应包括:片上SRAM和D触发器。较易受单粒子瞬态(SET)效应干扰的结构包括:组合逻辑(最终表现为D触发器翻转)、锁相环(PLL)和时钟网络等。SET效应的初始脉冲宽度是确定SET效应捕获概率及加固方法的关键参数,若系统能兼顾SET脉冲宽度的测试,就可更好地对单粒子瞬态效应进行评估。因此,Flash型FPGA的单粒子效应测试系统主要功能应包括:SRAM/Flash ROM的单粒子翻转效应测试、逻辑单元D触发器的单粒子效应测试、锁相环和时钟网络的单粒子瞬态效应测试、单粒子瞬态脉冲宽度的测试、单粒子锁定效应测试及保护等。

2 系统的测试原理

2.1 SRAM/Flash ROM的单粒子翻转效应测试

SRAM是典型的易发生单粒子翻转的结构,其测试方法与一般的SRAM存储器测试方法类似,向片上SRAM写入指定格式的数据(如55H、AAH),间隔一段时间回读一次,比较与写入数据的异同,判断单粒子翻转效应是否发生。Flash ROM的测试方法与SRAM类似。

2.2 D触发器的单粒子效应测试

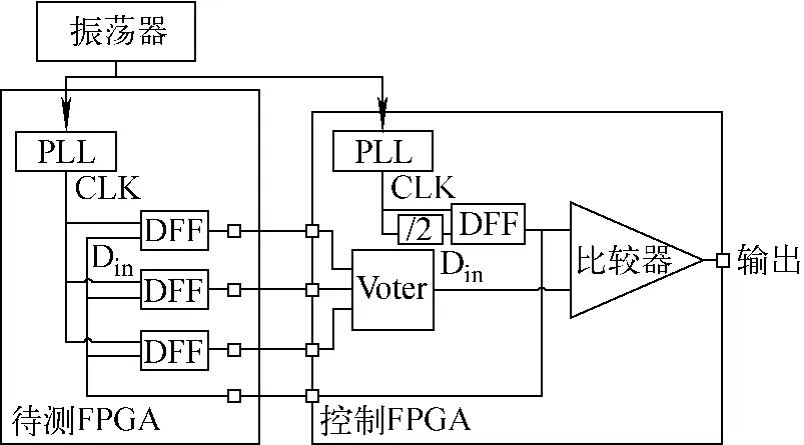

D触发器电路对单粒子效应的响应主要表现为输出信号的翻转,采用的测试方法如图2所示。将待测FPGA配置成一个由若干触发器组成的移位寄存器链,令移位寄存器链的输入端Din保持低电平,在正常情况下输出端Dout皆为低电平。触发器链上任意一点捕获到单粒子瞬态脉冲信号,经一定的时钟周期后最终均将出现在Dout端。这样,只要统计监测到的高电平信号的数量就可得到触发器单粒子事件的截面。

2.3 锁相环及时钟网络的单粒子瞬态效应测试

图1 Flash型FPGA的结构Fig.1 Architecture of Flash-based FPGA

锁相环是一种利用反馈控制原理实现的频率及相位的同步技术。对锁相环及时钟网络的单粒子瞬态效应采用间接测量方法。利用锁相环作为芯片间的同步时钟信号去驱动相同输入的触发器(图3),若待测FPGA芯片(DUT)的锁相环受到单粒子瞬态效应的干扰,则触发器的输出会与正常状态下的不同,通过比较待测FPGA与参照FPGA中触发器的输出信号就可统计锁相环及时钟网络发生单粒子瞬态的次数。为排除待测芯片中D触发器的单粒子效应,在DUT中对PLL驱动的D触发器进行了三模冗余(TMR)加固。

图2 D触发器测试方法Fig.2 Test method for D-flip flop

图3 锁相环及时钟网络的单粒子瞬态测试电路Fig.3 Single-event transient effect test circuit for PLL and clock network

2.4 单粒子瞬态脉冲宽度测试

集成电路内部的SET信号不能通过示波器直接测量,完整的信号测量具有较大的难度。本文在待测FPGA内部设计一个测试电路,采用间接方法测量SET的脉冲宽度,其电路结构如图4所示。在反相器链的偶数节点引出测试端,与最终输出端经过一个保护门后,连接到I/O端口上。保护门在两输入一致时为与,在两输入不一致时,锁存上一状态。反相器链输入端接地,在正常状态下,所有的输出结果都是0。

图4 单粒子瞬态脉冲宽度测试电路Fig.4 SET pulse width test method

当SET发生在反相器链的某一节点时,信号将沿反相器链传播至最终的输出端。这个SET信号将进入每个保护门的一个输入端,即最后一个反相器的输出端。但由于反相器链自身的延迟,进入保护门另一个输入端的信号与到达最后一个反相器输出端的SET信号之间会存在一定的延时。如果延时不超过瞬态脉冲的宽度,则该保护门输出为1;如果延迟时间超过了SET宽度,则保护门的输出为0。这样,通过输出端为1的个数就可判断该瞬态脉冲的宽度等于几个反相器的延迟。

2.5 单粒子锁定效应测试

采用高端测电流方案,在电源端串联一小电阻,采集电阻两端电压,用A/D转换为数字信号进行采集。系统的电流监测电路主要分为放大、监测、闭锁保护3部分。当电流实测值大于设定阈值时,关断电源端继电器,从而使器件断电。当关断时间到达设定值时,打开继电器,被测器件上电,继续进行后续测试。

3 测试系统软硬件设计

3.1 测试系统硬件设计

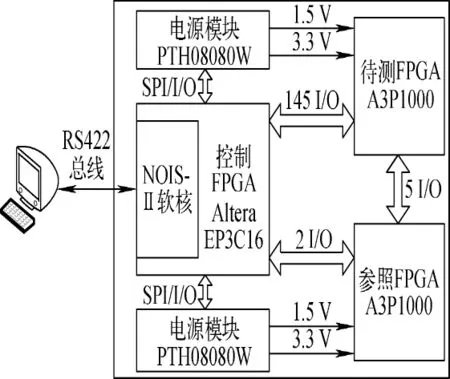

系统硬件设计方案如图5所示,主要由控制FPGA、待测FPGA、参照FPGA及相关外围电路组成。控制FPGA是整个系统的核心,通过SPI及I/O接口实现对待测FPGA、参照FPGA的功耗电流测量;通过通用I/O与待测FPGA、参照FPGA进行通信,实现各项逻辑测试;通过NOIS-Ⅱ软核和RS422接口实现与PC机的通信。综合考虑各项测试需求,选定Altera EP3C16为控制FPGA芯片。待测FPGA与参照FPGA只实现内部相关测试逻辑,采用Actel公司的Pro ASIC3系列芯片A3P1000,只需提供核心电压1.5 V,外部I/O电压3.3 V,剩余管脚为通用I/O,与控制FPGA相连即可。

3.2 测试系统软件设计

软件包括待测FPGA程序、参照FPGA程序、控制FPGA程序及上位机控制程序。待测FPGA程序包括5项功能:SRAM读写测试、Flash ROM回读测试、D触发器链的SET效应测试、SET脉冲宽度测试及PLL的SET测试。参照FPGA主要参与完成PLL的SET测试。控制FPGA程序实现:控制FPGA PLL时钟生成,待测FPGA和参照FPGA的频率控制、功耗电流测试和电流关断,待测FPGA SRAM的读写,Flash ROM的读取,DFF SET效应计数,SET脉宽测试和PLL测试及其错误类型的检测。上位机软件主要完成测试初始化及效应结果显示保存等功能。

图5 系统硬件设计方案Fig.5 Hardware design scheme of test system

4 系统功能测试

4.1 实验室测试

在本文中,SET脉冲宽度需用FPGA内部反相器链自身的延时来表示,因此必须知道每级反相器链的延时。本工作在A3P1000内设计了100级反相器,分别在10级的整数倍引出测试端,用示波器测得10级反相器的平均延迟为5.02 ns。由此可得,本方法测量SET脉冲宽度的精度约为1 ns(即两级反相器的延时)。据文献[8]报道,0.13μm工艺的CMOS器件中,单粒子瞬态电流的脉冲宽度通常在几ns至十几ns,因此该精度是可接受的。

一些研究[9]表明,反相器链对SET脉冲存在展宽/压缩效应,这种效应对测量SET脉冲宽度存在影响。经实测分析,平均每级反相器产生的脉冲展宽约为4 ps。在本文SET脉宽测试中共设计100级反相器链,假设SET平均经过50级反相器传播到输出端,此时SET脉冲平均展宽为0.2 ns,相对本方法的测试精度1 ns和平均几ns~十几ns的SET脉宽,该展宽是可接受的。

此外,本文还设计了一套测试方法,在100级反相器链输入端分别产生一个宽度为3、5、7 ns的脉冲信号,测得保护门输出为1的个数分别为3、5、7,从而验证了SET脉冲宽度测试功能的有效性。

4.2252Cf源辐照实验测试

为进一步验证系统功能,在252Cf源上开展一次单粒子效应实验。252Cf是一种不稳定核素,自发衰变产生α粒子、裂变碎片和中子。利用252Cf源产生的重离子碎片可产生单粒子效应,常用于单粒子效应测试系统调试。将去除表面封装的待测器件对准源孔,置于真空腔体内。真空度达到几十Pa时,重离子即可入射至芯片表面。图6为252Cf源单粒子效应实验装置和测试系统计算机控制界面。

实验进行24 h,实验结果列于表1。其中,Flash ROM、PLL与时钟网络及SET脉冲宽度测试未观察到单粒子效应,可能是由于252Cf源粒子注量率太低、穿透能力较差[10]、测试本身资源占用率低、粒子打在敏感位置上的概率过低等原因所致。只有在基于加速器的辐射模拟源上开展相关实验才能彻底解决上述问题。

图6252Cf源单粒子效应实验装置(a)和测试系统计算机控制界面(b)Fig.6252Cf single-event effect test facility(a)and control GUI of test system(b)

表1252Cf源辐照实验结果Table 1252Cf irradiation test result

5 结论

本文建立的针对Flash型FPGA的单粒子效应在线测试系统具备SRAM/Flash ROM单粒子翻转效应测试、D触发器单粒子效应测试、PLL及时钟网络单粒子瞬态效应测试、单粒子瞬态脉冲宽度测试、单粒子锁定效应测试等功能,较全面地覆盖了Flash型FPGA中各种可能的单粒子效应失效模式。实验室及252Cf源单粒子效应实验结果验证了系统功能的有效性,为开展针对Flash型FPGA的单粒子效应研究提供了测试手段。

[1]REZGUI S.Radiation-tolerant Pro ASIC3 FPGAs radiation effects[R].Mountain View:Actel Corporation,2010.

[2]REZGUI S,WILCOX E P,LEE P,et al.Investigation of low dose rate and bias conditions on the total dose tolerance of a CMOS flash-based FPGA[J].IEEE Transactions on Nuclear Science,2012,59(1):134-143.

[3]TARRILLO J,AZAMBUJA J R,KASTENSMIDT F L.Analyzing the effects of TID in an embedded system running in a flash-based FPGA[J].IEEE Transactions on Nuclear Science,2011,58(6):2 855-2 862.

[4]KASTENSMIDT F L,FONSECA E C P,VAZ R G.TID in flash-based FPGA:Power supplycurrent rise and logic function mapping effects in propagation-delay degradation[J].IEEE Transactions on Nuclear Science,2011,58(4):1 927-1 934.

[5]姚志斌,何宝平,张凤祁,等.静态随机访问存储器型现场可编程门阵列辐照效应测试系统研制[J].强激光与粒子束,2009,21(5):749-754.YAO Zhibin,HE Baoping,ZHANG Fengqi,et al.Development of measurement system for radiation effect on static random access memory based field programmable gate array[J].High Power Laser and Particle Beams,2009,21(5):749-754(in Chinese).

[6]王忠明,姚志斌,郭红霞,等.SRAM型FPGA的静态与动态单粒子效应试验[J].原子能科学技术,2011,45(12):1 506-1 510.WANG Zhongming,YAO Zhibin,GUO Hongxia,et al.Static and dynamic tests of single-event effect in SRAM-based FPGA[J].Atomic Energy Science and Technology,2011,45(12):1 506-1 510(in Chinese).

[7]张洪伟,于庆奎,张大宇,等.大容量Flash存储器空间辐射效应试验研究[J].航天器工程,2011,20(6):130-134.ZHANG Hongwei,YU Qingkui,ZHANG Dayu,et al.Radiation effect test on large capacity Flash memories[J].Spacecraft Engineering,2011,20(6):130-134(in Chinese).

[8]VRONIQUE F C,LLOYD W M,GOUKER P.Single event transients in digital CMOS:A review[J].IEEE Transactions on Nuclear Science,2013,60(6):1 767-1 790.

[9]赵雯.基于查找表的SET耦合注入与SET传播特性研究[D].西安:西北核技术研究所,2011.

[10]范雪,李平,李威,等.252Cf源和重离子加速器对FPGA的单粒子效应[J].强激光与粒子束,2011,23(8):2 229-2 233.FAN Xue,LI Ping,LI Wei,et al.Single event effects on FPGA of califormium-252 and heavyion accelerator[J].High Power Laser and Particle Beams,2011,23(8):2 229-2 233(in Chinese).

Development of Single-event Effect Test System for Flash-based FPGA

WANG Zhong-ming,YAN Yi-hua,CHEN Rong-mei,WANG Yuan-ming,ZHAO Wen,ZHANG Feng-qi,GUO Xiao-qiang,GUO Hong-xia

(State Key Laboratory of Intense Pulsed Radiation Simulation and Effect,Northwest Institute of Nuclear Technology,Xi’an 710024,China)

A single-event effect test system for Flash-based FPGA was developed.The system can be used for SRAM/Flash ROM single-event upset effect test,D-flip flop single-event effect test,PLL and clock network single-event transient effect test,and single-event transient pulse width test.The test methods and hardware/software solutions were described in this paper.

single-event effect;Flash-based FPGA;single-event transient

TN386.1

:A

:1000-6931(2015)12-2266-06

10.7538/yzk.2015.49.12.2266

2014-08-20;

:2015-01-10

王忠明(1984—),男,内蒙古呼伦贝尔人,副研究员,博士,从事大规模集成电路的单粒子效应研究