数字控制谐振变换器高轻载效率的研究

2015-02-22史永胜高丹阳李晓明

史永胜, 高丹阳, 李晓明, 胡 双

(1.陕西科技大学 理学院, 陕西 西安 710021; 2.陕西科技大学 电气与信息工程学院, 陕西 西安 710021)

数字控制谐振变换器高轻载效率的研究

史永胜1, 高丹阳2, 李晓明2, 胡双2

(1.陕西科技大学 理学院, 陕西 西安710021; 2.陕西科技大学 电气与信息工程学院, 陕西 西安710021)

摘要:针对传统模拟电源在轻载时损耗较大、效率较低的缺陷,提出了一种基于DSP的PI控制的数字电源设计方法.通过对谐振变换器工作原理、Burst模式工作原理和增益特性曲线等的分析,设置了最佳死区时间,提出了数字控制的Burst模式控制策略,可有效改变轻载模式下的开关频率,从而使得谐振变换器在轻载时也能够实现ZVS,并减少了变换器关断和传输损耗.实验结果表明:设置合理死区时间的变换器在小于5%额定负载时,其效率能达到87%以上;在5%~20%额定负载时,能够保持93%及以上的效率.Burst控制策略下谐振变换器的有效性和可行性通过仿真和样机实验得到了验证.

关键词:LLC半桥谐振变换器; 轻载效率; 死区时间; 数字信号处理器(DSP)

0引言

近年来,随着云计算和大数据时代的到来,服务器电源和个人计算机电源需要更高的可靠性和稳定性[1,2].传统的模拟电源在满载时都能高效工作,而在轻载时却效率较低很难保证最佳工作状态[3,4].针对这一情况,数字控制电源被广泛应用,其集成度已达到很高水平[5],而且其系统的复杂性并不随功能的增加而增加,外围器件很少;同时,数字电源还具有高灵活性、在线可编程能力以及更易于实现非线性控制能力[6].因此,其轻载效率较模拟电源有了很大改善和提高.

许多具备软开关能力的直流变换器拓扑被应用到数字电源的研究中,以减少开关和传输损耗、降低电磁干扰,从而提高功率器件的转换效率.LLC谐振变换器因其具有自然软开关特性,被作为数字电源的拓扑结构进行了分析与设计.

文献[7,8]提出的LLC谐振变换器PWM控制策略,是对占空比进行调节,没有特别针对轻载模式控制,因而不能有效改善轻载模式下变换器的工作频率和效率;文献[9,10]提出的变换器的PFM控制,尽管能够改变变换器的频率,但并没有对其轻载模式状态进行研究,没有实现真正意义上的高轻载效率.

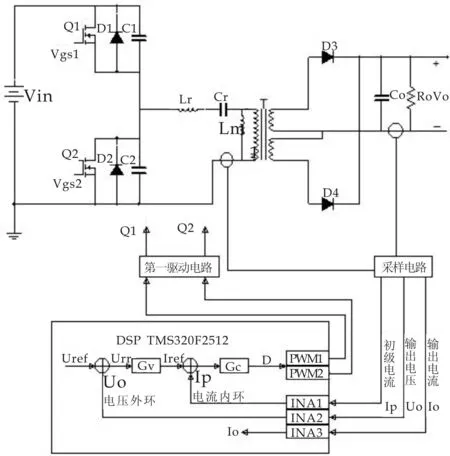

本文研究的数字控制谐振变换器如图1所示.首先分析了谐振变换器在数字控制下的工作原理和增益特性,然后根据数字控制时能量传输随开关频率变化的特性,提出了一种基于DSP控制的Burst模式控制策略;并在Burst模式期间设置合适的死区时间,即轻载时采用Burst模式数字控制策略控制开关管的占空比.在两个开关管交替导通期间设置合适的死区时间,可使开关频率逐渐减小、开关周期次数减少、开关损耗减小,从而在轻载时得到较高效率.最后,通过一台300 W的实验样机验证了所提控制方法的正确性和有效性[11,12].

1LLC谐振变换器的工作原理

1.1 变换器重载及轻载时的工作原理

图1是本文设计的基于TMS320F2812的高轻载效率数字DC/DC变换器的硬件结构图.由图1可知,Q1、Q2是两个主功率开关管,D3、D4是整流二级管,Lr是谐振电感,Cr是谐振电容,Lm是励磁电感,T1是主变压器,C1、C2分别为Q1、Q2的寄生电容,D1、D2分别为Q1、Q2的寄生二极管.

图1 数字LLC谐振DC/DC变换器的硬件结构图

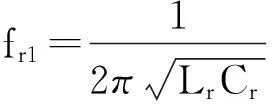

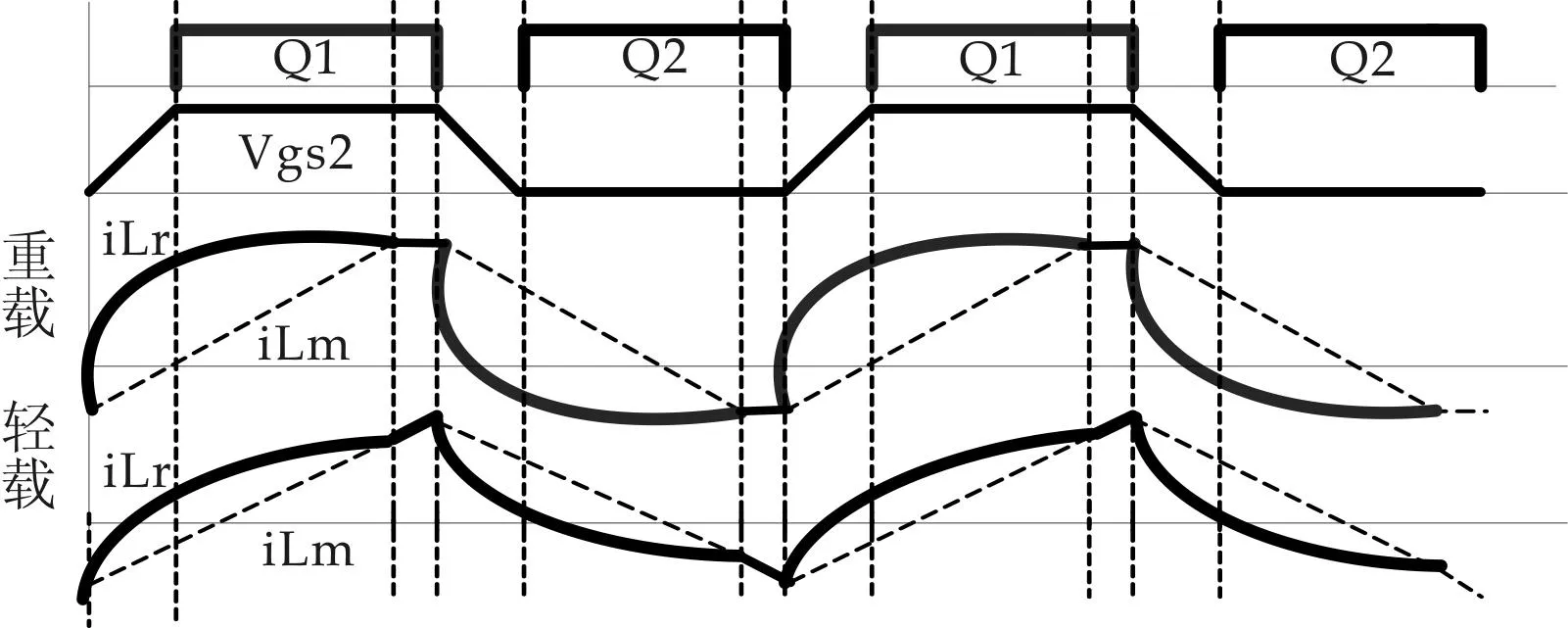

(1)

(2)

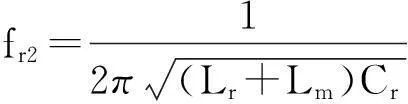

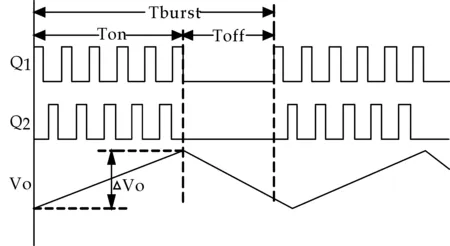

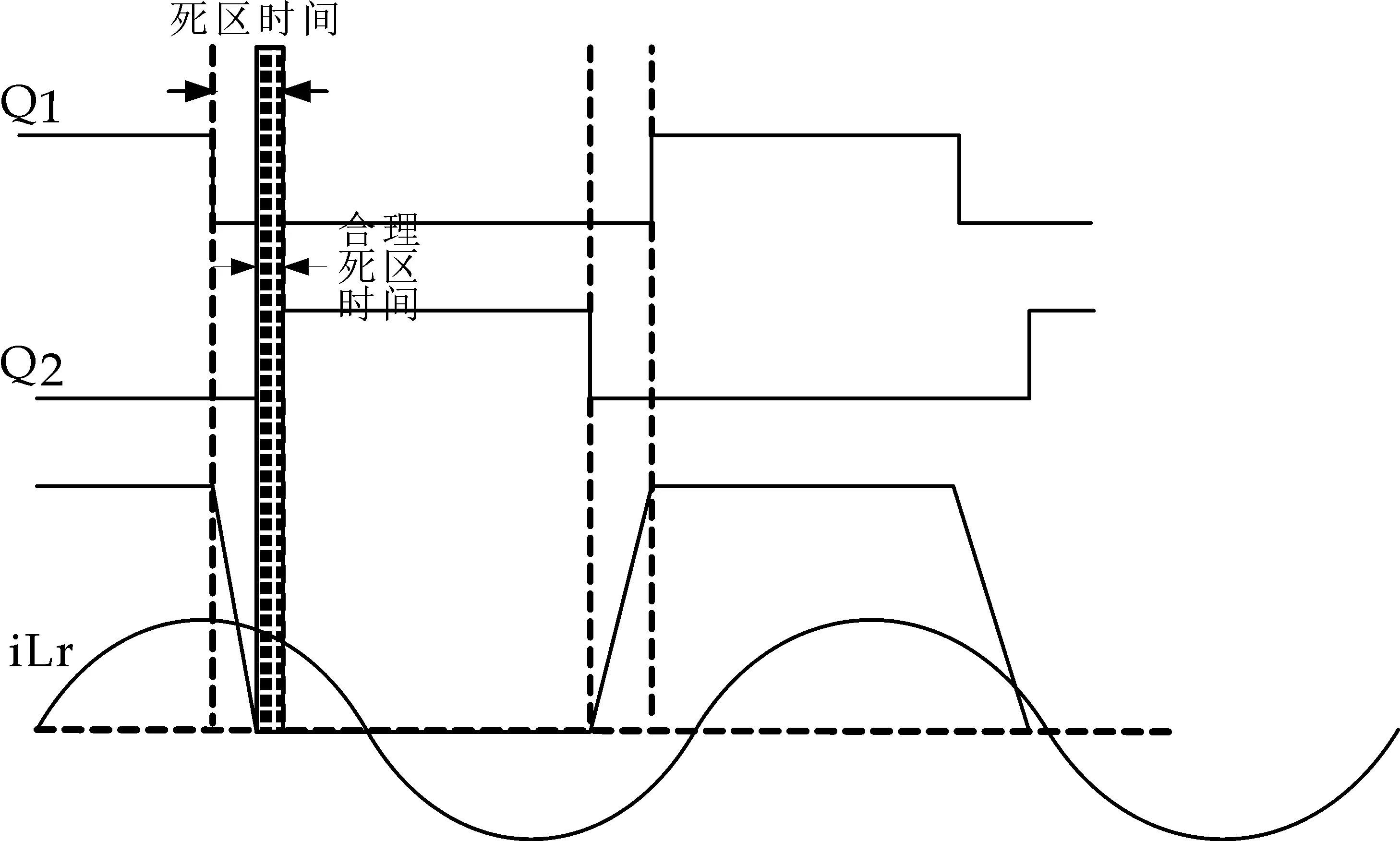

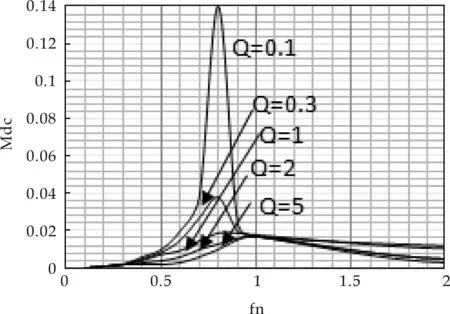

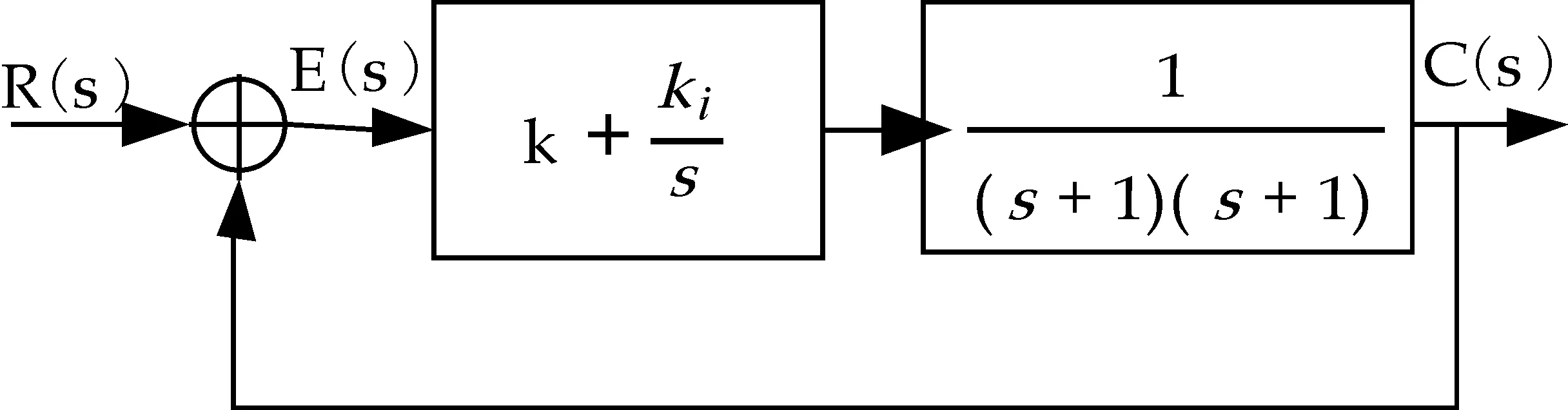

当谐振变换器工作在fr1 当变换器谐振工作时,Lr、Cr和Lm形成谐振腔,为Q1、Q2的开通关断制造ZVS条件,ZVS的开通时间Td要大于两开关管之间的死区时间Tdead,ZVS的实现和合理的死区时间有效地减少了主功率开关管的开断损耗,从而提高了变换器的转换效率. 通过控制半桥LLC谐振电路中Q1、Q2的占空比可控制能量传输、调节电压输出.当谐振变换器带重载(20%~100%额定负载)时,由图2可知,iLr和iLm之间能量之差较大,此能量将通过T1向副边传输;当谐振变换器带轻载(20%额定负载下)时,由图2可知,iLr和iLm之间的能量之差相比于带重载时较小,故向副边传输的能量变少[13,14]. 图2 重载和轻载情况下开关管的驱动信号以及主要工作电流波形 图3是Burst模式的工作原理图.当检测到输出电流在额定电流的20%以下时,主程序进入Burst模式,并且变换器进入间歇式工作,一些开关周期是在近似固定频率下工作,且由一些无效的周期间隔开,两个MOSFET功率开关管在Toff时都处在关闭状态,随着负载进一步减小,会进入更长的无效周期,以减小平均开关频率. 由图4可知,Q1和Q2呈180 °互补导通,死区时间处于Q1关断和Q2开通期间,Tdead 图3 Burst模式下的工作电压波形 图4 合理死区时间的设定 2LLC谐振变换器的特性分析 影响直流增益的参数有比例系数K、串联谐振品质因数Q、变压器匝比n等[12].各参数之间相互影响,所以在分析电路特性时,先固定一个参数,再改变其它几个参数. 首先,分析K对变换器的影响.固定Q和n,在图5中,令Q=0.2、n=31、fn=f/fr1.由图5可知,随着K的增大,电路的最大增益是减小的,如果一直增大K值,输出电压将不稳定、工作频率范围将变大,这对磁性元件有损害;如果减小K的取值,Lm将减小,从而损耗励磁电感.综上可知,K的取值应合理选取.根据经验,一般选择K的值为2.5~6. 其次,分析Q对变换器的影响.在图6中,令K=0.5、n=31.由图6可知,随着Q值的增大,最大增益减小.变压器空载增益达到最大,此时需增加开关频率;变压器满载时增益最小,此时需减小开关频率.根据上文可知,当开关频率fr1 图5 K对变换器的影响 图6 Q对变换器的影响 3LLC谐振变换器Burst模式系统的设计 系统硬件结构如图1所示.通过采样电路以及AD转换器将三路信号(变压器初级侧电流Ip、输出电流Io以及输出电压Uo)采样并送入DSP2812.其中,DSP内部的INA1、INA2、INA3端口分别对Ip、Uo和Io采样.系统采用电压电流双闭环控制,输出PWM驱动信号.DSP内部的PWM1、PWM2端口输出死区固定、占空比大小固定等驱动信号,通过驱动电路来驱动主功率开关管Q1、Q2. 本文所设计变换器的系统参数如下:谐振电感Lr=40μH;谐振电容Cr=33 nF;励磁电感Lm=285μH;变压器变比n=50∶7;开关频率fs=100 KHz;谐振频率fr=85 KHz;死区时间Tdead=340 ns、350 ns、 370 ns、 400 ns,设置多个死区时间的目的是找出最佳死区时间,以提高变换器的传输效率. 本文的DC/DC谐振变换器采用峰值电流控制,如图7所示.即双环控制,其中电压为外环,电流为内环.输出电压U0与电压基准值Uref比较产生误差电压Uerr,经过调节器GV形成电压外环控制;变压器初级侧电流Ip与基准值电流Iref比较形成误差电流Ierr,经过调节器GC形成电流内环控制,电流内环输出为有效占空比,根据占空比信号产生PWM信号[15]. 图7 双环控制结构框图 DSP的数据都是通过采样得到,因此,要想在计算机中实现系统的模拟PI控制,就必须对模拟PI控制器做离散化处理,变成数字控制器.在本文中,采取增量式PI,此法相比于位置式PI,可以消除控制器的积分饱和,容易达到较好的控制效果;而且此算法所用的执行器具有保持功能,执行器能够保持在原位,即使计算器发生故障也不会受到影响. 增量式PI算法,即数字控制器输出的是相邻两次采样时刻所计算的位置值之差. u(k)=u(k-1)+Δu(k) (3) Δu(k)=kp[e(k)-e(k-1)]+kie(k) (4) 由图8可知,系统的开环和闭环传递函数,通过仿真软件分析系统的稳态和动态性能,确定比例积分系数.在此分别取k=0、ki=5;k=10、ki=5;k=20、ki=5等值,以求取系统的特征根.当k=10、ki=5时,系统的超调量减少,系统反应速度较灵敏,PI控制器对系统的稳定性、暂态性等的影响减少. 图8 PI控制器的系统结构图 增量式控制算法有效地减小了累计误差.通过此种算法控制PWM驱动信号,以完成对控制器的控制,需要先设置控制参数Kp、Ki以及偏差初值,再根据采样值计算当前偏差值e(k),然后计算增量Δ(u)(k),利用这个增量调用占空比子程序计算电流环,最终把偏差量转化为占空比信息量. 本文根据变换器系统的硬件条件将采样频率调到极限值,提高了系统尤其是在轻载时的控制性能;运用极点配置方法整定PI的比例、积分系数;并通过Saber仿真修订参数,使得变换器在轻载时达到良好的控制效果.由Saber仿真得到:整定参数Kp=2.03、Ki=23 075. 本文分别对主程序、中断程序和PI算法程序进行了设计,整个程序运行良好,基本达到预期设计要求.如图9所示,主程序中首先进行系统配置及初始化,然后初始化ADC、PWM及PI控制模块参数,并且在等待中断的时间内采集输出电压,如果发生ADC中断则进入相应的流程[16,17].实际编写程序时采用改进型PI算法,设置好比例积分增益,计算输出电压偏差ΔU(k),更新PI运算变量,程序设计中CPU时钟频率设为50 MHz,ADC模块每10 ms采样一次. (a)主程序流程图(b)中断服务流程图(c)PI控制流程图图9 程序流程图 4实验与分析 为了验证本文设计的合理性,首先利用参数对电路进行仿真,仿真实验以Saber为平台,对半桥谐振电路轻载和空载情况进行了研究分析.主要实验参数设计如下:谐振电感Lr=40μH,谐振电容Cr=33 nF,励磁电感Lm=285μH,变压器变比n=50∶7,开关频率fs=100 KHz,谐振频率fr=85 KHz,最佳死区时间Tdead=340 ns、350 ns、370 ns、400 ns. 空载是谐振半桥电路工作时比轻载更恶劣的一种情况,在此状态下,由图10波形可知,此谐振变换器能够实现ZVS,并且在空载时iLr和iLm之差较稳定,原边能向副边稳定传输能量,并且输出电压基本达到24 V.这说明参数设计较合理,能够实现谐振,实现软开关,仿真电路工作正常. 图10 空载半桥谐振电路波形 本文为了验证轻载情况下LLC谐振变换器能够稳定工作并且具有较高的效率,设计了一款额定功率为300 W左右的试验样机. 图11为Q2零电压开通时各极间电压波形.由图11波形可知,此半桥谐振变换器能够在死区时间为340 ns的空载情况下,实现原边开关管的ZVS.ZVS有效地减小了开通关断时的损耗,有助于变换器效率的提高. 图11 Q2栅源极间零电压开通 图12为轻载情况下Burst模式控制的效率对比.当所设计变换器在系统固有死区时间(200 ns)下运行时,最低效率为75%、最高效率为94%;当变换器工作在合理死区时间(340 ns)时,最低效率为86%、最高效率达到96%. 合理的死区时间设置能够有效减少传输损耗,提高轻载效率.合理死区时间下的效率要比固定死区时间下的效率平均高出最少1%~2%的裕度.原因在于数字控制的LLC谐振变换器在轻载时也能够实现软开关技术,减少了开断损耗,而且合理的死区时间将会减少谐振电流的振荡,从而减少了传输损耗. 图12 不同死区时间轻载效率对比 5结论 本文对谐振变换器轻载效率进行了研究,提出了一种基于DSP的PI数字控制方法.此方法要求变换器在轻载工作情况下能够设置合理的死区时间、能够有效改变开关管的占空比,使开关频率逐渐减小、开关周期次数减少、开关损耗和传输损耗减小,从而在轻载时得到较高效率. 实验结果表明,轻载情况下该Burst模式控制下的拓扑结构简单易控,大大降低了开断损耗,能够较好地实现零电压开通和零电流关断.系统不仅高效还具有很好的稳定性,所以该控制模式下的拓扑具有节能高效的优点,可被广泛应用在机站电源和特种电源中,应用前景十分广阔. 参考文献 [1] Pawellek A,Oeder C,Duerbaum T.Compriison of resonant LLC and LCC converters for low-profile applications[C]//14th Power Electronics and Applications .Birmingham,European:IEEE,2011:1-10. [2] 张久庆,高田,景占荣.基于LLC谐振的LED驱动电源设计[J].电力电子技术,2012,46(3):9-11. [3] Ibrahim Demirel,Burcu Erkemen.A very low-profile dual output LLC resonant converter for LCD/LED tv applications[J].Trans.on Power Electron.,2014,29(7):3 514-3 524. [4] Wensong Yu,Jih Sheng Lai,Wei Han Lai.Hybrid resonant and PWM converter with high efficiency and full soft-switching range[J].Trans.on Power Electron.,2012,27(12):4 925-4 933. [5] Bo Yang.Topology investigation for front end DC/DC power conversion for distributed for distributed power system[D].Blacksburg:Virginia,2003. [6] 余昌斌.LLC谐振半桥DC-DC变换器的研究[D].重庆:重庆大学,2007. [7] Buccella C,Cecati C,Latafat H,et al.Digital control of a haif-bridge LLC resonant converter[C]//15 th Power Electronics and Motion Control Conference.Novi Sad:IEEE,2012:1-6. [8] 阮新波,严仰光.脉宽调制DC/DC全桥变换器的软开关技术[M].北京:科学出版社,1999:21-30. [9] Young Do Kim,Kyu Min Cho,Duk You Kim,et al.Wide-range ZVS phase-shift full-bridge converter with reduced conduction loss caused by circulate ingcurrent[J].Trans.on Power Electron.,2013,28(7):3 308-3 316. [10] 陈亚爱,张卫平.开关变换器控制技术综述[J].电气应用,2008,27(4):5-9. [11] B.C.Kim,K.B.Park,G.W.Moon.Asymme-tric PWM control scheme during hold up time for LLC resonant converter[J].Trans.on Power Electron.,2012,59(7):2 992-2 997. [12] Arikatla,Qahouq V,J A A.DC-DC power converter with digital PID controller[C]// 26th Applied Power Electronics Conference and Exposition.Fort Worth,TX:IEEE,2011:327-330. [13] Beiranvand R,Zolghadri M R,Rashidian B,et al.Optimizing the LLC-LC resonant converter topology for wide output voitage and wide output load applications[J].Trans.on Power Electron.,2011,26(11):3 192-3 204. [14] 唐明明.基于DSP的LLC谐振变换器的研制[D].长沙:中南大学,2009. [15] 周国华,许建平.开关变换器调制与控制技术综述[J].中国电机工程学报,2014,34(6):815-837. [16] In Ho Cho,Young Do Kim,Gun Woo Moon.A half-bridge LLC resonant converter adopting boost PWM control scheme for hold-up[J].Trans.on Power Electron.,2014,29(2):841-850. [17] 程林,陈新,蒋真.基于TMS320F28335的改进型单周期控制实现[J].电力电子技术,2011,45(12):107-108,122. Research of resonant converter based on digital control with high light load efficiency SHI Yong-sheng1, GAO Dan-yang2, LI Xiao-ming2, HU Shuang2 (1.College of Science, Shaanxi University of Science & Technology, Xi′an 710021, China; 2.College of Electrical and Information Engineering, Shaanxi University of Science & Technology, Xi′an 710021, China) Abstract:To solve the disadvantages of traditional anlog power supply loss and less efficient,the scheme of digital PI control based on the DSP is proposed.A new Burst-mode control strategy based on digital control is proposed and adjustable dead time is settled by the principle of LLC resonant converter and Burst-mode and the analysis of gain curves,which can improve the switching frequency at light load condition,ZVS can be achieved,meanwhile,the converter switching and transmission loss is reduced,and the light load efficiency is improved.The resuls show that set the reasonable dead time under 5% load condition,the efficiency reaches 87 percent,and in 5%~20% load condition,the efficiency is higher than 93 percent.The performance of Burst-mode control scheme of LLC converter is verified by simulation and experimental results. Key words:LLC half-bridge resonant converter; light load efficiency; dead time; DSP 作者简介:史永胜(1964-),男,陕西西安人,教授,博士,研究方向:特种电源和先进光电器件 基金项目:陕西省教育厅专项科研计划项目(12JK0494); 陕西科技大学博士科研启动基金项目(BJ08-07) *收稿日期:2015-07-07 中图分类号:TM46 文献标志码:A *文章编号:1000-5811(2015)06-0152-06

1.2 采用Burst模式控制原理

3.1 硬件设计

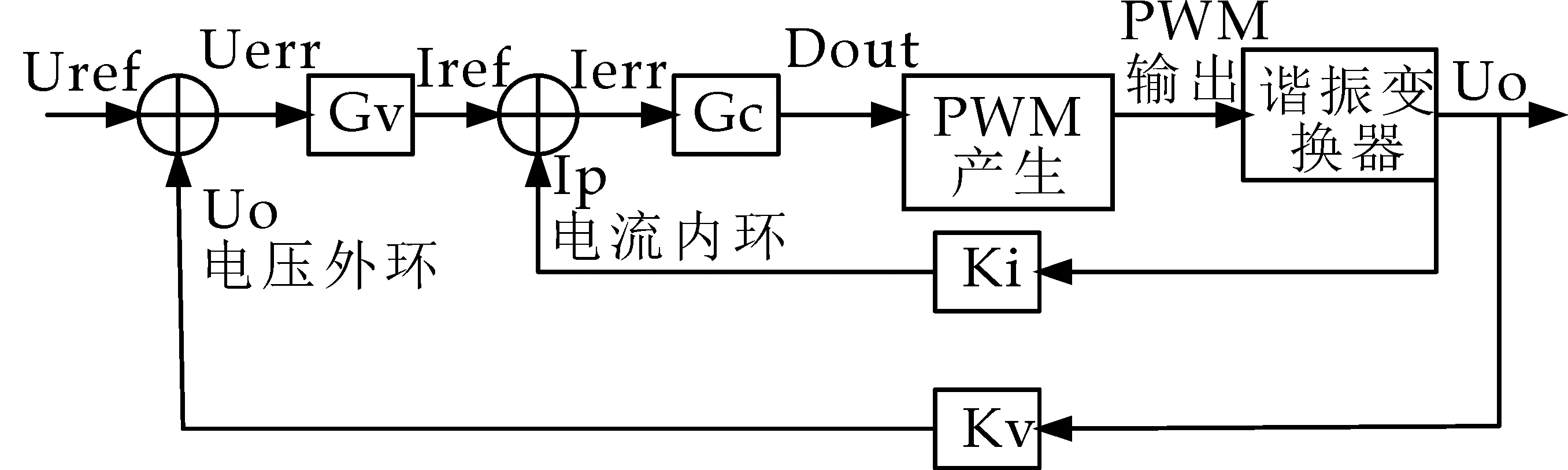

3.2 双闭环控制设计

3.3 软件设计