基于C8051F500的SPI接口研究

2014-08-07郑大勇

夏 琳,郑大勇

(1.中国电子科技集团公司第四十七研究所,沈阳110032;2.工业和信息化部电子第五研究所,广州510610)

基于C8051F500的SPI接口研究

夏 琳1,郑大勇2

(1.中国电子科技集团公司第四十七研究所,沈阳110032;2.工业和信息化部电子第五研究所,广州510610)

主要介绍了C8051F500中的SPI(Serial Perripheral Interface)接口,尤其是对SPI0CKR时钟速率控制寄存器、SPI0CFG配置寄存器、SPI0CN控制寄存器、SPI0DAT数据寄存器、Shift Register移位寄存器的结构和功能进行了详细介绍,并深入研究了SPI接口的通信过程。通过仿真,验证了主机与从机之间的数据传输以及各个寄存器的功能。

SPI接口;配置寄存器;控制寄存器;数据寄存器;移位寄存器

1 引 言

SPI(Serial Perripheral Interface)串行外围设备接口,是Motorola公司推出的同步串行接口技术,是一种灵活的、全双工,同步的串行通信总线。SPI可以作为主机和从机方式工作,具有三线和四线工作模式,在同一SPI总线上可支持多个主机和从机间的通信。从机选择信号NSS可被设置为输入以选择工作在从机方式的SPI,以避免两个以上主机同时进行数据传输时发生 SPI冲突。SPI在C8051F500芯片上只占用了四个引脚实现数据传输,节约了芯片的引脚数目,节省了布局空间,简单易用。

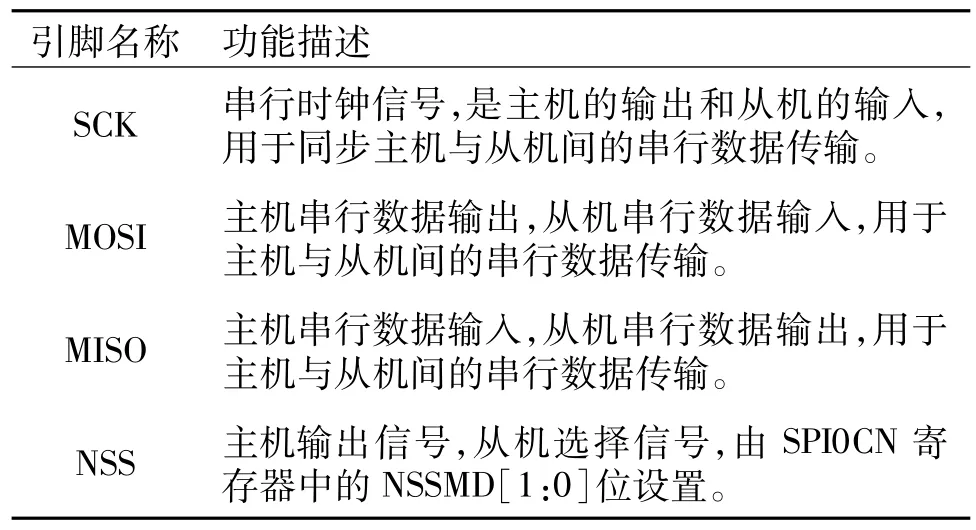

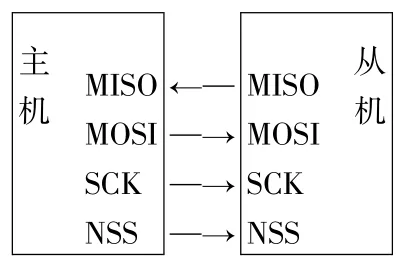

SPI通信结构是一个环形总线结构,由串行时钟信号SCK、串行数据MOSI和串行数据MISO、从机选择信号NSS构成,其时序简单,主要是在串行时钟信号SCK的控制下,两个双向移位寄存器进行数据交换。其引脚功能描述见表1。

2 SPI接口结构

C8051F500中的增强型SPI结构如图1所示,主要由SPI0CKR时钟速率控制寄存器、SPI0CFG配置寄存器、SPI0CN控制寄存器、SPI0DAT数据寄存器、Shift Register移位寄存器和相关控制电路组成。

表1 引脚功能描述

2.1 SPI0CKR时钟速率控制寄存器

SPI0CKR是一个8位的时钟速率控制寄存器,当SPI被配置成主机工作方式时,由该寄存器控制输出的串行时钟SCK频率。串行时钟SCK频率是从系统时钟(SYSCLK)分频得到的,由以下公式进行计算可得出,其中SYSCLK是系统时钟,SPI0CKR[7:0]是SPI0CKR寄存器中的8位数值。

图1 SPI接口结构图

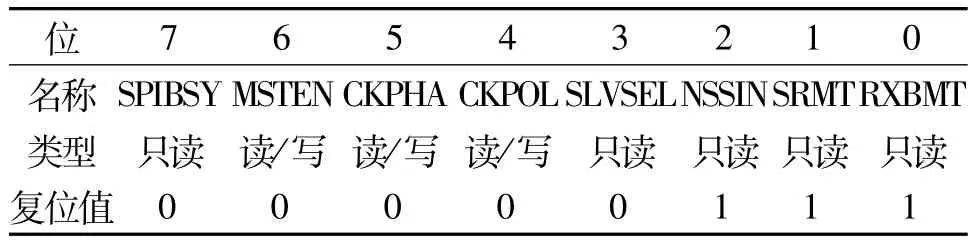

2.2 SPI0CFG配置寄存器

可以通过SPI0CFG配置寄存器对SPI串行时钟的极性和相位以及主从工作方式进行设置,其组成如表2所示。

表2 SPI0CFG配置寄存器

每一位的功能如下:

·Bit7-SPIBSY:SPI工作繁忙标志,当SPI传输正在进行时(主/从机),该位被置1;

·Bit6-MSTEN:主机工作方式允许位,0表示禁止主机工作方式,1表示允许主机工作方式;

·Bit5-CKPHA:SPI时钟相位配置,0表示在时钟SCK周期的第一个边沿进行数据采样,1表示在时钟SCK周期的第二个边沿进行数据采样;

·Bit4-CKPOL:SPI时钟极性配置,0表示在空闲时时钟SCK为低电平,1表示在空闲时时钟SCK为高电平;

Bit3-SLVSEL:从机选择标志位,当NSS引脚为低电平时,该位被置1,表示SPI是被选中的从器件;当NSS引脚为高电平时,该位被清0,表示SPI是未被选中的从器件;

·Bit2-NSSIN:NSS引脚输入的瞬间值;

·Bit1-SRMT:移位寄存器空标志位(从机模式有效),当所有数据都被移入/移出移位寄存器,并没有新数据从缓冲器读出/写入时,该位被置1;当数据从发送缓冲器传送到移位寄存器或时钟SCK发生变化时,该位被清0;主机工作方式时,该位为1;

·Bit0-RXBMT:接收缓冲器空标志位,当接收缓冲器中的数据被读出且没有新的数据时,该位被置1;如果接收缓冲器中有新数据未被读出,则该位被清0;主机工作方式时,该位为1;

通过上述的功能简介可以看出,SPI数据传输模式被设置成CPOL=1和CPHA=1时,在一个SCK时钟周期内,每个单独的SPI都能以全双工方式,同时发送和接收一位数据。因此,SPI总线的频率越快,时钟周期越短,则SPI间数据交换的速率就越快。

2.3 SPI0CN控制寄存器

通过SPI0CN控制寄存器可以查看一些标志和设置SPI三/四线通信模式,主要是用到SPIF这个标志位,接收完成和发送完成都会置位这个标志,进入中断服务程序。其组成如表3所示。

表3 SPI0CN控制寄存器

每一位的功能如下:

·Bit7-SPIF:SPI中断标志位,在数据传输结束后,该位由硬件置1;如果中断允许,该位置1将会使CPU转到SPI中断服务程序。该位不能被硬件自动清0,必须用软件清0。

·Bit6-WCOL:写冲突标志位,该位由硬件置1,并产生一个SPI中断,表示在数据传送期间对SPI数据寄存器进行了写操作。该位不能被硬件自动清0,必须用软件清0。

·Bit5-MODF:方式错误标志位,当检测到主机工作方式冲突时,该位由硬件置1;该位不能被硬件自动清0,必须用软件清0。

·Bit4-RXOVRN:接收溢出标志位,当前传输的最后一位已移入SPI移位寄存器,而接收缓冲器中仍保存着前一次传输未被读取的数据时,该位由硬件置1,并产生一个中断。该位不能被硬件自动清0,必须用软件清0。

·Bit3/2-NSSMD[1:0]:选择模式位,通过该两位选择NSS工作方式:00表示三线主/从机工作方式,NSS信号不连接到端口引脚;01表示四线从机或多主机工作方式,NSS是输入引脚;1X表示四线单主机工作方式,NSS是一个输出引脚。

·Bit1-TXBMT:发送缓冲器空标志位,当新数据被写入发送缓冲器时,该位被清0;当发送缓冲器中的数据被传送到移位寄存器时,该位被置1,表示可以向发送缓冲器写入新的数据。

·Bit0-SPIEN:SPI使能位,1表示SPI允许,0表示SPI禁止;

2.4 SPI0DAT数据寄存器

SPI0DAT是一个8位的可读写数据寄存器,用于发送和接收SPI数据。在主机工作方式下,向SPI0DAT写入数据时,数据被放到发送缓冲器中并启动发送,读SPI0DAT返回接收缓冲器的数据。

写数据是将数据传输到发送缓冲器中,通过移位寄存器将发送缓冲器中的数据串行发送出去;读数据是将移位寄存器接收到的串行数据传输到接收缓冲器中。

2.5 ShiftRegister移位寄存器

Shift Register是SPI内部的8位移位寄存器,它的主要作用是根据SPI时钟信号状态,往接收/发送缓冲器里移入/移出数据。

3 SPI功能验证

结合仿真,对主、从机之间的数据传输进行验证,深入了解SPI的通信方式。

3.1 SPI仿真验证

利用仿真软件,以四线主/从机工作方式为例,SPI主从机数据传输仿真验证环境如图2所示。

图2 仿真验证图

基于C8051F500的SPI主机初始化程序:

MOV A7,#0FH;//SFRPAGE=0F页;

MOV A4,#0DH;//将端口设置为输出推挽方式;

MOV E1,#04H;//交叉开关中允许SPI;

MOV C7,#40H;//交叉开关允许、I/O端口弱上拉;

MOV A7,#00H;//SFRPAGE=00页;

MOV A1,#40H;//SPI主机模式;

CKPHA=0;

CKPOL=0;

MOV F8,#0DH;//SPI四线主机模式;SPI允许;

MOV A2,#17H;//SYSCLK=24MHz,fSCK=500KHz;

MOV A3,#AAH;//向主机SPI0DAT写入数据AAH;

基于C8051F500的SPI从机初始化程序:

MOV A7,#0FH;//SFRPAGE=0F页;

MOV A4,#0DH;//将端口设置为输出推挽方式;

MOV E1,#04H;//交叉开关中允许SPI;

MOV C7,#40H;//交叉开关允许、I/O端口弱上拉;

MOV A7,#00H;//SFRPAGE=00页;

MOV A1,#00H;//SPI从机模式;

CKPHA=0;

CKPOL=0;

MOV F8,#05H;//SPI四线从机模式;SPI允许;

3.2 SPI主机工作方式

SPI总线上的所有数据传输都由SPI主机启动。通过将主机允许标志位MSTEN(SPI0CN.6)置1,将SPI置于主机工作方式。当处于主机工作方式时,向SPI数据寄存器(SPI0DAT)写入一个数据字节时是写发送缓冲器。如果SPI移位寄存器为空,发送缓冲器中的数据字节被传送到移位寄存器,数据传输开始。SPI主机立即在MOSI线上串行移出数据,同时在SCK上提供串行时钟。在传输结束后SPIF(SPIOCN.7)标志位被置为逻辑1。如果中断被允许,在SPIF标志置位时将产生一个中断请求。在全双工操作中,当SPI主机在MOSI线向从器件发送数据时,被寻址的SPI从机可以同时在MISO线上向主机发送其移位寄存器中的内容。因此,SPIF标志既作为发送完成标志又作为接收数据准备好标志。从从机接收的数据字节以MSB在先的形式传送到主器件的移位寄存器。当一个数据字节被完全移入移位寄存器时,便被传送到接收缓冲器,处理器通过读SPIODAT来读该缓冲器。

3.3 SPI从机工作方式

当SPI被使能而未被配置为主机时,它将作为SPI从机工作。作为从机,由主机控制串行时钟SCK,从MOSI移入数据,从MISO引脚移出数据。SPI逻辑中的位计数器对SCK边沿计数。

当8位数据经过移位寄存器后,SPIF标志位被置为逻辑1,接收到的字节传送到接收缓冲器中。通过读数据寄存器SPI0DAT来读取接收缓冲器中的数据。从机不能启动数据传送,通过写数据寄存器SPI0DAT来预装要发送给主机的数据到移位寄存器。写往SPI0DAT的数据是双缓冲的,首先被放在发送缓冲器,如果移位寄存器为空,发送缓冲器中的数据会立即被传送到移位寄存器。当移位寄存器中己经有数据时,SPI将在下一次(或当前)SPI传输的最后一个SCK边沿过去后再将发送缓冲器内的数据装入移位寄存器。

在从机检测到第一个SCK边沿后,移位寄存器中的数据被锁定。在第一个SCK边沿之后写入SPI0DAT的数据被保持在发送锁存器中,直到当前传输结束。

4 结束语

结合仿真验证对C8051F500中的SPI接口进行了深入研究,详细了解了主机与从机之间的数据传输过程。如今,SPI串行接口主要应用在EEPROM、Flash、实时时钟(RTC)、数模转换器(ADC)、数字信号处理器(DSP)以及数字信号解码器等器件中。它在芯片中只占四个引脚,用来完成控制以及数据传输,具有简单易用的特性,现在越来越多的芯片上都集成了SPI技术。

[1]李刚,林凌.与8051兼容的共性能、高速单片机-C8051FXXX[M].北京:北京航空航天大学出版社,2002.

[2]潘琢金,施国君.C8051FXXX高速SOC单片机原理及应用[M].北京:北京航空航天大学出版社,2002.

[3]张毅刚,彭喜源.MCS-51单片机应用设计[M].哈尔滨:哈尔滨工业大学出版社,2003.

Study of SPIBased on C8051F500

XIA Lin1,ZHENG Da-yong2

(1.The47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China;2.CEPREI,Guangzhou 510610,China)

This paper mainly describes the Serial Perripheral Interface(SPI)in C8051F500,especially introduces the structure and the functions of SPI0CKR,SPI0CFG,SPI0CN,SPI0DAT and Shift Register,and studies the communication process of Serial Perripheral Interface(SPI)between master and slave device by simulation.

SPI;SPI0CFG;SPI0CN;SPI0DAT;Shift Register

10.3969/j.issn.1002-2279.2014.03.004

TN4

:A

:1002-2279(2014)03-0011-03

夏琳(1981-),女,沈阳市人,工程师,主研方向:集成电路设计。

2013-12-26