一种新型双通道MOS开关栅压自举电路

2014-07-31庄奕琪汤华莲杜永乾

景 鑫,庄奕琪,汤华莲,张 丽,杜永乾

(西安电子科技大学宽禁带半导体材料与器件教育部重点实验室,陕西西安 710071)

一种新型双通道MOS开关栅压自举电路

景 鑫,庄奕琪,汤华莲,张 丽,杜永乾

(西安电子科技大学宽禁带半导体材料与器件教育部重点实验室,陕西西安 710071)

设计了一种新的低压、高速、高线性度的双通道MOS开关栅压自举电路,该电路采用同时自举NMOS和PMOS的并行结构,不但降低了MOS开关的导通电阻值,同时在输入信号的全摆幅范围内实现了常数的导通电阻;考虑了器件可靠性要求且与标准的CMOS工艺技术兼容.采用0.13μm CMOS工艺和1.2 V工作电压的仿真实验表明,提出开关的导通电阻在全摆幅输入信号范围内的变化量小于4.3%;在采样频率为100 MHz,输入峰峰值为1 V,输入频率为100 MHz时,提出开关的总谐波失真达到-88.33dB,较之传统的NMOS自举开关以及标准的CMOS传输门开关,分别提高了约-14.8dB和-29dB.设计的开关可应用于低压、高速高精度的开关电容电路中.

自举电路;线性CMOS开关;常数导通电阻;电荷泵;开关电容电路;低电压

高性能的采样/保持电路是许多集成电路应用中的关键模块之一.采样开关作为采样/保持电路中至关重要的单元,其性能的优劣决定了整个采样/保持的精度和线性度[1-2].然而,随着采样时钟频率的提高和电源电压的降低,传统MOS开关的线性度不断降低,限制了采样/保持电路的动态范围和采样精度,已无法满足高速、高精度采样/保持电路的设计要求.

采样开关的非线性主要源于开关导通电阻的非线性,一种减小开关导通电阻非线性的常用方法[3]是使用大尺寸的CMOS传输门(CMOS-TG)开关.然而,CMOS-TG的电导率是与输入信号紧密相关的,随输入信号的摆幅而变化,这将在输出信号中引入谐波,增加了信号的非线性失真.而且大尺寸的CMOS-TG也会增加信号通路的寄生效应,使得电路的频宽降低,不利于高速应用;另一种减小开关导通电阻非线性的方法是采用NMOS自举开关技术[1-6],即通过固定器件的栅源电压来达到减小开关导通电阻非线性的目的.这种技术虽然消除了因过驱动电压随输入信号变化所产生的非线性,但是器件阈值电压随输入信号变化所产生的非线性依然存在,而且限制了开关动态性能的进一步提高.如果采用大的开关尺寸,虽然能够缓解体效应的影响,但同时引入了大的寄生电容,不仅需要更大的自举电容来消除信号路径上寄生电容带来的电荷分享效应[1],而且也增加了开关导通电阻与输入信号的相关性.另外,由于自举开关技术自身的特性,也会带来器件的可靠性问题以及是否适合轨到轨应用的问题[5-8].针对上述问题,笔者提出了一种新的双通道MOS自举开关电路,该电路充分考虑了器件可靠性与轨到轨的应用要求,采用同时自举NMOS和PMOS的并行结构,在降低MOS开关导通电阻的同时,在输入信号的全摆幅范围内实现了接近常数的导通电阻值.提出的自举电路可由标准的N-WELL CMOS工艺实现,具有高线性度、高速度、低功耗和易实现的特性,适于高速高精度的开关电容电路的应用.

1 MOS开关分析

MOS器件用作开关有着优良的电特性,在混合信号电路中被大量使用,如开关电容电路、模数转换电路等[1-6].然而,MOS器件本身并不是一个理想的开关,在导通时存在导通电阻,其阻值与开关器件的几何尺寸、栅源电压及阈值电压等有关.同时,MOS晶体管的金属氧化层、栅源和栅漏等存在寄生电容,实际的MOS开关在导通时可等效为一个由寄生电容和电阻组成的RC网络.

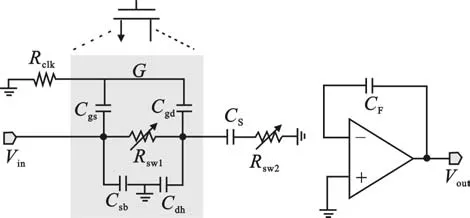

图1 典型的MOS开关采样电路

考虑图1所示的电路,其中rsw1和rsw2分别表示底板采样开关s1和顶板共模开关的导通电阻;rclk是时钟驱动器的输出阻抗;Cgs和Cgd是s1栅极对源和漏的交叠电容;Csb和Cdb是源和漏对衬底的电容.当激励信号vin(t)=A sin(ωt)时,计算采样电容CS底板上的电压值,其中,A表示激励信号的幅度,ω是激励信号的角频率.为了简化计算,忽略电阻和的影响,图1所示的采样电路简化为1个一阶RC低通滤波电路,使得电路对高频信号有抑制作用,由Kirchhoff电压定律可得

其中,I(t)表示流过采样电路的周期性信号电流.由式(1)可解得采样电容CS底板上的瞬态电压为

对于短沟道器件,导通电阻rsw1与器件各端子电压及器件尺寸之间的关系可表示为[9]

如果针对一个具体的输入信号频率fin,-3dB频率和输入信号之间的关系可表示为

其中,N表示对经过开关之后输出信号精度的要求.从式(2)~(5)中可以知道,MOS开关器件为了能应用于高速高精度的开关电容电路,不仅需要降低开关的导通电阻值,同时需要降低导通电阻的信号相关性,从而提高采样过程的速度和精度.

2 传统的NMOS栅压自举开关

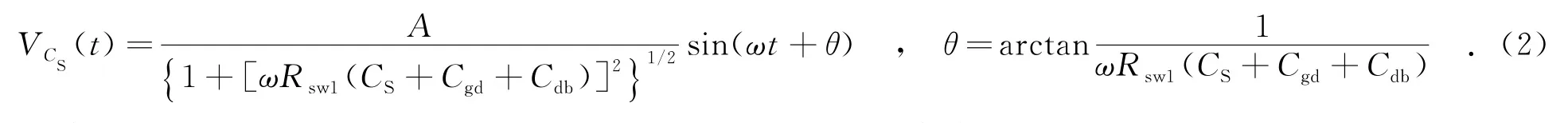

图2 传统的NMOS自举开关

为了降低MOS开关的导通电阻值及其信号相关性,文献[9]提出了NMOS自举开关技术.图2是传统的NMOS自举开关电路原理图.单相时钟clk控制主开关管m12的导通和截止,当clk为高电平时,主开关m12导通,节点n1的电压跟随输入信号vin变化,使得在开关导通期间m12的栅源电压vGS始终等于vDD.实际中,由于信号通路上寄生电容引入的电荷分享效应,在开关导通时,m12的栅源电压vboost要明显小于电源电压vDD,而且vboost因为寄生电容的影响而变得与输入相关.参考图2所示,vboost可近似表示为

其中,Ct是连接至Cboost上极板的寄生电容;Cg是m12栅极的寄生电容;Cgs和Cgd分别是m12栅源、栅漏的交叠电容;t0表示开关关断时的瞬间.式(6)表明,由于大的寄生电容Cg和Ct的存在,使vboost与vin的相关性变得明显,从而导致开关的线性度降低,而且信号相关的电荷注入也会增加.

与单一的MOS开关相比,传统的NMOS自举采样开关通过固定器件的栅源电压vgs来减小开关的导通电阻,同时降低开关导通电阻的信号相关性,这样虽然消除了因过驱动电压随输入信号变化所产生的非线性,但是器件阈值电压随输入信号变化所产生的非线性依然存在.因此在文献[8,10-12]中已提出了一些方法来补偿这一问题.其中,按电路结构的不同可分为:在采样开关导通时,将开关的源极与衬底端直接连接以消除背栅效应的影响[10].这是一种直接的方法,但是在标准的N-WELL CMOS工艺中由于NMOS管直接制作在衬底上,因此这一方法只能用于PMOS器件;采用CMOS自举开关技术,即同时自举NMOS和 PMOS开关[8,11-12]的方法.然而在文献[11]设计的CMOS自举开关中存在可靠性的问题,而且不适于轨到轨的应用.在文献[11]的图2中,m9和m17管的栅源电压分别在采样相和保持相时超过了电源电压值vDD,影响了电路的工作寿命,而且m17的栅极电压并不跟随源端电压变化.因此,m17的导通受限于vin>不能在全摆幅信号范围内可靠实现轨到轨的信号传输;在文献[12]的图4中,在采样相时,m2栅极的负电压会使SG管的源/漏结二极管发生正偏,因而文献[12]提出的电路必须限制输入电压的峰值;在文献[8]提出的开关电路中,当输入信号幅度较小时,由于过驱动电压的设计值(忽略由信号路径上寄生电容所引入的电荷分享效应)小于电源电压vDD,因而获得的开关的导通电阻要略大于传统的自举开关,而且文献[8]的图2所设计的电路,在采样相时,m2n和m7n以及m2p和m7p的栅源、栅漏电压会超过电源电压vDD,从而降低了器件的可靠性和寿命.

3 新的双通道MOS开关栅压自举电路

3.1 标准的CMOS开关

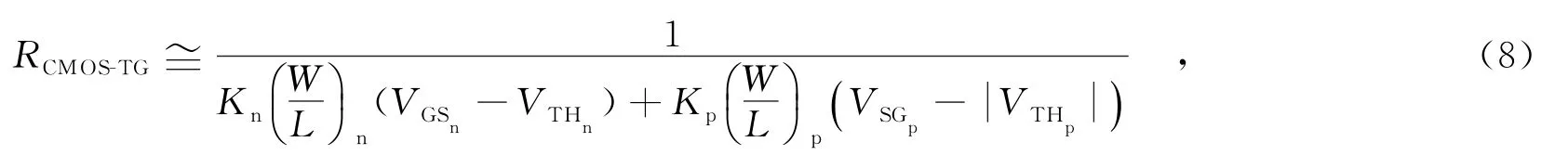

当器件工作在深线性区时,标准CMOS-TG的导通电阻可近似表示为

采用统计学软件SPSS15.0进行数据分析处理,其中,计数资料采用X2检验,以百分比表示,计量资料采用t检验,以均数±标准差表示,P<0.05表示差异突出,具有统计学意义。

其中,vGSn表示NMOS栅源电压;vSGp表示PMOS源栅电压;vT表示阈值电压;K=μCox,表示工艺跨导参数;下标n和p分别表示NMOS和PMOS器件.然而,即使在一阶近似的情况下,CMOS-TG的导通电阻相对于输入仍然是非线性的.考虑图1所示的电路,忽略寄生电容的影响,从输入至采样电容CS的传输函数可表示为

其中,vCS表示采样电容CS底板的对地电压.忽略共模开关rsw2的影响,将式(8)代入式(9),可得

式(10)表明,由于CMOS-TG导通电阻的信号相关性,vCS与vin呈现二次关系,引入了明显的谐波失真.

3.2 文中提出的双通道MOS自举开关

由上述分析可得,传统的CMOS-TG并不适合高速高精度的采样应用.文中参考了已有相关文献的设计,将传统的NMOS栅压自举技术拓展至CMOS-TG,提出了一种新的易实现的CMOS栅压自举电路.

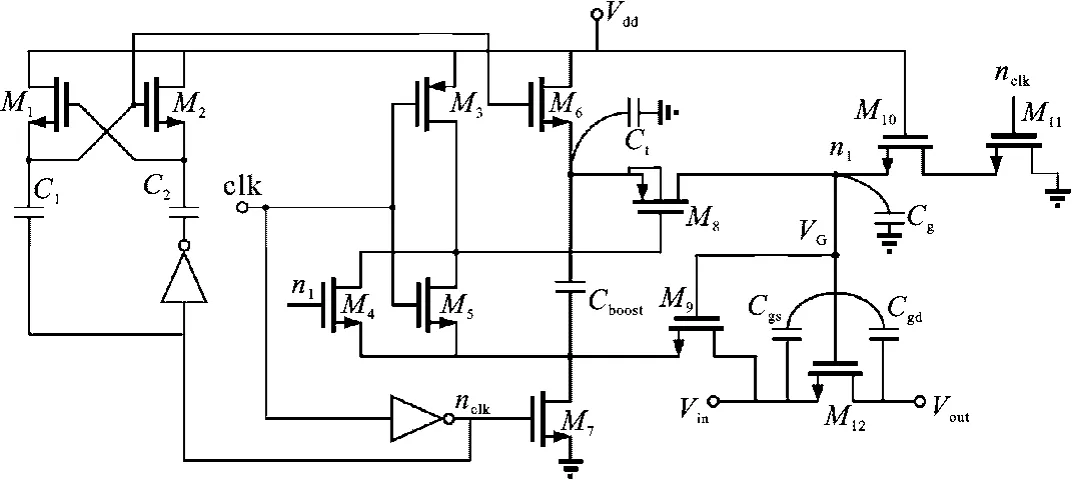

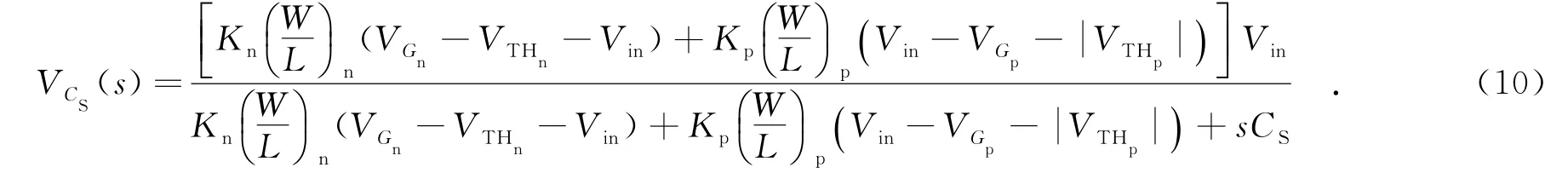

图3 文中提出电路的基本原理图

图4 文中提出CMOS自举开关的电路实现图

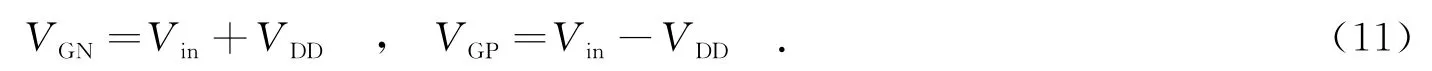

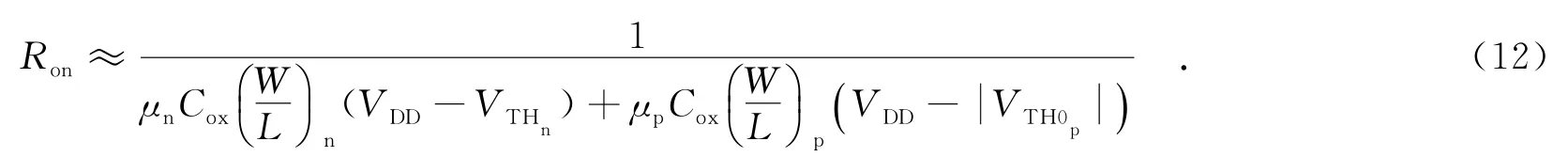

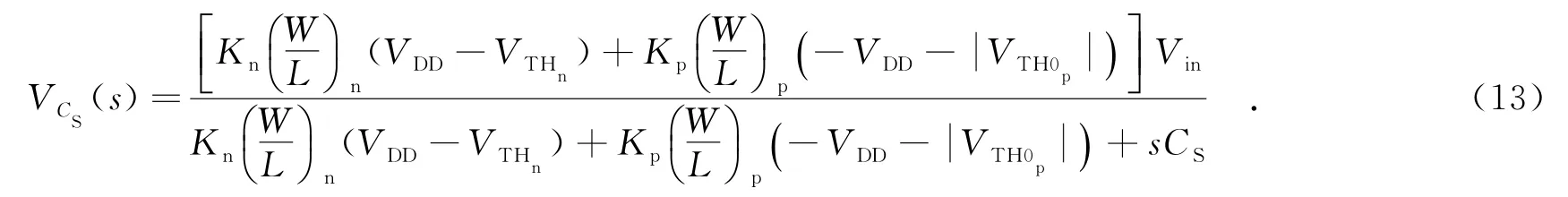

文中提出的CMOS自举电路由单相时钟控制,其设计原理如图3所示,电路实现在图4中给出.图中的晶体管MNS和MPS是主采样开关,导通时,开关MPS的体端子通过m17(sw6)连接至MPS的源端,以消除MPS的背栅效应.开关MNS和MPS的栅极电压可分别表示为

从而,开关的导通电阻由式(8)改进为

式(12)表明,设计的CMOS自举开关呈现常数的导通电阻,与输入信号vin无关.将式(12)代入式(9),可得

对比式(10)可以看出,vCS与vin呈现线性关系,显著降低了谐波失真.

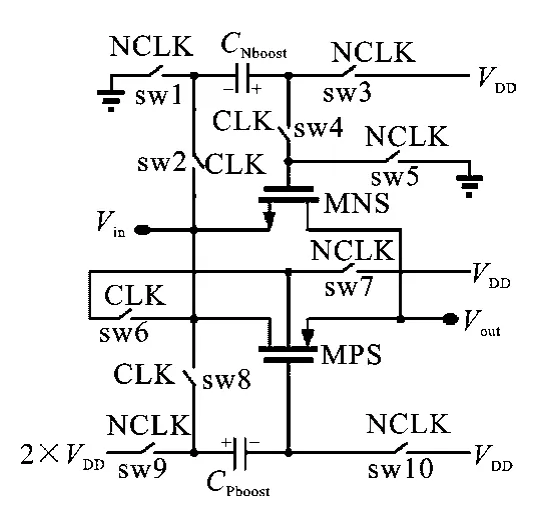

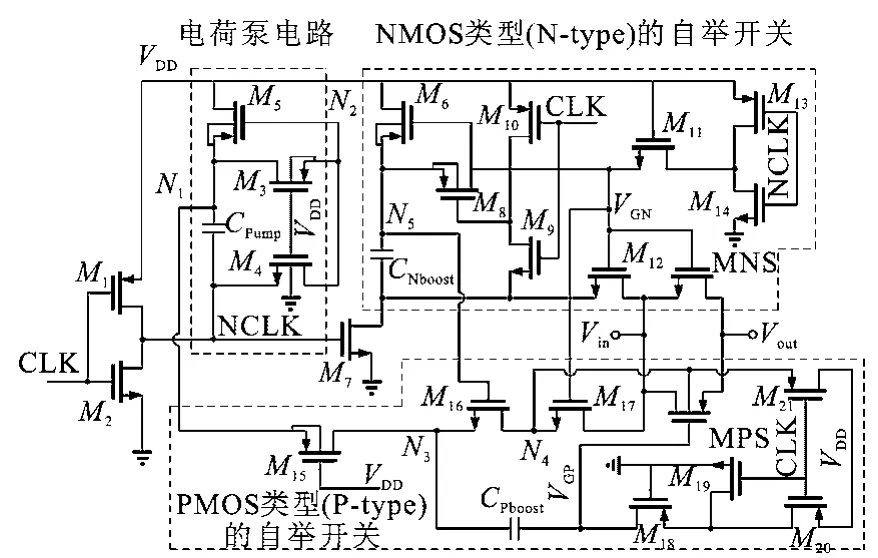

如图4所示,设计的CMOS自举电路由3部分组成:1个新的时钟电荷泵电路、1个PMOS类型(P-type)的自举开关和1个NMOS类型(N-type)的自举开关.其中,N-type部分与文献[4]中使用的自举开关类似,增加m13是为了降低m14漏端节点的非线性和寄生电容[1].考虑到器件的可靠性要求[5-8],在P-type部分利用了N-type中的n5和vGN节点以可靠偏置P-type中m16和m17.图4中,由晶体管m1、m2、m3、m4、m5构成的时钟自举电路实际上是一个新颖的电荷泵电路,其工作过程如下:当CLK为高电平时,电容CPump的下极板被拉至电源地,使得常开的m4导通,节点n2变为低电平,从而使m5导通,并将电容CPump的上极板充电至电源电压vDD,节点n1变为高电平,此时m3和m15处于截止状态;当CLK变成低电平时,m4截止,节点n1变为2VDD,使得m3导通,节点n2跃变为2VDD,将m5关断,同时m15导通,CPump通过m15对电容CPboost充电至vDD,在CMOS自举开关导通时用作浮动电池.

电路的工作原理如下:当时钟CLK为低电平时,两个并联的主开关MNS和MPS截止,m20将主开关MPS的栅极连接至电源vDD,同时电容CNboost和电容CPboost都被充电至vDD.为了将电容CPboost充电至vDD,电荷泵电路通过m15将节点n3倒拉至2VDD.电容CNboost通过m6和m7充电至vDD,m8和m12用于隔离自举电容CNboost和主开关MNS.当时钟CLK为高电平时,m7截止,m9将m8的栅极连接至浮动电池CNboost,此时m12导通,使得电容CNboost跨接在主开关MNS的栅极和源极,MNS导通;m16和m17也同时导通,使得电容CPboost跨接在主开关MPS的源极和栅极,MPS导通.这样,浮动电池CNboost和CPboost在开关导通期间,使得MNS和MPS的栅源及源栅电压被固定为电源电压vDD,而与输入信号vin无关,既保证了开关的导通电阻很小,又保证了阻值的恒定.在P-type的自举电路中,增加m16管是出于器件可靠性的考虑,使m17的漏源电压在一个完整的时钟周期内不会超过电源电压vDD,同时也简化了主开关MPS背栅效应的补偿电路,可以将MPS的衬底端直接连接至n4节点.这样,当开关导通时,MPS的衬底通过m17连接至输入信号vin,即MPS的源端;当开关截止时,MPS的衬底通过m21连接至vDD,确保MPS可靠关断.m11和m18的作用相同,分别是为了增加m14和m20的可靠性而引入的.m8和m15的衬底端与源极短接,以避免闩锁效应[3].由以上分析图4所实现的电路中,在导通状态时,信号通路上的所有晶体管m16、m17(sw6、sw8)以及m8、m12(sw2、sw4)在输入信号的全摆幅范围内都能可靠地传输信号,因而满足轨到轨的应用需求[8],而且所有晶体管的栅源、栅漏以及漏源电压都不超过电源电压vDD,也同时满足了可靠性的要求[5-8].

4 电路仿真与性能对比

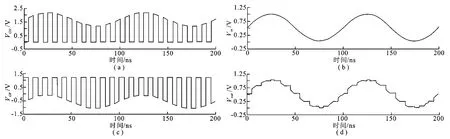

为了比较文中提出的CMOS自举开关的性能,分别对传统的NMOS自举开关、文中提出的CMOS自举开关以及传统的CMOS-TG在Cadence Spectre®环境下进行仿真测试.图5是文中提出的CMOS自举电路在输入峰峰值为1 V、频率为10 MHz的正弦信号.当采样频率为10 MHz时,从图5中各主要节点的瞬态模拟波形可以看到,主开关管MNS和MPS的栅极电压vGN和vGP良好地跟随了输入信号vin的变化.

图5 文中提出的CMOS自举开关的瞬态仿真波形

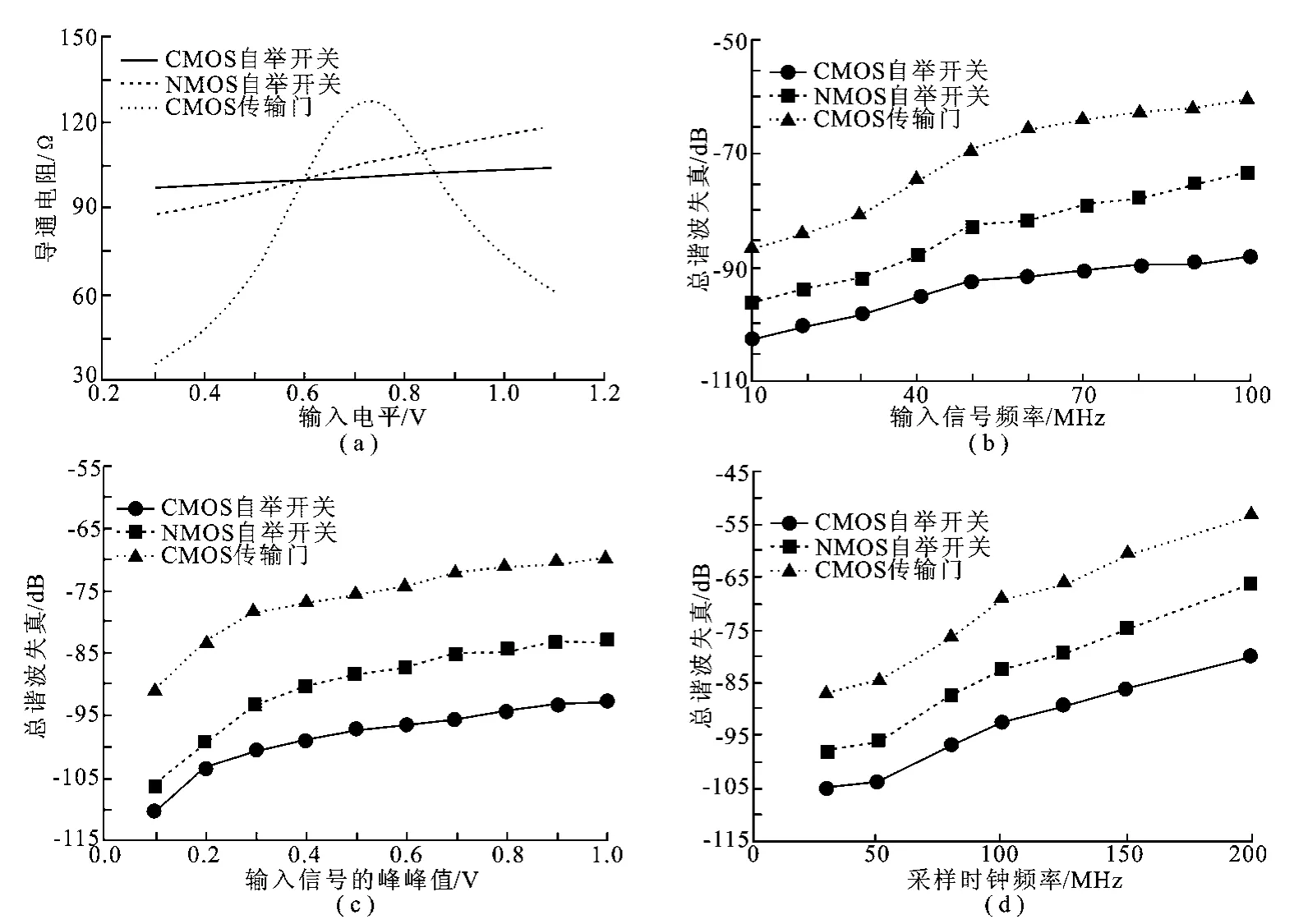

测试3种开关的静态特性.在仿真实验中,3种开关导通电阻的设计值约为100Ω,采用TSMC 130 nm CMOS工艺设计,工作电压为1.2 V.在文中提出的CMOS自举开关中,主采样开关MNS和MPS的尺寸分别为(W/L)n=3.88μm/0.13μm,(W/L)p=10.52μm/0.13μm,对应的传统NMOS自举开关中(W/L)n=5.7μm/0.13μm,CMOS-TG中(W/L)n=18μm/0.13μm,(W/L)p=41.4μm/0.13μm.图6 (a)是3种开关的导通电阻值ron与输入信号电平的关系图.可以看出,文中设计的CMOS自举电路,其导通电阻随输入信号电平的变化最小,最大变化量约为4.3%,因而其导通电阻ron在这3种开关中的信号相关性最小,也同时具有最好的线性度;而传统NMOS自举开关的导通电阻在输入信号的全摆幅范围内,最大变化量达到19.6%;CMOS-TG的导通电阻随输入信号电平的变化最为剧烈,在全摆幅的输入范围内,最大变化量超过65.4%.

图6 几种开关性能的模拟测试

测试3种开关的动态特性[12].在100 MHz采样频率时,输入信号峰峰值为1 V,信号频率从10 MHz增至100 MHz时,开关的总谐波失真(THD)与输入信号频率的关系如图6(b)所示.图6(c)是在100 MHz采样频率,约50 MHz输入信号频率条件下,开关的THD与输入信号峰峰值的关系图.实验结果表明,在100 MHz采样频率时,当输入信号峰峰值增加到1 V,输入信号频率增至100 MHz时,文中设计的CMOS自举开关的THD达到-88.33dB,相对于传统的NMOS自举开关约有-14.8dB的提高;当输入信号频率约取采样频率的一半.输入信号峰峰值为1 V时,开关的THD与不同采样频率的关系如图6(d)所示.在不同的采样频率下(30~200 MHz),文中所提出的自举开关的THD达到-80dB以下,而传统的NMOS自举开关在200 MHz采样频率时,THD增加到约-66dB.

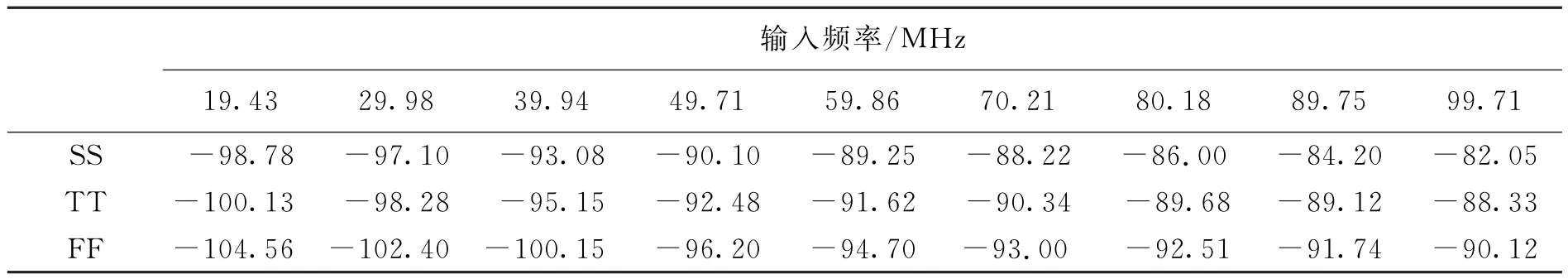

表1 不同工艺角下文中设计开关的总谐波失真THD____________dB

在不同工艺角下,文中设计开关的THD的模拟测试值在表1中给出.其中,输入信号峰峰值为1 V,信号频率约从20 MHz增至100 MHz,采样频率为100 MHz.可以看出,即使在最差的情况,文中设计的CMOS自举电路的THD仍然达到约-82dB.

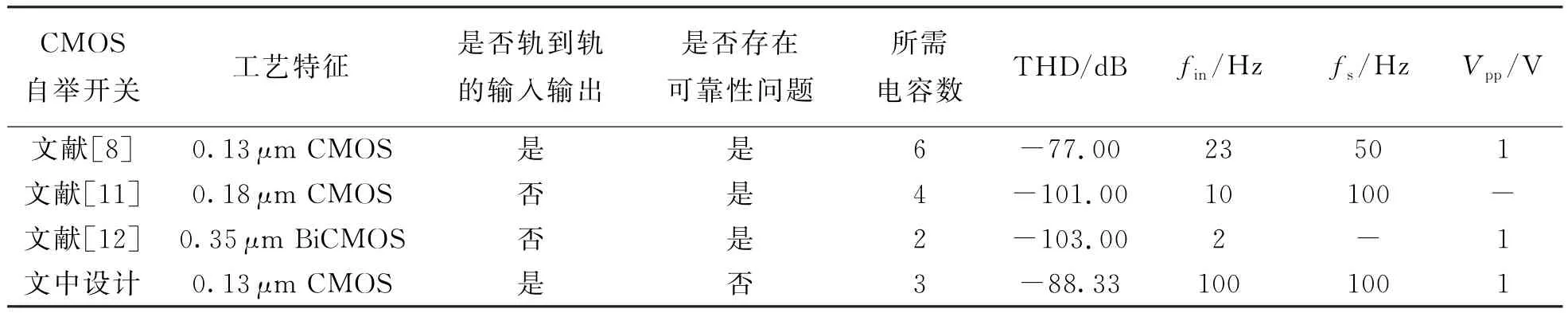

表2 文中设计开关与相关文献的CMOS自举开关的性能对比

最后,从线性度、所需电容数以及是否满足可靠性要求[5-8]等方面与已有的具有代表性的CMOS自举开关电路进行了对比,如表2所示.从表2可以看出,文中设计的CMOS自举开关相较于文献[8,10-12]中提出的双通道开关,不仅适于轨到轨的应用,而且具有更少的电容充电通路和更少的电容数目,因而具有更低的功耗和更小的芯片面积.而且在设计的自举电路中,所有MOS管的栅源、栅漏或是漏源电压都不会超过电源电压vDD,从而电路的可靠性和寿命也不会受到影响[5-8].

5 结束语

提出了一种新的低压模拟开关设计技术.设计的双通道MOS栅压自举电路与标准CMOS工艺兼容,当电路工作时所有器件的栅源、栅漏以及漏源电压都小于电源电压,而且信号通路上的所有元件都能轨到轨的传输信号,满足器件可靠性与轨到轨的应用要求.采用标准的TSMC 0.13μm CMOS工艺进行仿真测试,文中设计开关的导通电阻在输入信号全摆幅范围内的变化小于4.3%,有效提高了采样电路的精度和线性度.与已有的具有代表性的同类电路相比,提出的电路不但降低了设计复杂度,同时具有高线性度、高速度、低功耗和易实现的特性,已成功应用于一款高速高精度的流水线型模数转换器芯片中.

[1] Shu Guanghua,Guo Yao,Ren Junyan,et al.A Power-efficient 10-bit 40-MS/s Sub-sampling Pipelined CMOS Analogto-digital Converter[J].Analog Integrated Circuits Signal Processing,2011,67(1):95-102.

[2] Lee T S,Lu C C.A 250MHz 11bit 22m W CMOS Low-hold-pedestal Fully Differential Sample-and-hold Circuit[J]. Analog Integrated Circuits Signal Processing,2009,58(2):105-113.

[3] Sasidhar N,Kook Y,Takeuchi S,et al.A Low Power Pipelined ADC Using Capacitor and Opamp Sharing Technique with a Scheme to Cancel the Effect of Signal Dependent Kickback[J].IEEE Journal of Solid-State Circuits,2009,44(9): 2392-2401.

[4] Li Jian,Zeng Xiaoyang,Xie Lei,et al.A 1.8-V 22-m W 10-bit 30-MS/s Pipelined CMOS ADC for Low-Power Subsampling Applications[J].IEEE Journal of Solid-State Circuits,2008,43(2):321-329.

[5] Abo A M,Gray P R.A 1.5-V,10-bit,14.3-MS/s CMOS Pipeline Analog-to-Digital Converter[J].IEEE Journal of Solid-State Circuits,1999,34(5):599-606.

[6] Dessouky M,Kaiser A.Very Low-Voltage Digital-AudioΔ∑Modulator with 88-dB Dynamic Range Using Local Switch Bootstrapping[J].IEEE Journal of Solid-State Circuits,2001,36(3):349-355.

[7] Aksin D,AI-Shyoukh M,Maloberti F.Switch Bootstrapping for Precise Sampling Beyond Supply Voltage[J].IEEE Journal of Solid-State Circuits,2006,41(8):1938-1943.

[8] Galhardo A,Goes J,Paulino N.Design of Improved Rail-to-rail Low-distortion and Low-stress Switches in Advanced CMOS Technologies[J].Analog Integrated Circuits Signal Processing,2010,64(1):13-22.

[9] Waltari M.Circuit Techniques for Low Voltage and High Speed A/D Converters[D].Finland:Helsinki University of Technology,2002.

[10] Fayomi C J B,Roberts G W,Sawan M.Low-voltage CMOS Analog Bootstrapped Switch for Sample-and-hold Circuit: Design and Chip Characterization[C]//IEEE International Symposium on Circuits and Systems.Piscataway:IEEE, 2005:220-2203.

[11] Wang L,Yin W J,Xu J,et al.Dual-channel Bootstrapped Switch for High-speed High-resolution Sampling[J]. Electronics Letters,2006,42(22):1275-1276.

[12] Adeniran O A,Demosthenous A.Constant-Resistance CMOS Input Sampling Switch for GSM/WCDMA High Dynamic RangeΔ∑Modulators[J].IEEE Transactions on Circuits and Systems I:Regular Papers,2008,55(10):3234-3245.

(编辑:齐淑娟)

Novel dual-channel MOS bootstrapped switch circuit

JING Xin,ZHUANG Yiqi,TANG Hualian,ZHANG LI,DU Yongqian

(Ministry of Education Key Lab.of Wide Band-Gap Semiconductor Materials and Devices,Xidian Univ.,Xi’an 710071,China)

A novel low-voltage,high-speed and high-linear dual-channel MOS bootstrapped switch is proposed.This proposed switch utilizes the bootstrapping technique of both NMOS and PMOS simultaneously,thus resulting in small-variation low-value on-resistance over the entire input signal range. The switch considers reliability constrains and is suitable for standard CMOS technology.Based on the 0.13μm CMOS technology and 1.2 V power supply,simulation results show that the switch achieves an on-resistance variation less than 4.3%throughout the full range(vpp=1 V)of the input signal range.For a 100 MHz input with 1 V(vpp)amplitude,the switch has a total harmonic distortion(THD)up to -88.33dB at the 100 MHz sampling frequency,about-14.8dB and-29dB increase,compared with the conventional bootstrapped NMOS switch and the standard CMOS transmission gate,respectively.The circuit could be applied to the low-voltage and high speed-resolution switched-capacitor circuits.

bootstrap circuit;CMOS switch linearization;constant on-resistance;charge pump; switched-capacitor circuits;low voltage

TN432

A

1001-2400(2014)03-0138-07

10.3969/j.issn.1001-2400.2014.03.020

2013-08-15< class="emphasis_bold">网络出版时间:

时间:2013-11-22

国家重大科技专项资助项目(2012ZX03001018-001);中央高校基本科研业务费专项资金资助项目(K50511250006)

景 鑫(1977-),男,西安电子科技大学博士研究生,E-mail:jingxin_xd135@126.com.

http://www.cnki.net/kcms/detail/61.1076.TN.20131122.1628.201403.148_005.html