基于FPGA的高速串行AD转换器控制设计与实验研究

2014-03-26杨大伟杨秀芳李大伟韩俊锋陈剑虹

杨大伟,杨秀芳,李大伟,韩俊锋, 陈剑虹

(1.西安理工大学 机械与精密仪器工程学院,陕西 西安 710048;2.中国科学院 西安光学精密机械研究所,陕西 西安 710119)

随着工业技术的进步,现代数字控制系统对执行效率和集成化程度的要求越来越高[1]。特别是在靶场光电仪器平台多个伺服系统数据信号采集中,对多通道A/D转换的效率要求更高,此外,在外场便携式采集仪器与光电设备接口中,使用多通道高速A/D转换器还可以简化电路设计[2]。

许多文献对串行多通道A/D转换器AD7890的控制,基本上都是以单片机或者微处理器为控制核心。使用单片机作为处理器,虽然编程简单且容易控制,但是速度较慢,周期长,极大地限制了高速A/D的使用[3],而使用DSP作为处理器,需要专用SPI接口。采用FPGA作为控制核心,其时钟频率可高达100 MHz以上,与单片机或微处理器相比,更适合用于数字控制系统中直接对高速A/D器件进行有效控制[4-6]。

本设计以Xilinx公司高性能现场可编程门阵列Virtex-4系列FPGA芯片为核心器件,利用多通道串行A/D转换芯片AD7890实现快速、高精度的A/D转换。

1 FPGA控制AD7890原理框图

图1 FPGA控制AD7890设计原理图

2 A/D转换控制模块设计

依据AD7890工作原理,采用FPGA器件XC4VLX25芯片,在ISE 10.1软件环境下实现对A/D转换控制模块的程序设计及仿真。

2.1 AD7890的工作原理

AD7890是Analog Device公司推出的一款8通道12位高速串行A/D转换器。它的内部结构和引脚功能如图2、3所示,由8路模拟输入(信号调理)、多路选择器、跟踪/保持放大器、参考电源、输入控制寄存器和数据输出寄存器等部分组成[8]。

图2 AD7890内部结构功能图[8]

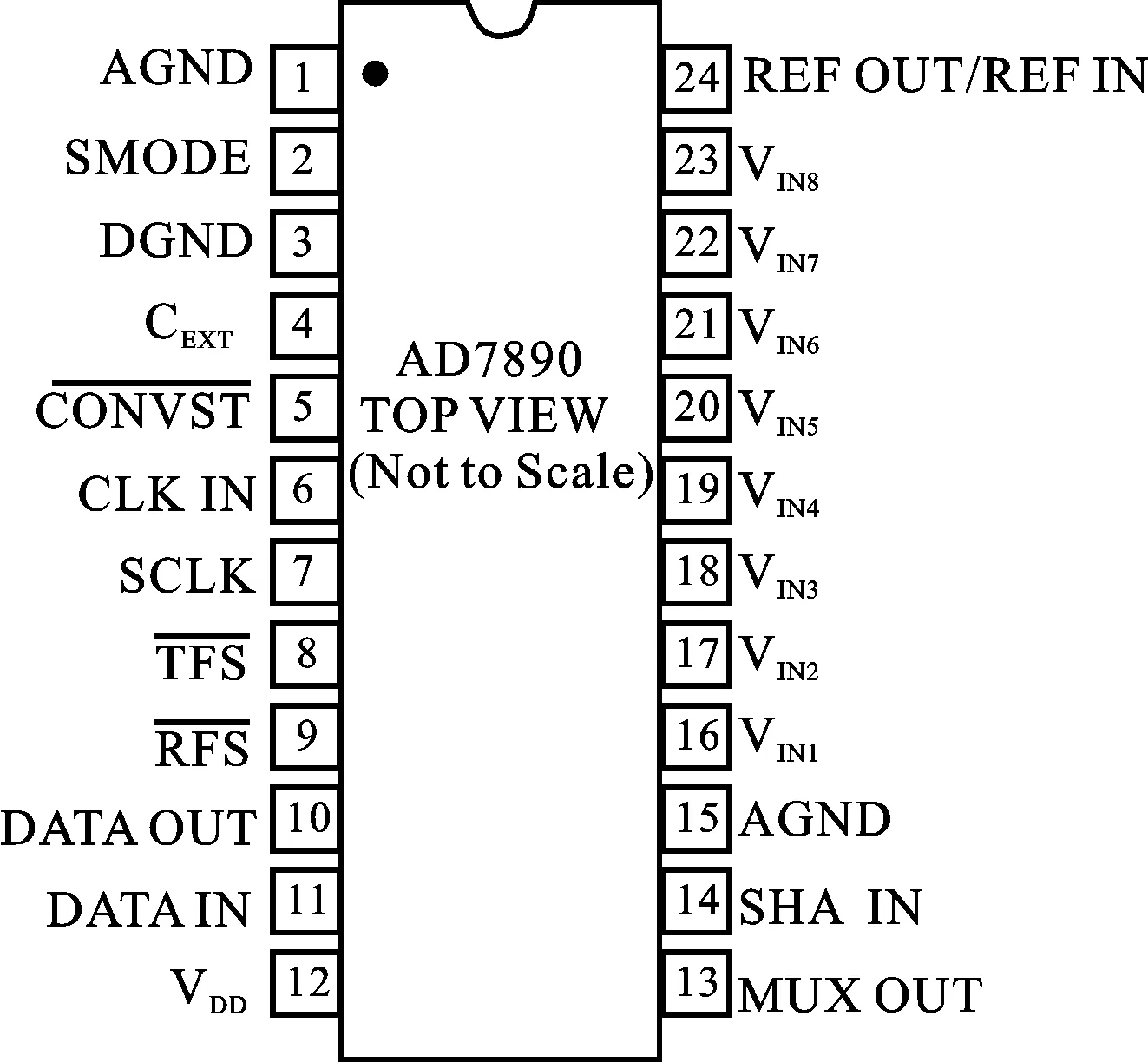

图3 AD7890引脚图[8]

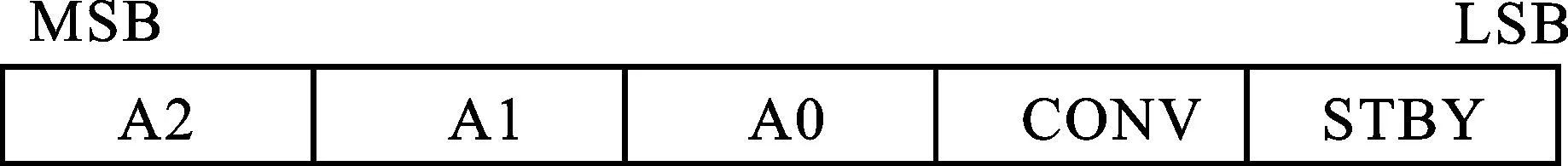

AD7890有两种工作模式(外部时钟和内部时钟)可选,由AD7890的SMODE引脚的高低置位决定,AD7890通过片内的高速双向串行数据接口接收输入控制字和输出串行数据,器件的8路模拟输入通道通过给定输入控制字选出。串行输入控制寄存器由5位组成:3位通道选择地址位A2、A1、A0,1位软件控制转换状态位CONV(低电平有效)、1位休眠状态位STBY,如图4所示。在指定芯片输入控制命令时,至少需要6个SCLK时钟脉冲信号才能完成对寄存器的写操作,超过6个写周期时钟的输入字无效,且5位控制位默认输入为0。被选通道按照公式(通道号=4×A2+2×A1+A0+1)计算。

图4 AD7890输入控制寄存器

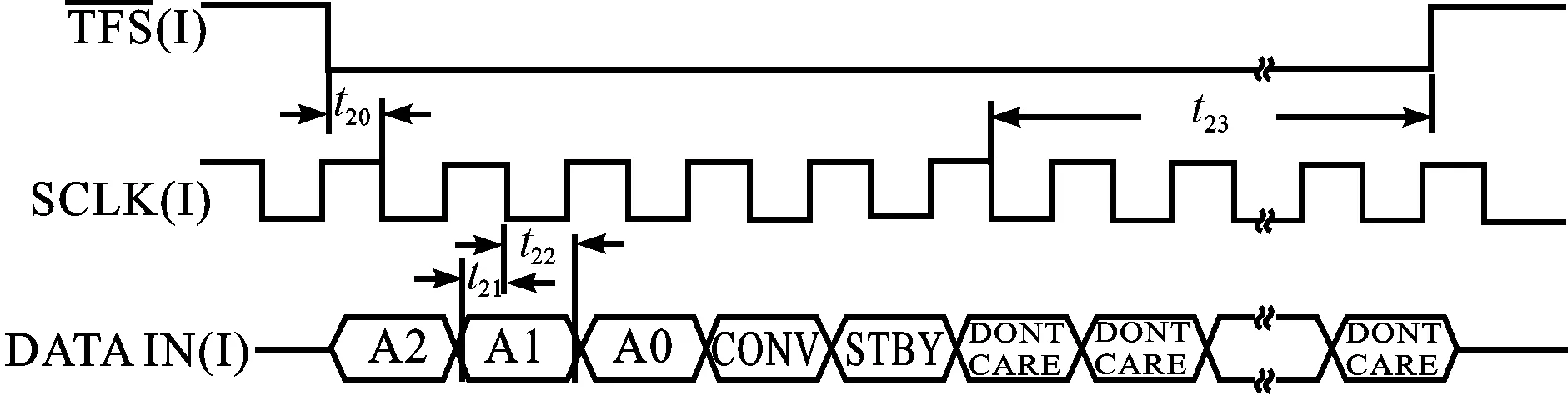

图5 外部时钟模式写操作时序[8]

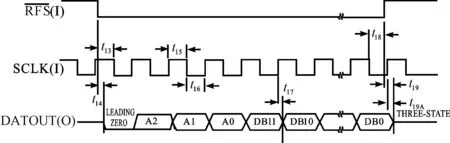

图6 外部时钟模式读操作时序[8]

2.2 ISE10.1软件环境下的控制程序设计及仿真

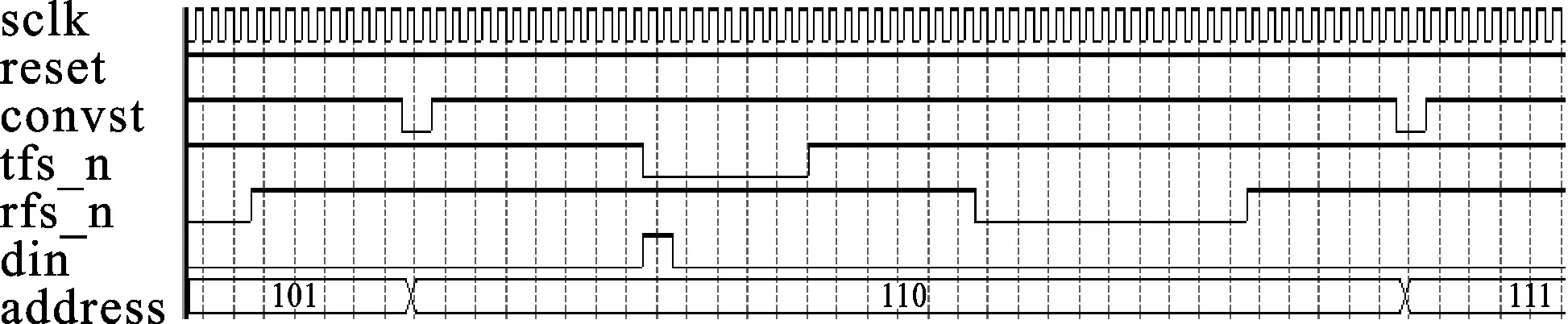

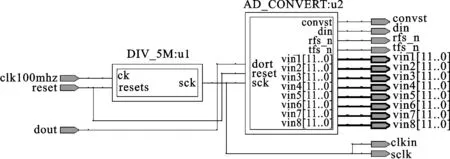

在Xilinx公司ISE 10.1软件平台下[10],使用VHDL硬件描述语言进行逻辑描述,A/D控制逻辑包括系统顶层模块、时钟分频模块、A/D读写控制输入输出模块。使用状态机来设计通道产生及串行数据控制时序,AD7890控制时序图及生成模块原理图分别如图7、8所示。

图7 AD7890控制时序图

图8 A/D转换控制模块图

顶层结构体定义源程序:

entity AD7890_top is

port(clk100mhz : in std_logic; ——系统时钟

reset : in std_logic; ——复位信号(低有效)

dout : in std_logic; ——串行输入端口信号

sclk : out std_logic; ——AD输入时钟

clk_in : out std_logic; ——AD内部工作时钟

rfs_n : out std_logic; ——接收帧同步信号(低有效)

tfs_n : out std_logic; ——发送帧同步信号(低有效)

din : out std_logic; ——控制命令串行输出端口信号

convst : out std_logic; ——转换控制标志

/*8通道串行数据*/

vin1 : out std_logic_vector(11 downto 0);

…

vin8 : out std_logic_vector(11 downto 0));

end AD7890_top ;

A/D转换接收串行数据部分源程序如下:

elsif (sclk’event and sclk=’1’) then

case state is

when state0=> if(count<12) then

tfs_n<=’1’;

count:=count+1;

state<=state0;

else

count:=0;

state<=swrite0;

end if;

/*输入控制字*/

when swrite0=> tfs_n<=’0’;

din<=address(2);

state<=swrite1;

…

when swrite3=> din<=’0’;

state<=swrite4;

when swrite4=> din<=’0’;

state<=swrite5;

/*串行数据输出:1位起始,3位地址,12位数据*/

when sread1=>state<=sread2;——串行输出起始位

when sread2=> tempaddr(2)<=dout; ——串行输出地址位和数据位

…

when sread16=> tempdata(0)<=dout;

state<=sread;

…

when converse=>

if(count<9) then

count:=count+1;

state<=converse;

else

count:=0;

state<=select;

convst<=’0’;

end if;

/*通道地址选择输出*/

when select=> case tempaddr is

when "000"=>

vin1<=tempdata;

…

when "111"=>

vin8<=tempdata;

when others=>NULL;

end case;

if address<"111" then

address<=address+"001";

else

address<="000";

end if;

state<=sover;

…

end case;

3 基于Virtex-4处理器硬件开发环境下的程序下载验证

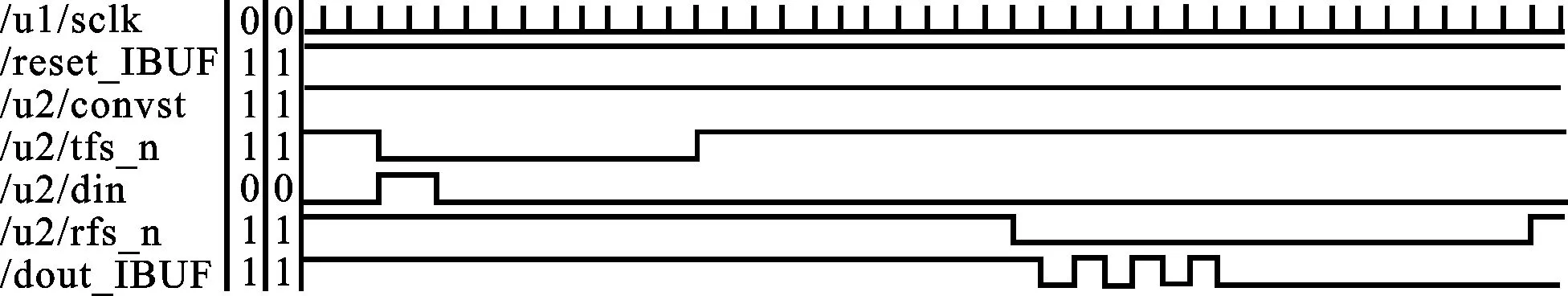

在ISE软件环境下进行综合、布局布线后,将程序下载到光电仪器便携式多功能信号处理采集系统硬件中(图9为实物图),使用在线逻辑分析仪ChipScope[11]采集信号数据,得到AD7890控制时序及功能仿真测试图,图10、图11是分别在AD7890第6通道输入5 V模拟量和第7通道输入3 V模拟量的时序控制及串行数据输出图。

图9 实验实物图

图10 5V模拟输入时序控制及串行数据输出

图11 3V模拟输入时序控制及串行数据输出

由图10、图11可以看出,FPGA实现了对AD7890的正确控制,AD7890输出的二进制数与理论计算结果完全一致。实验中在第6通道(101)、第7通道(110)分别接入5 V和3 V模拟量,由图10、图11的dout得到的AD7890输出的二进制码分别是101_010000000000和110_001001100111。前面3位是通道码,后面的12位是转换的二进制数据,010000000000对应的十进制数的1024,001001100111对应十进制数的615,用公式(1)将其换算为输入模拟量。式(1)中LSR、FSR分别表示AD7890允许输入的最大模拟量(10 V)和最小模拟量(-10 V),以6通道转换成的二进制数010000000000为例,计算结果为5 V,这与加入到6通道的模拟量完全一致,对于7通道情况完全类同。

(1)

4 结 论

本设计和实验实现了用FPGA对AD7890的正确控制,充分发挥了AD7890高速高精度特点,选用FPGA作为控制器件,使得数据采集硬件更加简单,控制更加灵活,集成化程度进一步提高,这对光电仪器外场数据采集系统来说是重要的。

参考文献:

[1]黄浦, 杨秀丽, 李军, 等.多通道模/数转换器AD7890与DSP的接口设计[J].现代电子技术, 2009, (22): 213-215.

Huang Pu, Yang Xiuli, Li Jun, et al.Interface design between multi-channel A/D convertor AD7890 and DSP[J].Modern Electronics, 2009, (22):213-215.

[2]汤楠, 李明.AD7890型串行数/模转换器与51系列单片机的接口设计[J].国外电子元器件, 2006, (8): 4-7.

Tang Nan, Li Ming.Design of interface between serial A/D converter AD7890 and 51 series single-chip microcomputer[J].International Electronic Elements, 2006, (8): 4-7.

[3]黄荣兰,万德焕.基于FPGA的A/D转换采集控制模块设计[J].数据采集与处理, 2009, 24(S): 237-240.

Huang Ronglan, Wan Dehuan.Design of A/D convertion sampling control module based on FPGA[J].Journal of Data Acquisition & Processing, 2009, 24(S): 237-240.

[4]陈钰利, 曾成志, 郑海荣,等.基于ADS6122和FPGA的多通道信号采集系统的设计[J].电子器件, 2012, 35(4): 406-411.

Chen Yuli, Zeng Chengzhi, Zheng Hairong, et al.Design of multi-channel data acquisition system based on ADS6122 and FPGA[J].Chinese Journal of Electron Devices, 2012, 35(4): 406-411.

[5]贺秋实, 郝国法, 钱龙.基于FPGA的高速AD转换[J].电子设计工程, 2012, 20(8): 122-124.

He Qiushi, Hao Guofa, Qian Long.AD conversion with high speed based on FPGA[J].Electronic Design Engineering, 2012, 20(8):122-124.

[6]徐园,靳根,王希涛,等.ARM与AD7656-1的多通道数据采集系统设计[J].核电子学与探测技术, 2012, 32(8): 914-917.

Xu Yuan, Jin Gen,Wang Xitao, et al.The design of multi-channel data acquisition system between ARM and AD7656-1[J].Nuclear Electronics & Detection Technology, 2012, 32(8): 914-917.

[7]田耘,徐文波,胡彬.Xilinx ISE Design Suite 10.x FPGA开发指南[M].北京:人民邮电出版社, 2008: 26-38.

[8]Analog Devices Inc.LC2MOS 8-Channel, 12-Bit Serial Data Acquisition System AD7890 Data Sheet[EB/OL].http:∥www.ananlog.com/static/imported-files/data_sheets/AD7890.pdf, 2013-5-20.

[9]赵慧洁,刘小康,张颖.声光可调谐滤波成像光谱仪的CCD成像电子学系统[J].光学精密工程, 2013, 21(5): 1291-1296.

Zhao Huijie, Liu Xiaokang, Zhang Ying.CCD imaging electrical system of AOTF imaging[J].Optics and Precision Engineering, 2013, 21(5): 1291-1296.

[10]赵吉成,王智勇.Xilinx FPGA设计与实践教程[M].西安:西安电子科技大学出版社, 2012: 26-40.

[11]田耘, 徐文波.Xilinx FPGA 开发实用教程[M].北京: 清华大学出版社, 2008: 295-316.