可配置并行HEVC去块滤波VLSI设计

2014-03-26路伟余宁梅南江涵王冬芳

路伟,余宁梅,南江涵,王冬芳

(西安理工大学 自动化与信息工程学院,陕西 西安 710048)

HEVC(High Efficiency Video Coding)图像编码是基于图像块进行的DCT/DST(Discrete Cosine Transform/Discrete Sine Transform)变换量化的,因而会导致图像块的边界处重构像素的精度低于块内部重构像素数据的精度,从而导致了边缘块效应。这种块效应会影响到编码压缩的效率,也会影响到解码出图像的清晰度。因此是当前的高清视频编解码技术所必须考虑的一个重要问题。去块滤波技术可以在不明显影响图像内容的情况下去除方块效应的影响,显著提高重构图像的主客观质量,是改善图像块效应的有效方法。文献[1]针对H.264与HEVC去块滤波算法的异同进行了研究,并列出相关数据说明了HEVC中去块滤波算法的低码率方面优于H.264。文献[2]针对HEVC的算法,提出了一种基于判决条件的快速算法,用来确定其滤波强度以及滤波方式。文献[3]针对需要滤波块中像素点间的相关性,提出了一种低复杂度的感知优化,用以降低滤波器的计算复杂度。文献[4]是最新的草案定稿版,将历届会议提案中有关去块滤波部分的最优算法列入其中,提高了去块滤波处理效率。但是,以上研究都在算法层面展开。由于 HEVC是靠增加编码复杂度来获得编码效率的提升,编解码时间也随之大幅增加。采用软件对图像进行去块滤波处理,处理时间过长,不能满足实时处理要求。为了提高处理速度,采用硬件加速的方式势在必行。在HEVC编解码系统中,去块滤波是非常重要也是占用编码时间多的模块之一,对HEVC去块滤波模块的VLSI实现进行研究,提高超高清视频的编码速度具有重要意义。在HEVC去块滤波的VLSI研究方面,文献[5]采用四级流水线结构,完成了滤波边界的判断、滤波强度判断、参数选取、强弱滤波的实现,同时采用内存交互技术根据滤波顺序进行数据调度,增大了滤波数据的吞吐率。但是,内存交互技术和流水线中模块的计算有着密切的关系,在数据流控制上比较困难,并且容易造成数据地址错误的情况。文献[6]采用由水平和垂直两个方向组成的8×8寄存器阵列来计算四叉树子块的边界滤波。并且采用总线技术将多种分割模式的滤波块逐一调度,利用寄存器阵列进行滤波计算。但是,这种总线调度寄存器阵列结构在SOC系统中有一定瓶颈,并且易受DDR控制器带宽和总线带宽的约束,对数据处理有一定局限性。

基于以上原因,本文对HEVC去块滤波算法结构进行分析,设计了转置矩阵模块。在不改变算法滤波顺序的基础上,采用转置模块对数据进行暂存,以此减少数据重复读取操作,进而解决了ASIC架构中去块滤波模块面积资源消耗大的问题。

1 去块滤波的算法

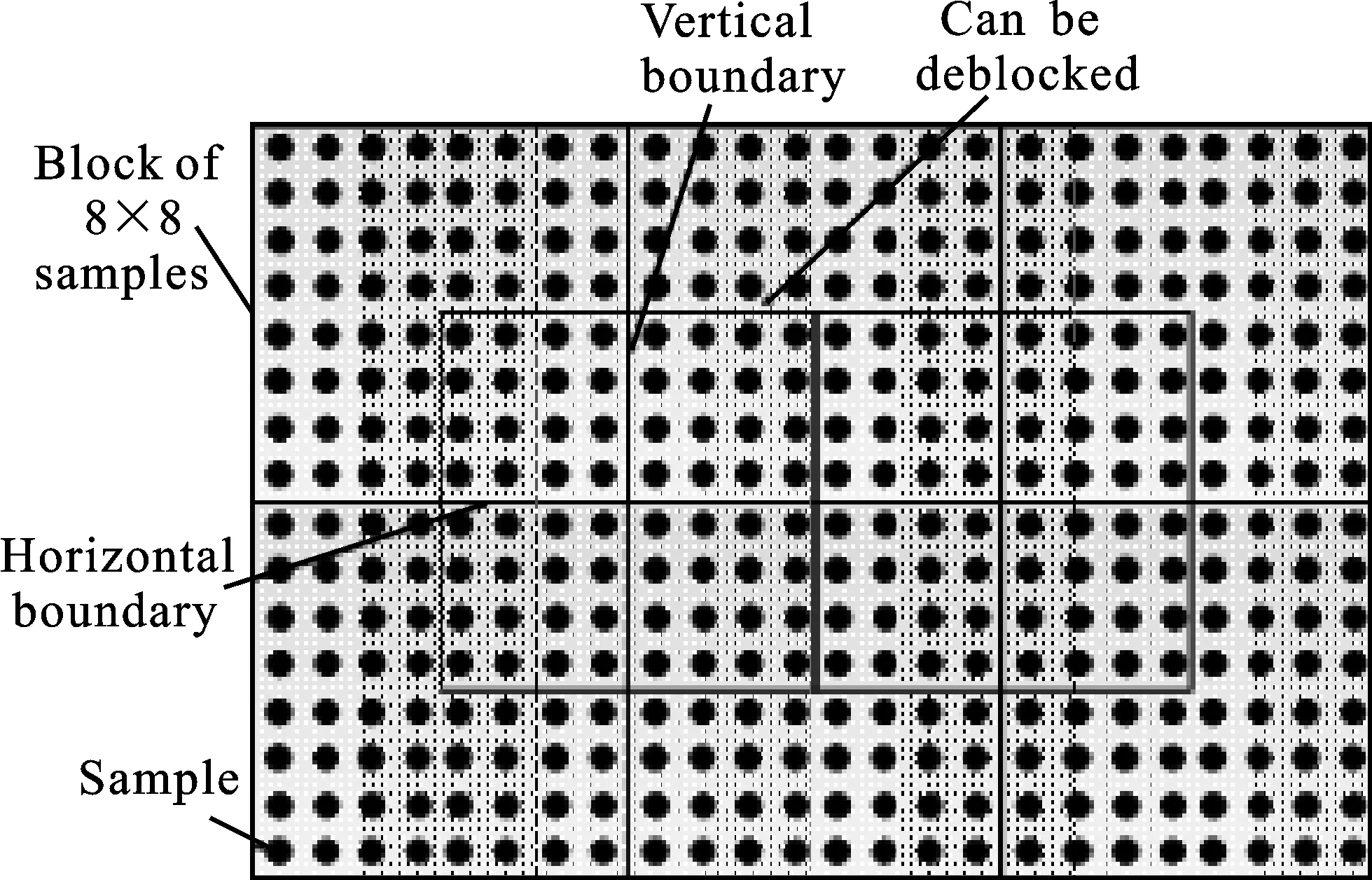

HEVC去块滤波是为了减少各单元(CU(Coding Unit)、PU(Prediction Unit)、TU(Transform Unit))边界的块效应而采用的一种滤波方式。HEVC为了利于简化硬件设计和并行处理,将滤波的基本单元设置为8×8块大小的单元。由于CU、PU、TU是按照四叉树分割方式将LCU(Largest Coding Unit)从64×64大小的块分为32×32、16×16、8×8大小,从而对相应的边界进行去块滤波处理[7]。去块滤波的方式如图1所示,图1中每个黑色的圆点代表了单元块中的一个像素点(Sample)。图1由6个8×8大小的块组成了待滤波的区域,其中Block of 8×8 sample指向了其中一个8×8块。6个8×8块中的两个方框是需要进行滤波的两个滤波区域(Can be deblocked),图1标出了需要进行滤波的位置,分别是水平边界(Horizontal boundary)和垂直边界(Vertical boundary)[8]。由图1可以看出,垂直边界和水平边界都在需要滤波的区域中,并且两个需要滤波区域的参考像素点Sample是互不相关的,即这两个滤波区域可以单独完成滤波。

图1 PU滤波方式

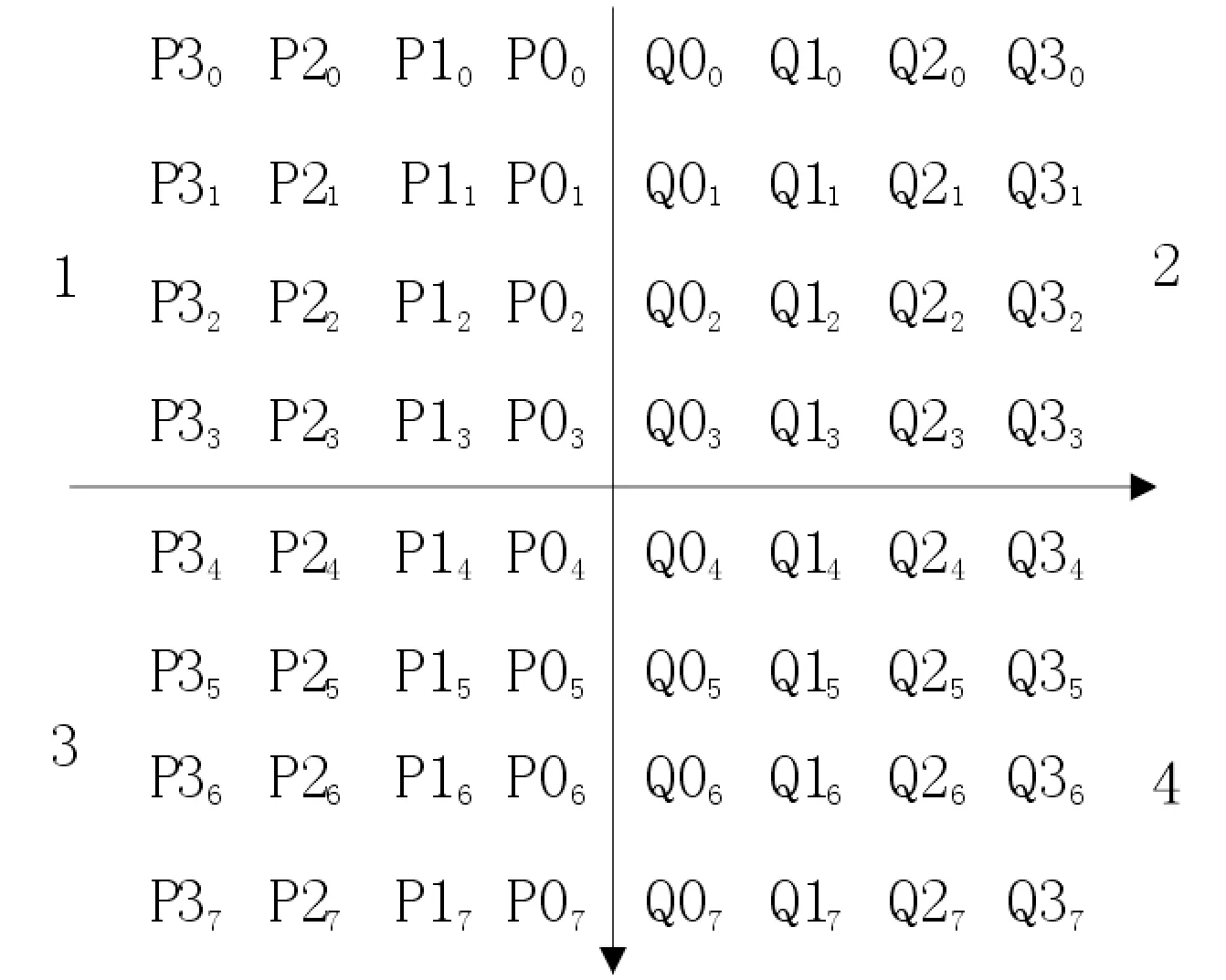

HEVC去块滤波的基本单元块是8×8块,其边界选择在8×8块边界区域,每个8×8块的边界分别和自己相邻的8×8块边界组成了去块滤波的边界,如图1所示。左边需要滤波区域由四个相邻的8×8块组成的滤波边界。依次是左上8×8块的右下4×4块,中上8×8块的左下4×4块,左下8×8块的右上4×4块,中下8×8块的左上的4×4块。这4个4×4块的相邻边界分别组成了垂直边界(Vertical boundary)和水平边界(Horizontal boundary)[9]。得到的滤波基本单元块,如图2所示。首先对垂直边界进行滤波,会用到水平方向的8行数据,P3iP2iP1iP0i, Q0iQ1iQ2iQ3i(i=0…7)。垂直边界滤波完成后,需要对水平边界进行滤波。此时,需要用到之前经过滤波后,垂直方向的8列数据,Pij(i=3,2,1,0.j=0…7)和Qij(i=3,2,1,0,j=0…7)。水平边界的滤波完成后,就可将得到去块滤波后的最终数据。

图2 去块滤波的边界

其滤波的算法是采用P和Q点进行滤波。下面以一行(列)为例说明:

强滤波:

p0′=(p2+2·p1+2·p0+2·q0+q1+4)≫3

(1)

q0′=(p1+2·p0+2·q0+2·q1+q2+4)≫3

(2)

p1′=(p2+p1+p0+q0+2)≫2

(3)

q1′=(p0+q0+q1+q2+2)≫2

(4)

p2′=(2·p3+3·p2+p1+p0+q0+4)≫3

(5)

q2′=(p0+q0+q1+3·q2+2·q3+4)≫3

(6)

弱滤波:

Δ定义为:

Δ=(9·(q0-p0)-3·(q1-p1)+8)≫4

(7)

当abs(Δ)小于tc·10时,有:

Δ=Clip3(-tc,tc,Δ)

(8)

p0′=Clip1(p0+Δ)

(9)

q0′=Clip1(q0-Δ)

(10)

如果dEp1 = 1,则:

Δp=Clip3(-tc≫1),tc≫1,(((p2+p0+1)≫1)-p1+Δ)≫1)

(11)

p1′=Clip1(p1+Δp)

(12)

如果dEq1=1,则:

Δq=Clip3(-tc≫1),tc≫1,(((q2+q0+1)≫1)-q1-Δ)≫1)

(13)

q1′=Clip(q1+Δq)

(14)

其中p1′和q1′(i=0,1,2)是滤波后的像素值。

2 去块滤波硬件结构

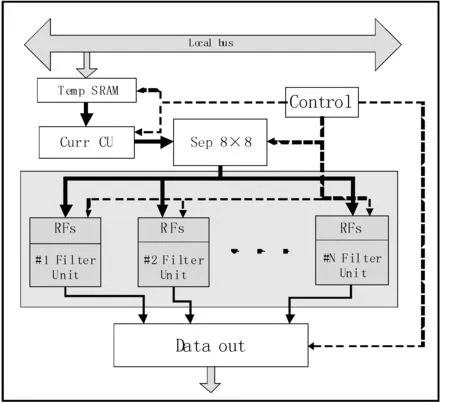

由以上算法原理可知,HEVC滤波将CU、PU、TU按照四叉树方式分割并对边界进行滤波,并且划分出来的每个需要滤波单元都是相互独立的[10]。根据这一原理,本研究设计了图3所示滤波单元数可配置的并行滤波结构。首先,通过Local bus得到重构数据及相应的参数(参数中包含有LCU经四叉树的分割信息),将重构数据及相应的参数暂存到Temp SRAM中。通过Control控制器将重构数据中需要滤波的CU块及参数信息存入Curr CU中。在Curr CU模块中根据分割参数信息,将CU块按照预测分割方式分成了多个PU块,将这些PU块及参数按照顺序依次送入Sep 8×8模块。在Sep 8×8中将PU块按照四叉树分割方式分割到8×8大小块为止。从8×8块中取出需要进行滤波的数据及相应的参数,并将其排序,依次送入下面的Filter Unit中。Filter Unit模块接收需要进行滤波的数据及相关的参数信息进行滤波处理。这里采用可配置并行处理的方式,设置了N个滤波处理单元Filter Unit进行并行处理。N的数值越大,Filter Unit单元数越多,可同时处理滤波单元就越多,处理滤波数据的速度越快,吞吐量越大。反之,N的数值越小,Filter Unit单元数越小,可同时处理滤波单元就越少。对于一个LCU会有若干个边界需要滤波,其中32×32分割块的边界有8个8×8的边界,垂直边界和水平边界各4个,16×16、8×8分割块分别含有4个和2个8×8边界。为了保证分割块能够按照算法中给定的顺序进行处理,将设计中的滤波单元数量N设置为2的倍数。将滤波的顺序进行排序依次处理。假设Filter Unit单元数为4,当待处理的分割块为32×32、16×16、8×8时,一次可进行的水平或者垂直滤波的分割块数分别为1、2和4个。各个Filter Unit单元处理完成后得到了滤波后的数据,通过Control控制Data out模块,N个并行的滤波数据按照之前定义的顺序输出数据。

图3 去块滤波结构图

2.1 去块滤波单元结构

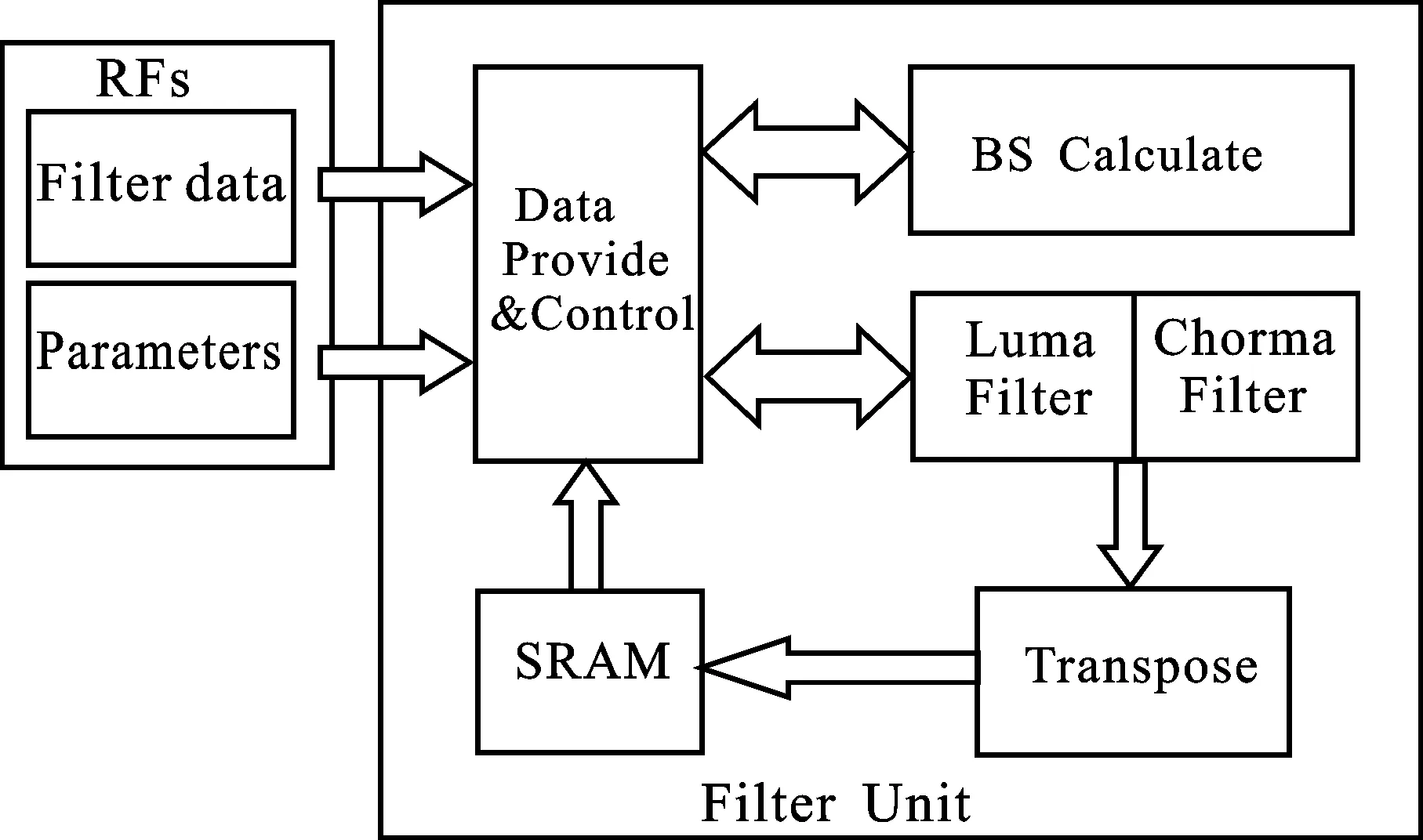

HEVC去块滤波单元硬件系统的核心模块有:滤波强度计算模块(BS Calculation)、亮度块滤波模块(Luma Filter)、色度块滤波模块(Chroma Filter)、转置模块(Transpose)、数据供给和控制模块(Data Provide & Control)和数据缓存(SRAM)。

去块滤波单元结构和模块间的数据流走向如图4所示,即:

① 将重构图的PU或者TU中需要进行滤波的像素点和相应的参数值输入RFs暂存,等待滤波处理。RFs保存了待滤波的数据和相应的参数值。

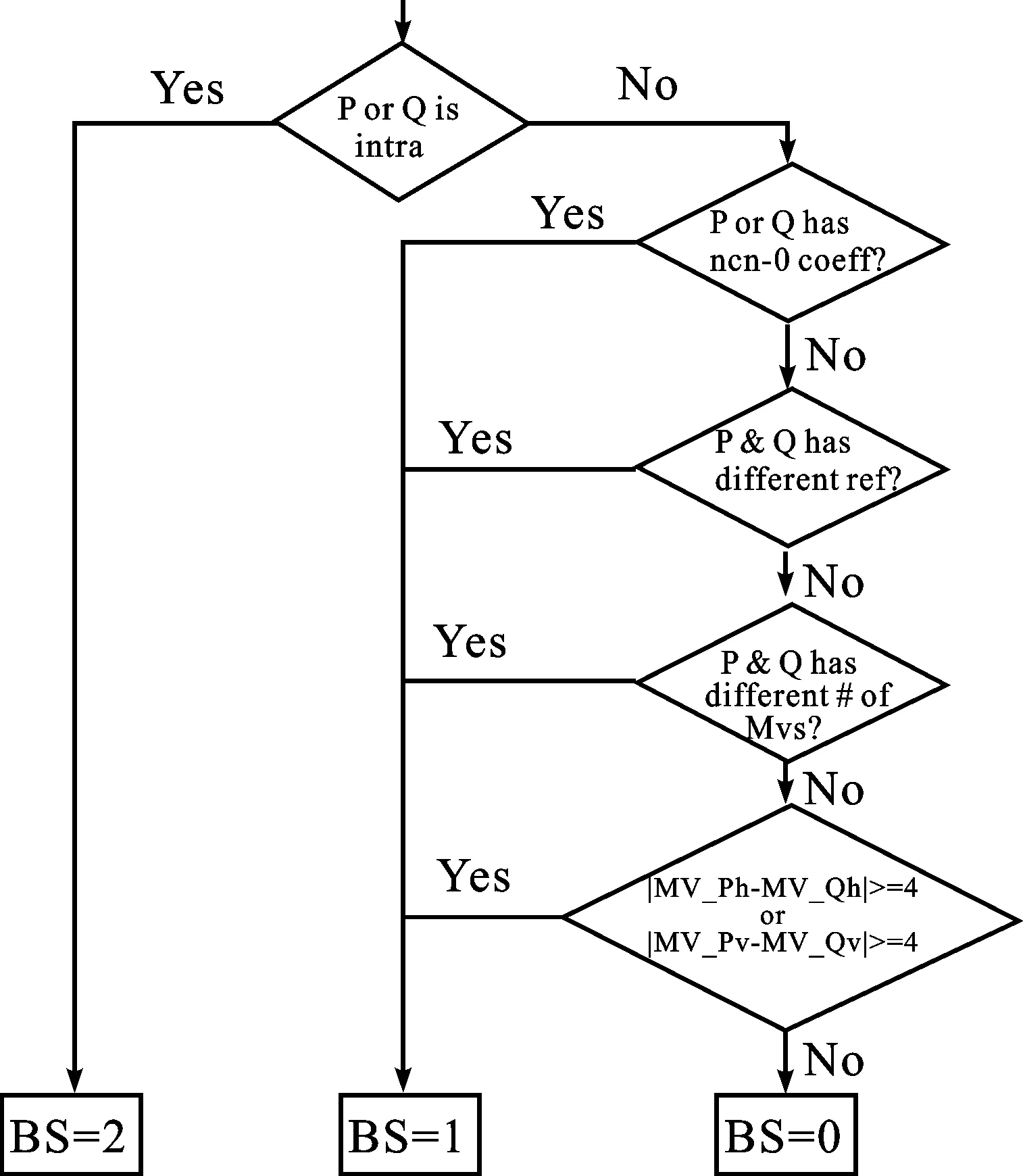

② 待滤波的像素点和参数准备好后,将8×8的每行(列)的8个像素信息,经由Data Provide & Control模块传输给BS Calculation模块进行相应行(列)滤波强度值计算。此处需要根据整体编码器中的帧内、帧间模式以及相邻快的信息进行判断。具体处理的方式为,当BS=2时使用强滤波、当BS=1时使用弱滤波、当BS=0时不滤波。具体判断方式如图5所示。

图4 去块滤波单元硬件结构

图5 BS计算流程图

对于当前块Q或相邻块P为帧内预测模式且边界为宏块边界的BS=2,即为强滤波。当前块Q或相邻块P有非零coeff、当前块Q或相邻块P有不同的参考像素、当前块Q或相邻块P有不同的MVS、|MV_P - MV_Q|>=4,符合这几种情况的BS=1,即为弱滤波。凡不属于以上几种情况的BS=0,即为不滤波。

③ 当整个8×8块的滤波强度值计算完毕后,会返回Data Provide & Control模块一个滤波强度值,这个滤波强度值决定了接下来要采用的滤波是强滤波还是弱滤波。

④ 滤波强度计算完成后,系统开启Luma filter,向其中每次输入8行8个亮度像素信息以及已经准备好的亮度边界滤波强度值。经过滤波计算后,8×8亮度块重新返回至Data Provide & Control模块内。

⑤ 4×4色度滤波与亮度滤波相似。每次向Chorma filter输入4行4个色度像素信息和色度边界滤波强度值。经过滤波计算后,4×4色度块重新返回至Data Provide & Control模块内。

⑥ 由于每次只能进行垂直滤波或者水平滤波,因此,按照滤波顺序,需要将8行亮度块的像素点和4行色度块的像素点先进行垂直滤波。滤波完成后,会被输入至Transpose模块内,进行像素矩阵转置。经过转置的模块会被暂时存入SRAM中,用于水平滤波。

⑦ 当所有亮度块垂直边界滤波完成,且经过转置存入SRAM后,Data Provide & Control模块会提取SRAM中经过转置的亮度块,输入亮度滤波模块,进行水平滤波。从步骤2开始重复上面的操作,完成水平滤波。同样,色度滤波也会有这样的操作。

2.2 转置模块的设计

HEVC算法中去块滤波的顺序是,首先,对LCU的所有CU、PU、TU的垂直边界进行滤波,将滤波后的数据存入外部存储。当所有垂直边界滤波完成后,用已经垂直滤波完成后的sample值对LCU的所有CU、PU、TU的水平边界进行滤波。硬件设计中如果按照算法的顺序进行滤波设计,垂直滤波后的数据需要通过Local Bus进行存储。当所有的垂直边界滤波完成后,需要再次通过Local Bus调取垂直边界滤波完成后的数据进行水平滤波。这样会使得系统需要对Local Bus进行数据读和取操作,从而影响系统的处理速度。为了能够让垂直滤波后的数据不需要通过Local Bus存入外部存储,而直接被水平滤波使用。本文对垂直边界滤波完成后的数据进行转置、暂存的操作,从而使垂直边界滤波完成后的数据进行后续水平边界滤波的处理操作。采用这种设计可以提高数据利用率,增加模块的复用性,减少对于外部存储的依赖,使得去块滤波系统变的高效。

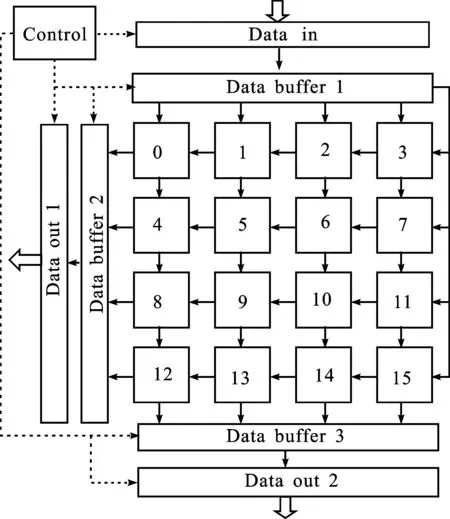

图6给出了以4×4为例的色度转置模块结构图。首先,垂直滤波完成后的数据存入Data in中,数据保存并由Control模块控制,每次只读出4×4块的一行数据。将读出的第一行数据送给Data buffer 1。Data buffer1按照一行相应的位置送入移位寄存器模块分别是0、1、2、3,同时第二行数据进入Data buffer 1。经过一个时钟周期后,第二行的Data buffer 1数据按照行相应的位置送入移位寄存器模块0、1、2、3,而此时第一行的0、1、2、3内的数据移位到相应位置4、5、6、7。依次类推,4个时钟周期运算后一个4×4块就可以完成寄存器组的移位。然后,将0、4、8、12送入Data buffer 2,同时将后面列依次向左移位。经过一个时钟周期后,Data buffer 2将数据按照顺序传给Data out 1,就得到了第一列的数据。此时,下一个色度块的第一行数据从Data buffer 1给3、7、11、15。依次类推,4个时钟周期后就得到4个列的数据,此时下一个色度块的数据已经全部在寄存器组中,Control控制寄存器组向下移位,重复以上操作,从Data buffer 3输出给Data out 2。依次循环下去。

按照以上步骤就可以实现滤波的转置,并且是按照流水级运行,能够提高数据处理能力。对于亮度8×8块,需要将寄存器组设计为8×8,原理与色度转置模块一致。

图6 色度转置模块

3 实验结果分析

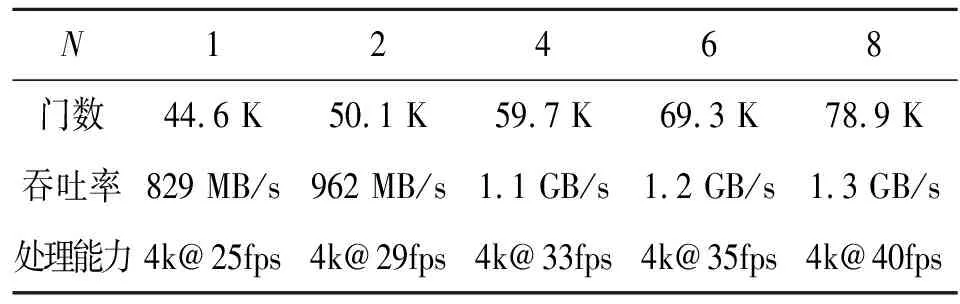

本文以HEVC去块滤波算法为基础,研究设计了去块滤波的VLSI实现方式,利用8×8滤波块可独立进行滤波的特性,设计了可调滤波单元个数的并行结构。可配置滤波单元数为N个,N越大滤波单元越多,处理效率越高,吞吐率越大,但面积会增加;N越小滤波单元越小,处理效率和吞吐率会下降,但面积会减少。根据算法中分割块滤波边界的特点,对采用可配置滤波单元数进行计算,得到表1所示数据。可看到,随着N的增加,门数、吞吐率、处理能力也有所增加。

在设计过程中分别对N=1、2、4、6、8时的设计进行了综合,得到了相应的门数。对于吞吐率的计算本研究根据设计中采用流水线技术,每个滤波单元可处理相应的一个块的一行(列)数据。本研究首先计算出N=4时的吞吐率约为1.1 GB/s,再根据每个滤波单元能够处理261 MB/s的数据得出N为其他值时的吞吐率。处理能力是在相应吞吐率基础上计算得到。

表1 N配置表

本文采用了转置矩阵的方式对数据进行暂存,而并非采用直接将每行(列)计算完的数据先存储起来。等所有的行(列)的数据都计算完后,再对数据按照行、列转置的方式依次输入给滤波模块计算下一步的列(行)的数据。因此,这样可在存储单元上减少一定的面积。结合可配置滤波单元数的方式,当要达到高效处理数据单元的时候存储单元减少的面积数就会更多。

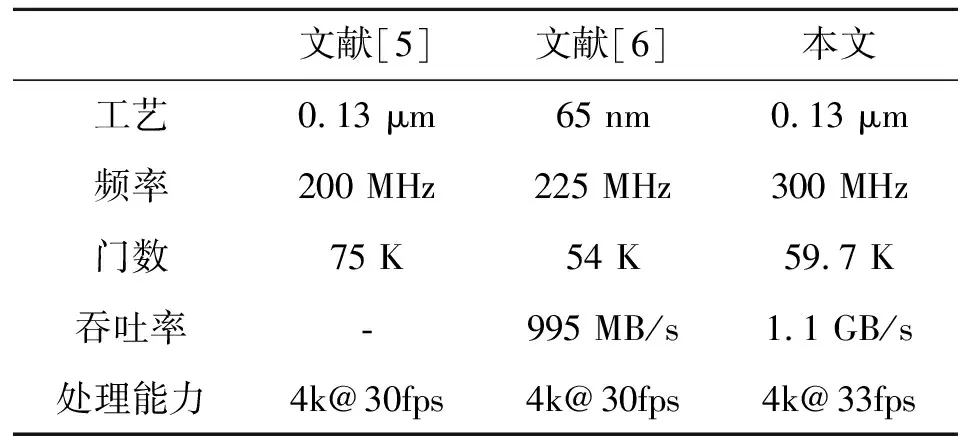

为了能够保证高清视频编码4 K视频序列的流畅性的最低要求,帧率需要每秒达到30帧。本文采用N=4,即4个并行的滤波处理单元进行处理操作,这样可用相对较小的硬件资源消耗达到流畅性的最低要求。在此配置下,表2说明了本研究的设计和参考文献的比较。相同工艺参数下,比文献[5]所提及的门数少、处理能力高。比文献[6]门数多5.7 K,但是数据吞吐率和处理能力都比文献[6]高。

表2 资源消耗表

4 结 论

1)以HEVC去块滤波算法为基础,设计了去块滤波的VLSI实现方式。

2)利用滤波块间相互独立进行滤波的特性,设计了可配置滤波单元个数的并行结构,给出了实现框图。并针对滤波先垂直后水平的滤波顺序,设计了转置模块,将垂直滤波后的数据进行转置。为了避免使用系统总线进行数据重复读取,而有可能降低系统处理数据的效率,把转置后的数据暂存在SRAM中,为水平滤波提供实时的数据,以提高流水线运行效率。

3)使用 SMIC 0.13 μm的工艺库参数,综合后在300 MHz下,配置滤波单元数为4个,系统总门数为59.7 K,可以实时处理3840×2160@33fps的图像序列。

参考文献:

[1]Zhou M, Sze V, Mastuba Y.A study on HEVC parsing throughput issue:joint collaborative team on video coding[C].Torino, JCTVC-F068, 2011.

[2]Sullivan G J, Ohm J R, Han W J, et al.Overview of the high efficiency video coding (HEVC) standard[J].IEEE Transcation Circuits and Systems for Video Technology, 2012, 22(9): 1649-1668.

[3]Naccari M B, Ascenso C.Low complexity deblocking filter perceptual optimization for the HEVC code:2011 18th IEEE international conference on image processing (ICIP)[C].Brussels,2011:159-163.

[4]Bross B, Han W J, Ohm J R, et al.High efficiency video coding (HEVC) text specification draft 10 (for FDIS & Consent):JCTVC-L1003_v25[C].Geneva ,2013:190-220.

[5]Shen weiwei, Shang Qing, Shen Sha, et al.A high-throughput VLSI architecture for deblocking filter in HEVC:IEEE international symposium on circuits and systems (ISCAS)[C].Beijing:China,2013:673-676.

[6]Jongwoo B.Register array-based VLSI architecture of H265/HEVC loop filter[J].IEICE Electronics Express,2013, 10(7):1-9.

[7]Ohm J R, Sullivan G J, Schwarz H, et al.Comparison of the coding efficiency of video coding standards including high efficiency video coding (HEVC)[J].IEEE Transactions on Circuits and Systems for Video Technology, 2012, 22(12): 1669-1684.

[8]Bross B, Han W J, Ohm J R,et al.High efficiency video coding (HEVC) text specification draft 10 (for FDIS & Consent):JCTVC-L1003[C].Geneva ,2013: 179-201.

[9]Bossen F, Bross B, Sühring K.et al.HEVC complexity and implementation analysis[J].IEEE Transactions on Circuits and Systems for Video Technology, 2012, 22(12): 1550-1561.

[10]Andrey Norkin, Gisle Bj ntegaard, Arild Fuldseth HEVC deblocking filter[J].IEEE Transactions on Circuits and Systems for Video Technology, 2012, 22(12):1801-1809.