针对FPGA密码芯片的近场差分电磁分析攻击

2013-07-20陈开颜吴恒旭

陈开颜,余 浩,邹 程,吴恒旭

1.军械工程学院 计算机工程系,石家庄 050003

2.中国人民解放军78086部队

针对FPGA密码芯片的近场差分电磁分析攻击

陈开颜1,余 浩1,邹 程1,吴恒旭2

1.军械工程学院 计算机工程系,石家庄 050003

2.中国人民解放军78086部队

1 引言

由于嵌入式密码芯片设备的开放性(芯片外部各种信号易于测量),近年来针对密码芯片出现了称为旁路攻击(又称为旁路密码分析、侧信道攻击等,Side Channel Attacks,SCAs)的新型密码分析技术[1],利用密码芯片工作时的功耗、电磁辐射、运行时间等信号(称为旁路信号)中蕴含的与芯片内部运算相关的信息,采用分而治之的思想将密钥分成若干块进行分析,在获取各个子密钥之后拼接得到完整的密钥,表现出了强大的攻击能力,开辟了密码学和密码分析学的新领域。在旁路攻击领域之中,目前研究最为广泛,成果最为突出的当属功耗分析攻击,它是利用密码设备在进行密码运算时产生的功耗信息,来推导出运算中的秘密参量。然而,在针对现场可编程门阵列(Field Programmable Gate Array,FPGA)密码芯片进行功耗攻击时,由于实际电路中设置的一些解耦电容或者作为本地能量存储的滤波电容以及电路中的其他电子元器件对电路板中电流变化的额外作用,往往使得测量核心部件的功率消耗很困难,即使获取到功耗信号,由于信号中包含的是整个FPGA电路中所有元器件的功耗泄漏,因此需将密码运算核心部件产生的功耗与其他大量辅助部件产生的功耗进行逻辑上的剥离,这也是非常困难的。此外,如果密码设备采用内置电源方式甚至使得功耗分析攻击变得不可行。

电磁分析攻击又称电磁辐射攻击(Electromagnetic Emanation Attacks),是通过测量密码芯片在运算期间发射的电磁信号,依据电磁场与内部处理数据之间的相关性而获取内部秘密参量。电磁分析攻击分为简单电磁分析(Simple ElectroMagnetic Analysis,SEMA)攻击和差分电磁分析(Differential ElectroMagnetic Analysis,DEMA)攻击。在进行电磁分析攻击时,可以用探头探测核心部件的表面电磁辐射,直接定位于运算部件之上,最大限度地获取有用的旁路电磁信号,完成非入侵式攻击[2]。

本文在SPANTAN3系列的FPGA上,自行设计完成了AES密码电路,实现了针对FPGA密码系统的近场电磁辐射分析攻击,证明了由于整个芯片电路集成度高,导致敌手对芯片功耗难以测量,或者设计者实施的一些抗功耗分析攻击对策的影响,使得功耗分析攻击变得很困难时,敌手仍然可以通过精确定位、捕获与数据运算操作密切相关的电路元器件上所泄漏的电磁信息,从而最终破解密码系统的密钥。

2 密码芯片电磁泄漏信号描述

当前,超大规模集成电路(VLSI)芯片中应用最多的是CMOS技术,它被广泛运用在微处理器、微控制器以及其他数字逻辑电路之中。对CMOS电路,电磁辐射源自于控制、I/O、数据处理或器件其他部分的电流,按照类型通常将其分为直接辐射与间接辐射[3]。对直接辐射,电磁场的特性取决于辐射源、源周围的介质和源到观测点的距离,根据距辐射源的远近,其相应的辐射区域分别称做近场(小于λ/2π的区域,λ表示波长)和远场(大于λ/2π的区域)。本文主要研究FPGA密码芯片的近场直接电磁辐射。

2.1 CMOS电路直接电磁辐射

根据电磁场理论[4]:导体上存在随时间变化的电荷和电流时,它的周围就有随时间变化的电场和磁场。电场和磁场是一个不可分割的整体,它们相互联系、相互激发组成一个统一的电磁场。电磁场间的相互作用,在一定的条件下离开导体向远处运动,形成向自由空间传播的电磁波,被称为电磁辐射。可以利用毕奥-萨伐尔定律描述磁场变化:

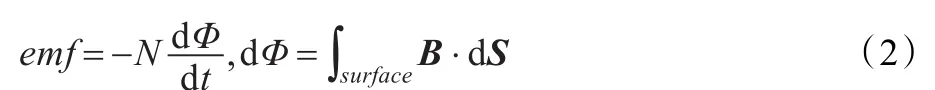

其中I是在无限长导体上的电流,µ为磁导率,r为电流与磁场间距离的向量。此外,法拉第定律表明环行探头所处环境的任何变化会在环中产生感应电动势:

其中N为线圈匝数,Φ为磁通量。如果假定总线可以看成是一条无限长的导线,用毕奥-萨伐尔方程表示如下:

其中r是与线之间的距离,αˆφ为与导线相关的单元向量。式(3)清楚地表示了探头离目标电路越近,测量到的磁场越强。

CMOS数字电路的基本组成单元是反相器,按图1所示,反相器可以看做是一个推拉开关:输入接地时切断下面的晶体管,产生高电平输出。高电平输入时刚好相反,将输出接地拉到低电平。当一个比特位从0翻转到1,或者从1翻转到0同样成立,反相器的NMOS管和PMOS管会导通一小段时间,这就导致一个从VDD到VSS的短暂的电流脉冲,而这个在CMOS门的输出变化时产生的电流会在芯片周围产生一个变化的电磁场,这个变化的电磁场可以用感应探头检测到。

图1 反相器原理图

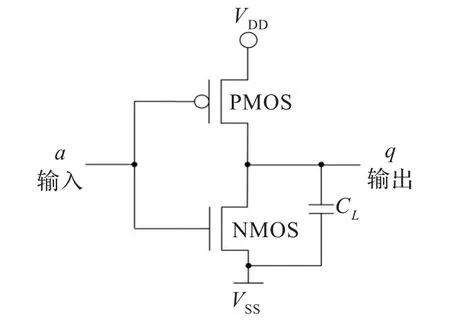

根据楞次定律,变化的磁场将在闭合导体中产生电流,探头中的感应电动势取决于磁通量的变化率,其表示如下:

其中v表示探头的输出电压,ΦB表示探头感应的磁通量,t表示时间,B表示磁场,而A表示磁力线穿透的区域面积。基于安培定理的麦克斯韦方程将磁场的产生表示如下:

其中J表示电流密度,E表示电场,ε表示电导率而µ表示磁导率。式(4)和式(5)说明探头的输出电压V与电流密度J和电场E成正比,也就是和翻转的晶体管数量成正比,即在一定时间内通过物理旁路泄漏的数据取决于该时间内从一个状态到另一个状态的翻转数[5]。

2.2 FPGA近场电磁辐射模型

现实中,由于集成电路芯片结构的差异,无法构建统一的电磁辐射模型。文中以SPANTAN3系列的FPGA为例,对其进行近场电磁辐射的建模。

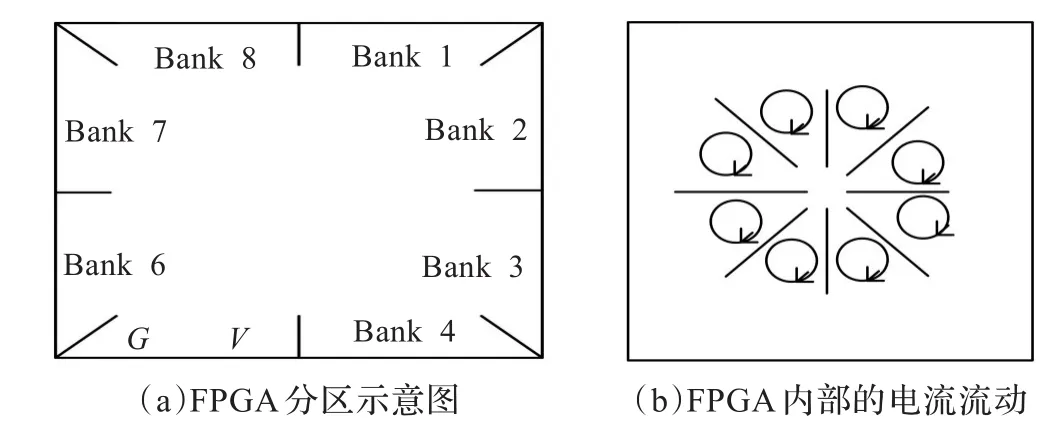

SPANTAN3系列的FPGA的物理结构一般被分成八个区(banks),每个区内都有内核电源(VCCINT)引脚和地(GND)引脚。如图2(a)所示,分析FPGA的内部电流特性时,可以认为在FPGA工作时,电流是从一个区的电源引脚(VCCINT)开始流动,通过区内电路,到该区的地(GND)引脚结束。近似的,可以认为FPGA中的电流从电源到地形成了许多的小的环形循环。如图2(b)所示,因此可以将这些环形电流建模为基本的磁偶极子。如果假设环的媒介对电磁是没有损耗的,并且认为电流环位于x-y平面,则环形磁偶极子的电磁场由式(6)进行定义。

图2 FPGA分区和内部电流流动示意图

其中,Zc是媒介的特性阻抗。在空气中它等于120π,kg表示波数,A表示环的面积,I是通过环的电流,r是从环中心到电磁点的距离。当测量近场电磁辐射时,它可以表示为式(7):

从式(7)可以得出FPGA近场辐射特性两个重要的结论:(1)场强依赖于数据的变化(即依赖于电流强度)。(2)场的方向直接依赖于电流的方向。

为测得磁场信号,应该使用磁场感应探头测量FPGA的近场辐射,接收FPGA近场辐射电磁波。探头的输出电压能够被示波器进行采集,并进行数字化存储。另外,根据式(4)、式(7)可知,如果FPGA被建模为一系列磁偶极子的集合,每个磁偶极子辐射不同的电磁信号,那么磁偶极子的位置,方向及采集探头的位置对电磁域的测量都是有影响的。这将直接影响电磁分析攻击的效果及所需样本量的大小。因此,应该在电磁分析攻击中充分考虑采集探头在FPGA表面所处的采集位置。

3 差分电磁分析攻击原理

以AES为例,首先作如下定义:

(1)N个随机的明文输入ti(1≤i≤N);

(2)K表示真实子密钥,ks(1≤s≤Μ)表示敌手第s种猜测子密钥,共包含Μ种猜测情况;

(3)p(ti)(1≤i≤N)为第i个明文加密所对应的电磁辐射曲线。

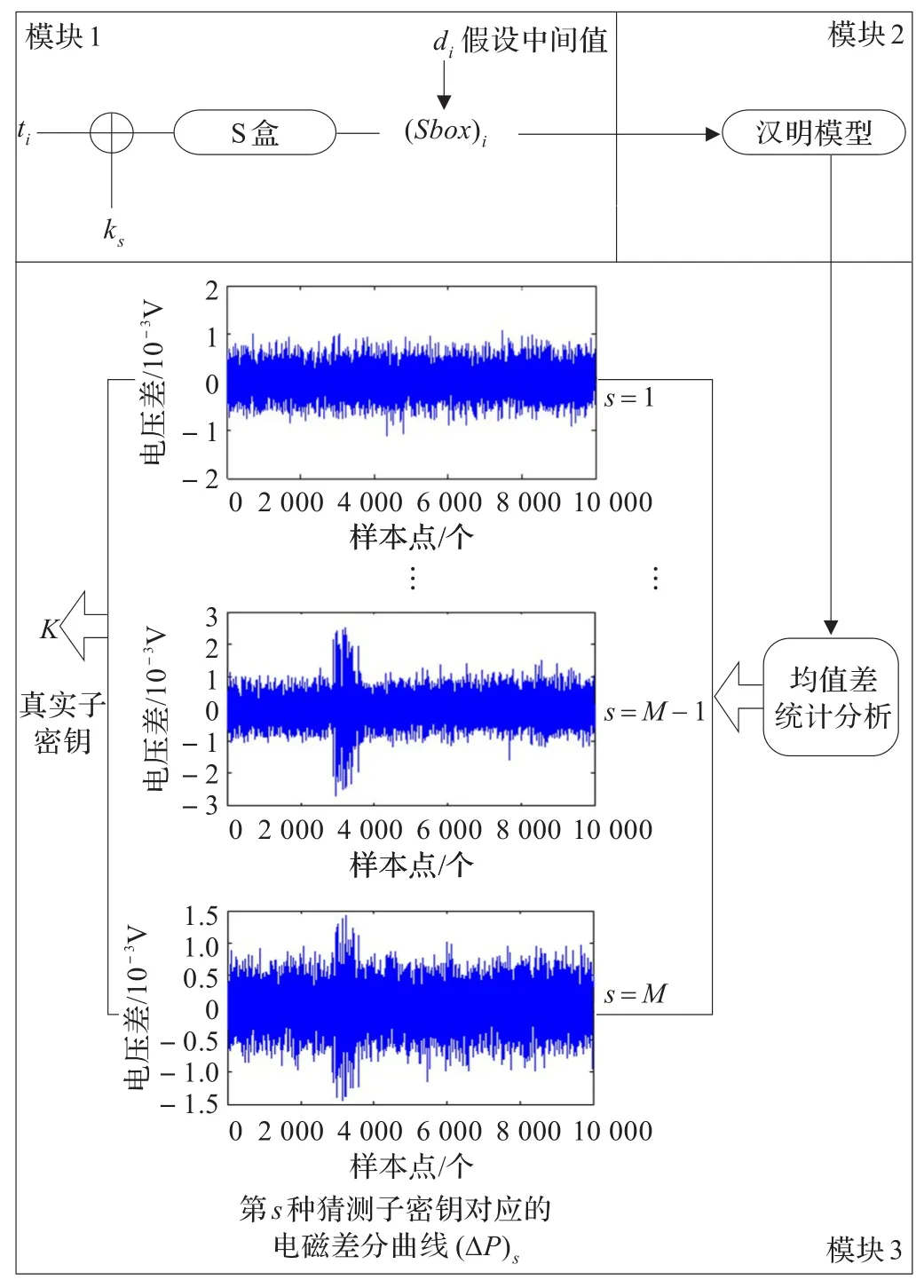

图3所示为差分电磁分析攻击原理示意图,共分为3个模块。

模块1分析中,敌手选择S盒输出(Sbοx)i中与电磁辐射信息密切相关的中间值di,即对应的猜测子密钥所计算的一位或多位假设中间值,示为:

图3 差分电磁分析攻击原理示意图

模块2旁路信号与芯片内部运算数据之间的相关性模型是联系数据和芯片电磁辐射信号的纽带,对敌手而言,需对选取的所有中间值结果进行数据相关性泄漏模型的构建。最后,根据模型计算假设中间值,把对应的电磁辐射曲线进行不同的划分。文中采用的旁路信号数据相关性模型为汉明重量模型[6]。

模块3敌手依据均值差统计分析结果判断所猜测的子密钥正确与否,若猜测子密钥正确,则所选假设中间值在其处理数据的区域会对芯片的电磁辐射表现出明显的影响效果,即明显尖峰的出现。通常,差分曲线幅值最大的就是影响效果最突出的,其对应的猜测子密钥也就应该是最可能的正确子密钥。用Dp表示基于假设中间值的电磁辐射影响效果曲线,即差分曲线,f[]表示一确定函数,用于计算差分曲线的幅值,可形式化表达为:

4 设计实现

AES是当前国际上最流行的商用对称加密算法,其前身是Rijindael算法[7]。AES算法是一个使用可变分组和密钥长度基于有限域运算的迭代分组密码。本文针对128 bit AES密码算法结构,完成了AES的FPGA电路设计,对算法一轮的四个操作:S盒(SubBytes)、ShiftRows、MixColumn、AddRoundKey分别进行了实现。

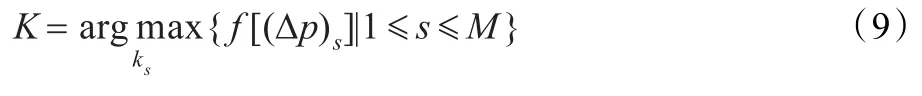

AES密码算法的整体十轮迭代过程电路设计采用流水线结构,并增加串、并转换接口模块作为密码算法模块的输入输出端。FPGA内部设计顶层结构如图4所示,Receive模块负责接收计算机串口发送到开发板上的数据即明文,并对数据进行重新组装;Aes_enc是实现AES算法的主体模块,完成AES的加密计算;Send模块负责将加密好的密文“拆装”成可以用串口发回计算机的串行数据,并将数据输出至计算机。

图4 FPGA顶层设计图

在设计中,加入了FPGA的DCM时钟模块,将AES加密/解密运算时间降至了5 MHz时钟,降低了FPGA的运算速度,以利于示波器对数据的采集,整个设计占用了1 239个Slices,815个寄存器,与此相关设计可参考文献[8]。

实验平台由FPGA密码系统(采用Xilinx公司的SPANTAN3系列的90 nm技术的SRAM型FPGA:XC3S400芯片作为分析对象)、示波器(Tektronix DPO4032)、稳压电源、电磁信号采集探头(RF-B3-2磁场探头)、放大器(PA303,放大倍数30 dB)及PC机(Pentium IV4 2.8 GHz,160 GB HDD,1 GB DDR RAM,USB及RS232接口)组成。电磁探头将接收到的FPGA电磁信号传送给示波器进行采集,并通过USB传输到PC机存储,示波器的采集过程由PC机上用LabView编写的虚拟仪器控制平台实现自动控制,整个控制流程为:

(1)虚拟仪器控制平台首先初始化示波器,设置采集参数,并通过RS232接口给FPGA提供随机明文输入。

(2)当FPGA接收到明文后,密码电路工作,进行加密计算,并将密文数据回送给PC机,同时触发示波器记录探头的电磁信号输出,虚拟仪器控制平台控制示波器实时向PC机传输信号数据,PC机存储数据。然后重复上述过程,实现数据采集的完全自动化。

(3)在采集数据完成以后,在PC机上用C++或MATLAB编写的信号处理与分析软件进行数据分析从而获取密钥。

5 近场电磁探头的定位

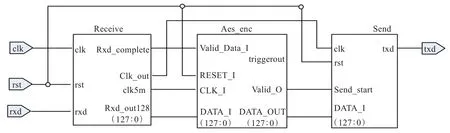

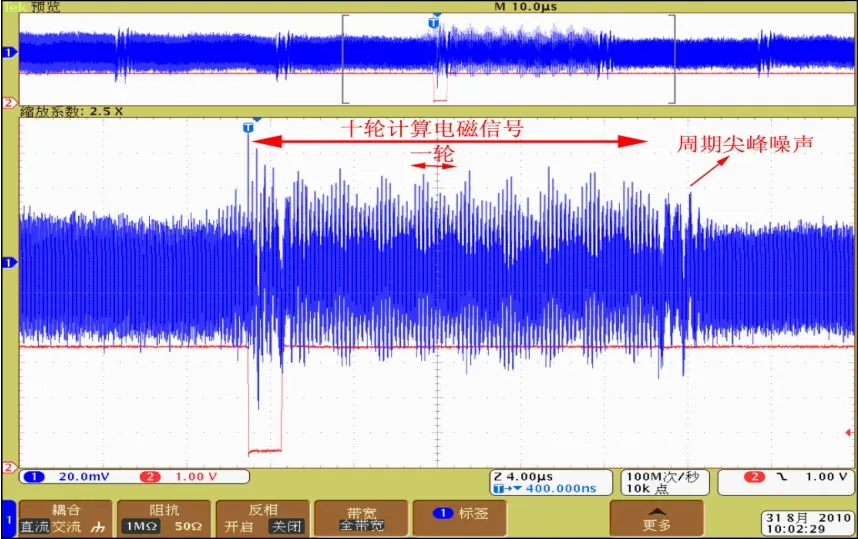

将AES密码电路装载进FPGA,AES密码电路进行加密计算,利用近场电磁探头,通过放大器接入示波器,在示波器上观测到AES密码电路运算的电磁信号如图5所示。

图5 未进行扫描定位的AES十轮计算电磁信号

通过对密码电路运算进行的简单电磁分析,从图5中明显可以看到,电磁信号显示了AES的十轮计算过程,十轮AES加密形成了重复的模式。十轮计算电磁信号的能量幅度大约是40 mV。除此之外,也可以看到除十轮计算的电磁信号以外,还出现了周期性的噪声信号,并且其能量幅度最高达到100 mV。对周期噪声信号进行分析,认为该周期噪声是由于FPGA内部本身的主动配置电路所产生的。由于其幅度明显大于AES十轮计算所产生的电磁信号幅度,并且通过对AES多次加密计算的电磁信号进行观测,可以发现该噪声信号随机出现在AES十轮加密计算过程中,如果运用统计分析大样本量平均的方法去消除该噪声信号,则需要的样本量将非常大,并且效果并不理想,严重影响电磁信号分析的信噪比。

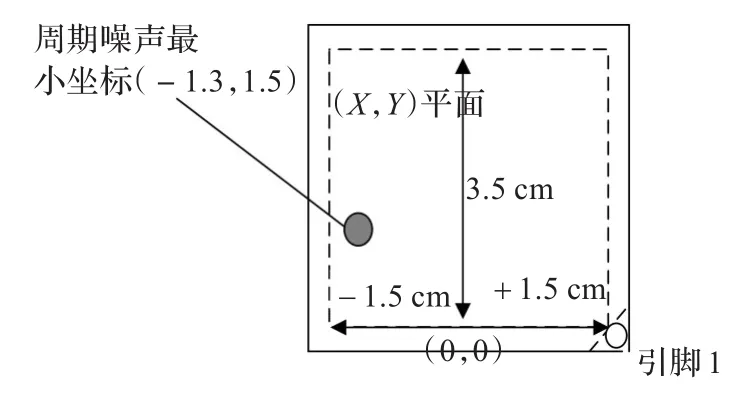

对此,采用逐点电磁扫描方法对FPGA表面电磁采集点进行定位,确定最佳电磁辐射采样点的位置,即与运算数据密切相关的电磁辐射信息泄漏点,同时泄漏点必须满足既使周期噪声信号最小,又使十轮计算的电磁信号较明显这两个要求。电磁扫描仪的步进距离为1 mm,对FPGA表面每一位置点的电磁信号进行扫描,观测示波器上的电磁信号曲线,定位最佳测量点。图6为FPGA平面扫描示意图,显示了定位点的精确坐标位置。

图6 FPGA平面扫描示意图

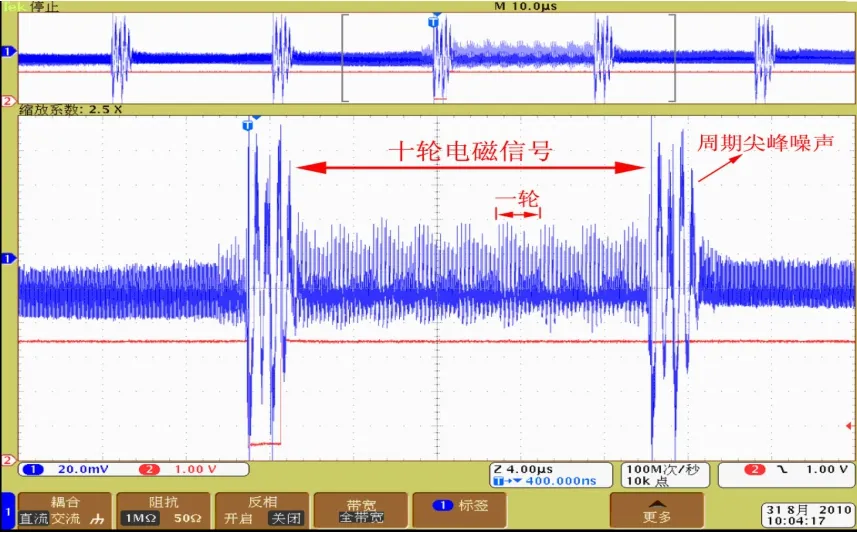

在进行扫描定位后,用探头采集AES十轮计算电磁信号。如图7所示,可以看出FPGA本身的周期噪声电磁信号幅度要低于十轮加密计算所产生的电磁信号幅度,不影响实际的电磁分析攻击。

图7 进行扫描定位采集的AES十轮计算电磁信号

6 实验结果及结论

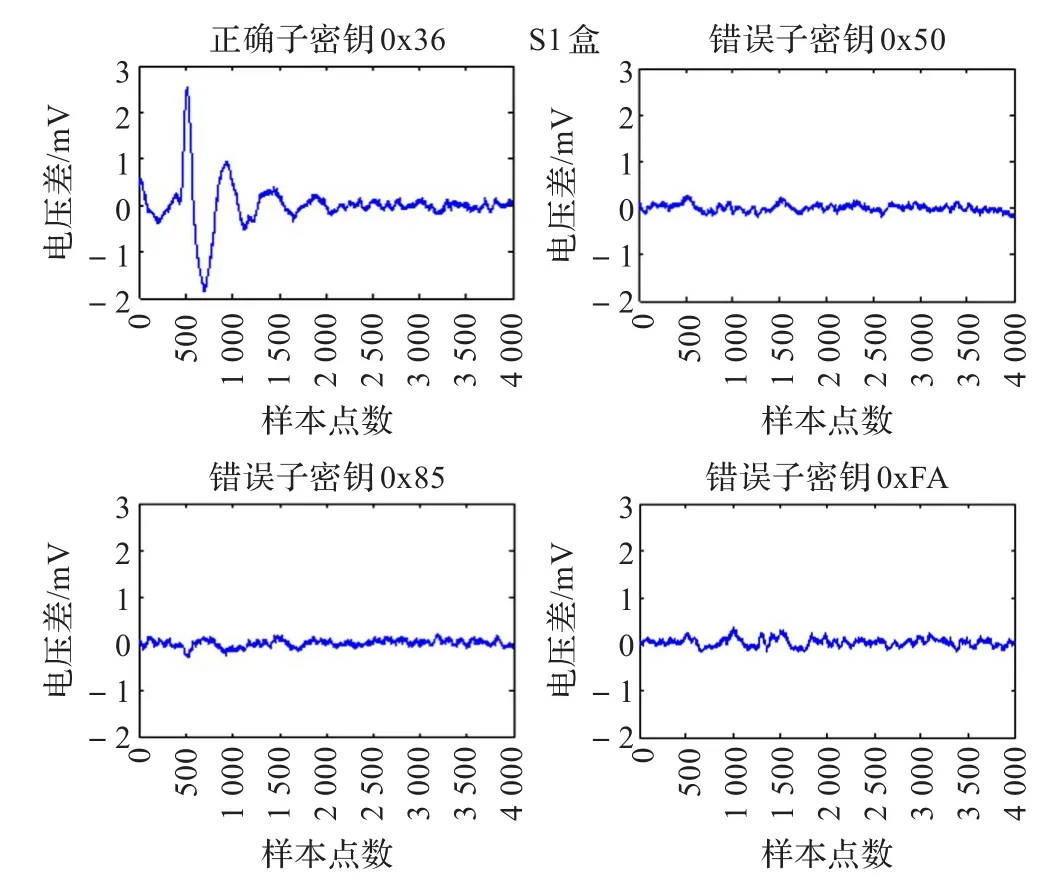

利用电磁探头对FPGA中AES密码电路加密过程中的电磁信号进行采集完成以后,在42 000个样本的条件下,对所采集的电磁信号进行差分电磁分析。如图8所示为对AES中S1盒进行差分电磁攻击后的情况图,分别列出了正确猜测子密钥(也即是真实子密钥)0x36及错误猜测子密钥0x50,0x85,0xFA所对应的差分电磁曲线,可以观察到在正确猜测子密钥对应的电磁差分曲线上出现了明显的尖峰,而错误猜测子密钥对应的差分曲线则趋于平缓。据此,可成功得出第一个真实子密钥值。

图8 正确猜测子密钥与错误猜测子密钥对应的电磁差分曲线

同理,利用一组电磁辐射曲线可恢复出AES中剩余15个S盒的真实子密钥,最后各子密钥拼接,可得到完整的128 bit密钥。

因此,利用FPGA密码芯片运行时泄漏的电磁辐射,通过旁路攻击手段,能够直接获取其中的秘密信息,采用文中所提出的对密码芯片近场电磁辐射精确定位的方法,能克服攻击中噪声的影响,提高信号信噪比,进而破解密码系统的密钥。

[1]Zhou Yongbin,Feng Dengguo.Side-channel attacks:ten years after its publication and the impacts on cryptographic module security testing[EB/OL].[2011-10-26].http://eprint.iacr.org/ 2005/388.pdf.

[2]Prpic M.Reverse engineering of Java card applets[D].Faculty of Informatics,Masaryk University,Brno,2010.

[3]Agrawal D,Archambeault B,Rao J R,et al.The EM side-channel(s):attacks and assessment methodologies[C]//Proceedings of the 4th International Workshop on Cryptographic Hardware and Embedded Systems(CHES),2003,2523:29-45.

[4]张三慧.电磁学[M].北京:清华大学出版社,1999.

[5]陈志敏.安全芯片旁路功耗分析及抗攻击措施[D].上海:上海交通大学,2007.

[6]Brier E,Clavier C,Olivier F.Correlation power analysis with a leakage model[C]//Cryptographic Hardware Embedded System-CHES 2004.Boston:Springer-Verlag,2004:16-29.

[7]National Institute of Standards and Technology.FIPS-197 Advanced encryption standard[S].Gaithersburg:National Institute of Standards and Technology,2001.

[8]邹程,张鹏,邓高明,等.AES密码电路抗差分功耗分析设计[J].计算机工程与应用,2009,45(36):63-65.

CHEN Kaiyan1,YU Hao1,ZOU Cheng1,WU Hengxu2

1.Department of Computer Engineering,Ordnance Engineering College,Shijiazhuang 050003,China

2.Unit 78086 of PLA,China

To do research for physical information leaked by Electromagnetic(EM)radiations from Field Programmable Gate Arrays(FPGA)cipher chip during its operation,this paper analyzes the principle of direct electromagnetic emanations for Complementary Metal-Oxide-Semiconductor(CMOS)circuit,and then a near- fi eld leakage model about FPGA is designed.According to this model,the technique,EM scanning,is used to tackle the problem of the localization of the spatial position of the cryptoprocessor,in putting an electricmagnetic near- fi eld sensor above the chip.Moreover,Advanced Encryption Standard(AES)circuit is completed based on FPGA cryptosystem and Differential ElectroMagnetic Analysis(DEMA)is introduced.As a result,practical experiment has shown that an attacker can extract the secret 128-bit key using 42000 traces of AES cryptographic device under the condition of having localized the optimal leaking spots characterized by mostly data-dependent EM emissions.

cipher chip;near-field;Electromagnetic(EM)radiations;Differential ElectroMagnetic Analysis(DEMA);Advanced Encryption Standard(AES);Field Programmable Gate Arrays(FPGA)

为探究现场可编程门阵列(FPGA)密码芯片运行时电磁辐射造成的涉密信息泄漏情况,研究了互补金属氧化物半导体(CMOS)电路直接电磁辐射的原理,构建了FPGA密码芯片的近场电磁辐射模型。根据这个模型,探讨了近场电磁辐射测量点的选取,采用电磁扫描的方法解决了电磁探头在FPGA表面电磁信号采集的定位问题。此外,在阐释了差分电磁分析(DEMA)攻击原理的同时,完成了高级加密标准(AES)的FPGA电路设计,针对FPGA密码系统的DEMA攻击实验表明,通过电磁扫描找到最佳测量点,在42 000个样本的条件下能成功破解AES密码电路的128 bit密钥。

密码芯片;近场;电磁辐射;差分电磁分析;高级加密标准;现场可编程门阵列

A

TP309

10.3778/j.issn.1002-8331.1112-0492

CHEN Kaiyan,YU Hao,ZOU Cheng,et al.Differential ElectroMagnetic analysis attacks on FPGA cipher chip in near field.Computer Engineering and Applications,2013,49(18):89-93.

国家自然科学基金(No.60940019);河北省自然科学基金(No.F2012506008);军械工程学院原始创新基金(No.YSCX0903)。

陈开颜(1970—),女,博士,副教授,硕士生导师,主要研究领域为信息安全;余浩(1987—),男,硕士研究生,主要研究领域为信息安全;邹程(1980—),男,博士,主要研究领域为电磁信息检测与主动防护技术;吴恒旭(1983—),男,硕士,主要研究领域为信息安全。E-mail:ouyangyh2010@163.com

2011-12-26

2012-03-29

1002-8331(2013)18-0089-05

CNKI出版日期:2012-05-22 http://www.cnki.net/kcms/detail/11.2127.TP.20120522.1108.006.html