适用于中频采样的CMOS自举采样开关

2013-07-05钱宏文朱燕君季惠才陈珍海

钱宏文,朱燕君,季惠才,陈珍海

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

0 引言

无线通信、高速测量仪器、数字雷达等应用系统对模数转换器(ADC)提出了高速度、高精度、大动态范围、宽输入信号带宽、低功耗等指标要求,使得高性能ADC的设计面临更大的挑战。目前,适用于上述应用场合的ADC实现方式为流水线结构[1,2],并且具有良好的中频采样特性。对于流水线ADC电路的实现,需要用到大量的数据采样开关。作为ADC系统与外界的接口,前端信号采样开关的性能优劣直接决定了ADC所接收到的信号纯度和真实性。对于CMOS工艺,采样开关一般通过MOS管来实现,高线性度的CMOS采样开关可以极大程度上提高流水线ADC的中频采样特性。

在分析现有的CMOS自举采样开关的原理及其存在的不足之后,设计了一种改进的适用于中频采样特性的CMOS自举采样开关。试验结果表明,该自举开关非常适合于中频采样。

1 基本栅压自举采样开关

当MOS开关处于导通时,晶体管工作在线性区,可以将开关MOS管视作一个阻值为Ron的电阻,其大小为[3]

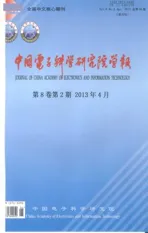

可以看出,Ron是一个与输入信号Vin和衬底偏置电压VSB相关的非线性电阻。MOS管的源极电压为输入电压随着输入变化而变化,栅极电压如果为恒定值(比如电源电压Vdd),则Vgs将会随着输入信号而变化。通过采用栅压自举开关可以很大程度上解决Vgs随着输入信号而变化的问题,如图1所示[4,5]。根据式(1),此时导通电阻为

图1 传统栅压自举开关

可以看出与式(1)相比,Ron变为一个与输入信号Vin无关,而仅与衬底偏置电压VSB相关的非线性电阻,线性度得到了很大的提高。同时可以看出Ron还是一个与衬底偏置电压VSB相关的非线性电阻。若要进一步提高图1所示栅压自举开关的线性度,与衬底偏置电压VSB相关的非线性特性必须被消除;若要进一步减小图1所示栅压自举开关的导通电阻,可以进一步提高开关管Ms栅源电压。

2 改进的栅压自举采样开关

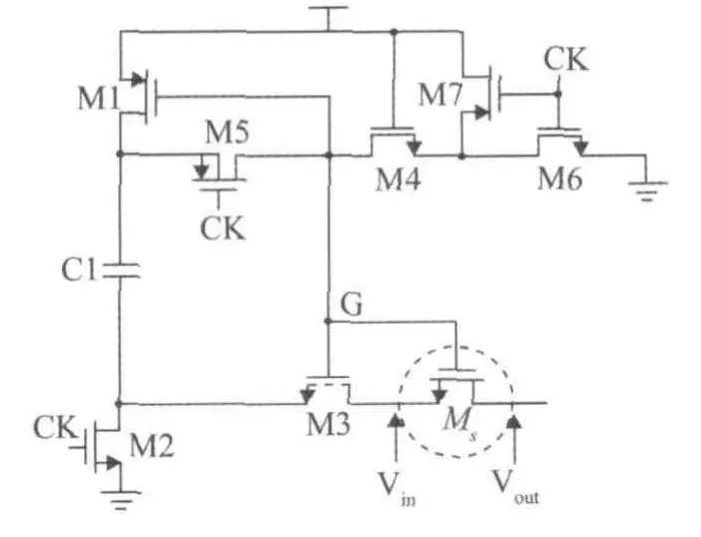

改进的高线性度CMOS自举采样开关电路,如图2所示,其对图1所示基本栅压自举开关的主要改进是:保持图1所示开关的连接方式不变,增加了一个由MOS管M8、M9、M10和电容C2构成的自举支路,进一步提高了开关管的栅源电压,减小了导通电阻;增加了一个由MOS管M11和M12构成的采样MOS开关管衬底电压切换电路,消除了衬底偏置电压VSB相关的非线性特性,提高了线性度。

图2 改进的栅压自举开关

当时钟CK 为高电平时,NMOS 管M2、M4、M6、M8导通,PMOS管M7截止,使得PMOS管M1、M9也导通;电路通过MOS管M1、M2和M8、M9分别对电容C1、C2充电,使得电容C1、C2两端的电压都接近电压Vdd,从而在电容C1、C2上都存储了Vdd*C1(C1=C2)的电量;NMOS管M11截止,M12导通,采样开关MOS管Ms截止,采样开关MOS管Ms衬底接地。

当时钟CK从高变低时MOS管M2、M6、M8截止,MOS管 M7导通,M4导通,电源通过 MOS管M7、M4对结点G的对地寄生电容充电,使得结点G电压升高,MOS管M1、M9截止,M10导通,使得电容C2的上极板接到电容C1的下极板,电容C1、C2串联,M5、M3导通,输入信号通过MOS管M3抬升电容C1下极板电压直到其值等于输入电压Vin,由于电容Cl、C2上存储的电荷在时钟CK变化过程中没有放电回路,存储在其上的电荷保持不变,电容C1上极板的电压就会同步上升,直到其值等于2Vdd+Vin,开关管Ms栅源电压为电源电压2Vdd;MOS管M12截止,M11导通,采样开关MOS管Ms截止,采样开关MOS管Ms衬底接输入节点Vin,这样MOS管Ms的衬偏电压对其阈值电压的影响被消除(VSB=0)。

根据式(2),此时导通电阻为

比较式(3)和式(2),可以看出改进的高线性度CMOS自举开关的导通电阻Ron只与电源电压Vdd、MOS管载流子迁移率un、单位面积栅氧化层电容Cox、MOS管宽长比W/L和MOS管衬偏电压为0时阈值电压Vth0有关。并且在工艺参数及MOS管宽长比W/L相同的情况下,开关Ms的过驱动电压为2倍Vdd,导通电阻Ron小于现有栅压自举开关,因此对于相同的采样电路由更小的时间常数,更快的采样速度,可以采样更高频的信号。因此,所改进的高线性度CMOS自举开关有更好的线性度和更小的导通电阻。

3 试验结果分析

将图2所示本文高线性度CMOS自举开关和图1所示基本自举开关分别作为采样开关应用于相同的采样电路进行仿真,仿真环境相同,输入信号频率2.39 MHz,采样频率 100 MHz,工艺模型为 0.18 μm CMOS工艺,电源电压1.8 V。图2所示开关和图1所示开关对应的MOS管取相同的尺寸,图2所示自举开关中两个电容值均为图1所示基本自举开关的一半。对两种开关采样结果做FFT频谱分析得到输出频谱,如图3所示。可以看出改进的高线性度CMOS自举开关的(无杂散动态范围)SFDR为116.7 dB,比基本自举开关的101.5 dB高了约15 dB;信噪失真比为83.5 dB,比基本自举开关的81.9 dB高了约1.6 dB。说明改进的自举开关比传统的白举开关有更好的线性度。

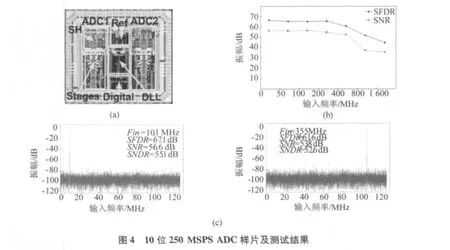

所设计自举采样开关目前已成功应用于一款10位250 MSPS流水线 ADC,该 ADC样片采用0.18 μm 1P6M CMOS工艺流片,样片的照片如图4(a)所示。图中芯片左右两侧两个ADC通道,每个通道内部自上而下为采样保持电路和流水线ADC各级子级电路,芯片中间部分为带隙基准电压及其他基准电压产生及其驱动电路,DLL时钟接收、产生及其驱动电路和数字延时同步和校准逻辑部分。ADC在250 MHz全速采样条件下模拟输入带宽特性如图4(b)所示,可以看出ADC模拟-3 dB带宽达400 MHz以上信号。ADC在250 MHz全速采样条件下对于不同频率输入信号测试得到的FFT频谱图如图4(c)所示,对于10 MHz正弦输入信号转换得到的 SFDR为 67.1 dB,SNDR为 55.1 dB;对于355 MHz正弦输入信号转换得到的SFDR为61.6 dB,SNDR为52.6 dB。从测试结果可以看出,所述自举采样开关中频采样特性良好,符合前文的理论分析。

4 结语

分析了MOS采样开关非线性的来源和现有栅压自举采样开关的不足之处,提出并实现了一种新型MOS采样开关。通过在现有自举开关的基础上增加一个采样MOS开关管衬底电压切换电路,消除了衬底偏置电压VSB相关的非线性特性,提高了线性度,并通过电压倍增减少了开关导通电阻,从而使得所设计MOS采样开关特别适合于中频采样应用。目前该自举采样开关目前已成功应用于一款10位250 MSPS流水线 ADC,测试结果表明开关特性良好。

[1]STEPHEN H LEWIS,PAUL R G.A Pipelined 5-Msample/s 9-bit Analog-to-Digital Convert[J].IEEE J.Solid-State Circuits,1987,22(12):954-961.

[2]CLINE D,PAU1 R G.A Power Optimized 13-b 5 Msamples/s Pipelined Analog-to-Digital Converter in 1.2 μm CMOS[J].IEEE J.Solid-State Circuits,1996,31(3):294-303.

[3]毕查德·拉扎维著.模拟CMOS集成电路设计[M].陈贵灿,程军等,译.西安:西安交通大学出版社,2002.

[4]ANDREW M A,PAU1 R G.A 1.5V 10-bit l4.3 MS/SCMOS Pipeline Analog to Digital Converter[J].IEEE J.Solid-State Circuits,1999,34(5):599-606.

[5]DESSOUKY M,KAISER A.Input Switch Configuration Suitable for Rail-to-Rail Operation of Switched Opamp Circuits[J].Electronics Letter,1999,35(1):8-10.