基于模块局部可重构FIR滤波器设计

2013-01-31黄凤英

黄凤英,王 俊,钱 慧

(1.福州大学 物理与信息工程学院,福建 福州350002;2.福州大学 电气工程与自动化学院,福建 福州350002;3.福建省集成电路设计中心,福建 福州350002)

FIR数字滤波器具有在设计任意幅频特性,同时能够保证严格的线性相位特性,具有稳定性强、精度高、速度快等特点[1],在雷达、通信、音视频、图像、航空航天等领域有着广泛应用。传统的FIR滤波器的特性一般不能在线改变。但对未知时变环境下的信号进行处理时,滤波器的性能必须随着实际条件变化而变化[2]。因此,设计一种能在保证系统正常运行的前提下,实时更改滤波器系数的FIR滤波器在研究、工业生产领域得到了广泛的关注。

FPGA是一种典型的动态可重构器件,具有“在系统”重新配置电路功能的独特性能,同时还具有在系统动态重构电路逻辑的能力,对提高电子信息系统的实时处理能力、可靠性、降低硬件系统的规模和功耗具有重大的理论和实际意义[3]。

本文利用Xilinx Virtex-4 FPGA可以重构配置特性,结合滤波器结构的特点,设计了一个基于模块局部可重构的FIR滤波器,并结合MATLAB工具软件,对可重构设计的性能进行了测试。实验结果表明,相对于传统设计方法,本文设计的可重构FIR滤波器具有快速、灵活、硬件资源消耗少等优势。

1 FIR滤波器原理概述及设计方法

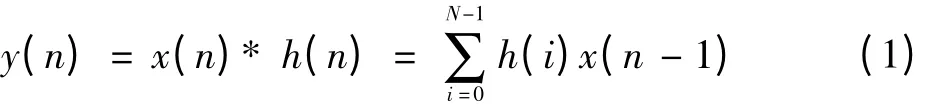

FIR滤波器的数学表达式为

式(1)中,N是FIR滤波器的抽头数,x(n)表示第n时刻的输入样本,h(i)表示滤波器的第i级抽头系数。FIR的传递函数H(Z)是通过对h(i)进行Z变换得到,其形式如式(2)所示

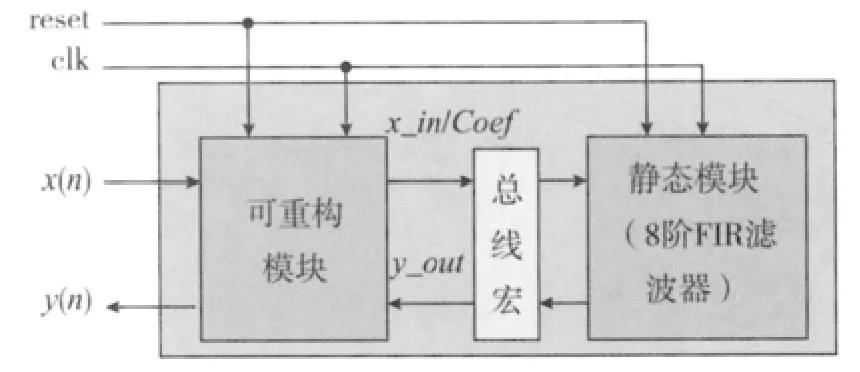

根据式(1)、(2),可画出FIR滤波器的一般结构如图1所示。

图1 FIR滤波器的一般网络结构

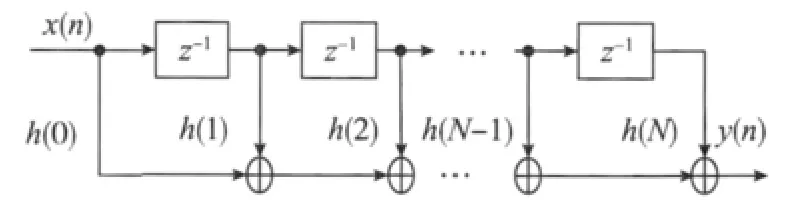

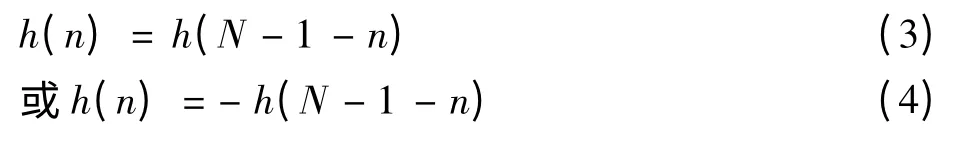

由图1可知,FIR滤波输出结果y(n)实质上是由一个输入信号x(n)经过逐级延迟,且在各级延迟输出进行加权累加得到。滤波器最主要的工作过程是进行乘累加运算,一个N阶的FIR滤波器完成一次滤波需要进行(N-1)次加法运算和N次乘法运算。但FIR数字滤波器具有线性相位特性及对称特性,即

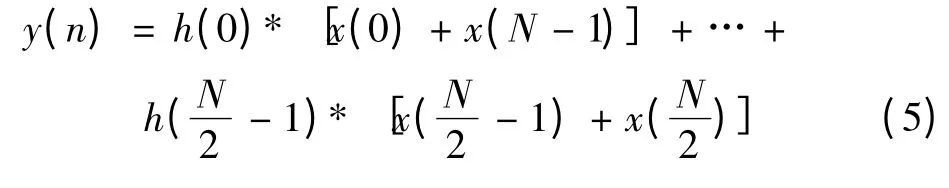

从而容易得到偶对称的FIR滤波器的输入输出关系,如式(5)所示

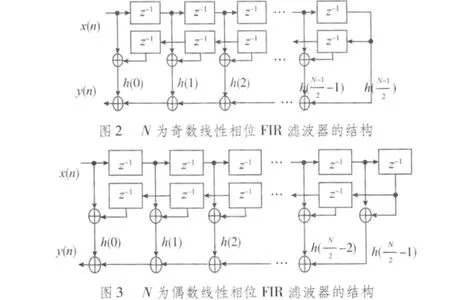

相对于直接型结构,在实现滤波器硬件电路上,乘累加次数得到减半,资源消耗更少,且滤波的时钟周期减半,从而大大提高了处理速度[4]。图2和图3分别显示了N取奇数和N取偶数的线性相位FIR滤波器结构。

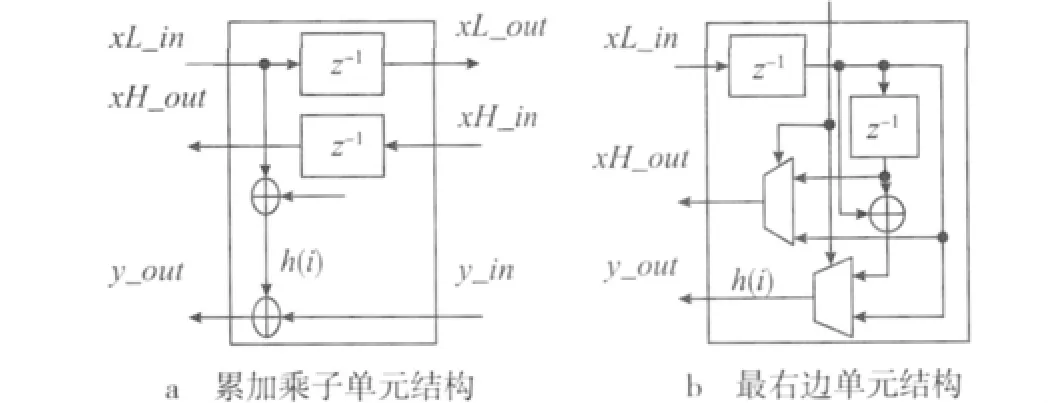

从图2、图3可知,FIR数字滤波器可以看成由多个累加乘子单元和一个最右面的单元结构组成,如图4a,4b所示,根据阶数为偶数或者奇数(信号线even为1或者0)决定最右单元结构。从结构上看,FIR滤波器容易通过多个滤波器直接级连就能够扩展滤波器的阶数,因此在FPGA上采用基于模块局部重构技术来重构FIR滤波器变得简单、灵活,且能够充分利用资源。

图4 单元结构图

2 基于模块局部重构设计

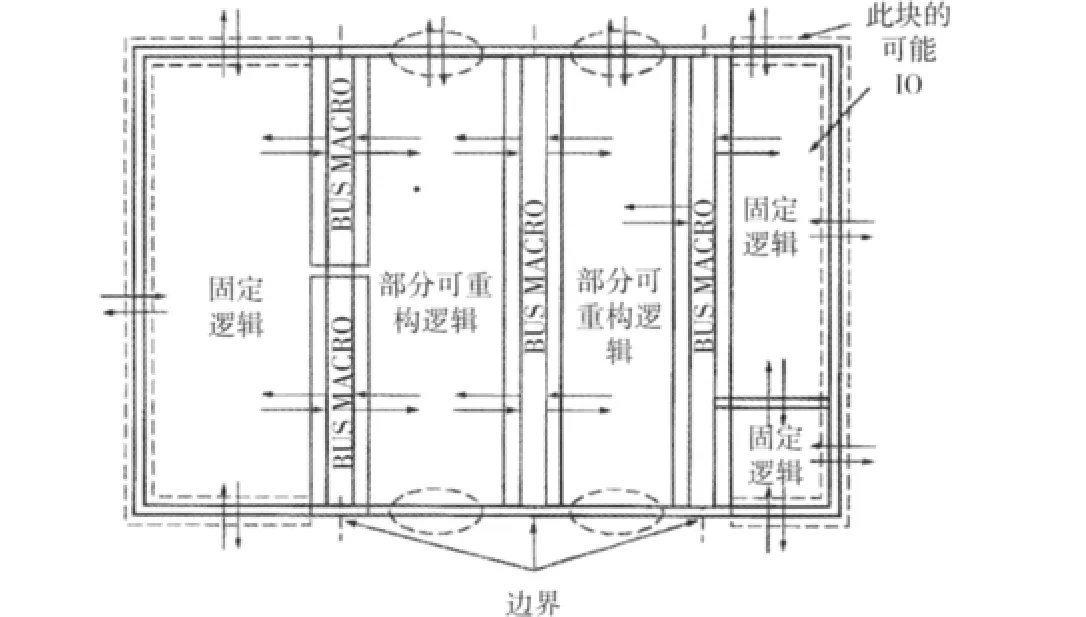

如图5所示,基于模块的可重构设计的一个重要步骤是将整个电路功能划分成功能可变的重构模块(可重构逻辑)和功能不变的静态模块(固定逻辑)。其中,可重构区域可以在器件的其他部分还在运行的情况下进行重构。

图5 两个模块的设计布局图

基于模块局部重构的输入、输出以及穿过可重构模块边界的布线资源是预先固定的,这就需要一种特殊的总线宏(BUS MACRO)在局部重构模块和静态模块之间充当一个固定的布线桥,总线宏在功能重构的时候仍保持不变,从而能够保证两个模块之间能正确的通信[5]。

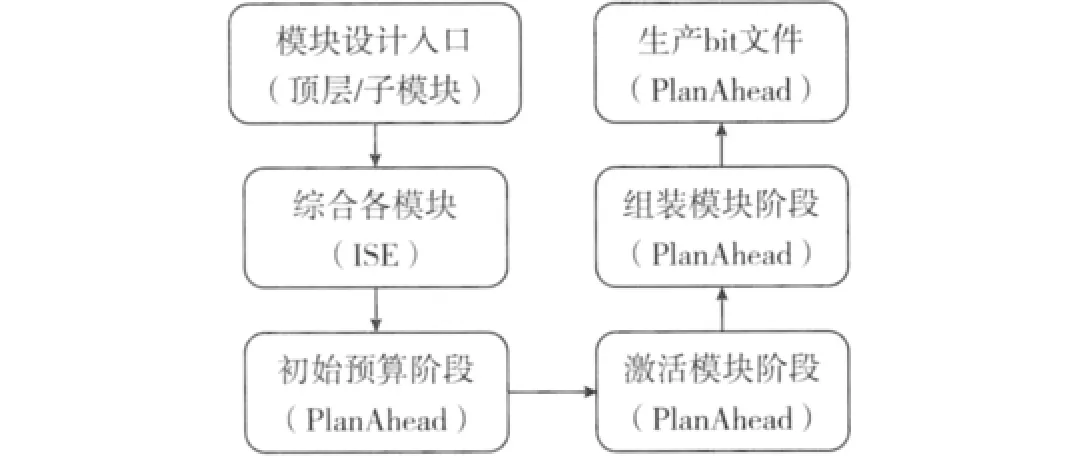

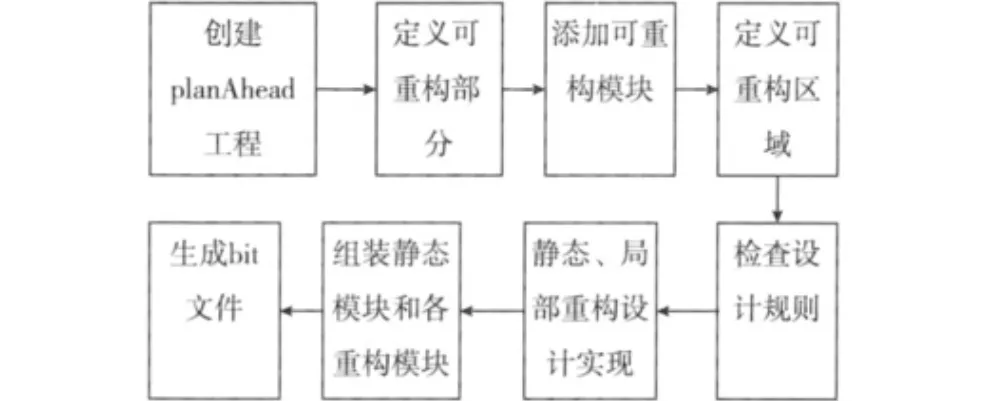

实际设计中,如图6所示,每个模块从硬件描述语言(verilog)设计开始,经过独立综合、布局、实现等操作,并生成比特流文件[6]。

图6 局部重构设计流程图

3 可重构FIR滤波器设计

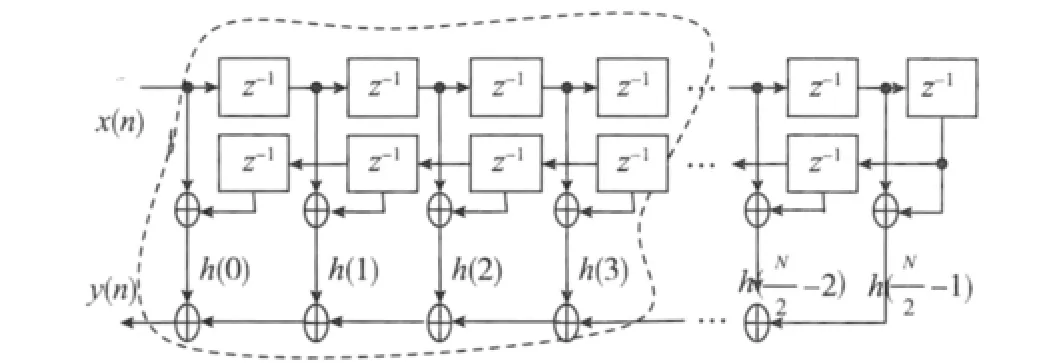

本文设计的可重构FIR滤波器阶数可从8阶到16阶进行的转变,其中静态模块由3个累加乘子单元结构和最右边单元结构组成;可重构模块由多个累加乘子单元结构模块和滤波器系数输入的控制模块组成。且在静态模块和动态可重构模块之间插入总线宏,设计框图如图7所示。

图7 可重构FIR滤波器的设计框架

从前面滤波器的结构图中可以看出16阶的FIR滤波器和8阶的滤波器硬件结构基本相同,为了构成16阶滤波器,可在原有的8阶滤波器结构上加载4个累加乘单元模块,如图8中的虚线区域所示。在实现重构过程中,只需下载重构模块的配置信息,而不需要重新配置整个芯片,就能将原有的滤波器构成16阶的FIR滤波器,而原本在FPGA上的8阶FIR滤波器不受任何影响,如此可大大减少芯片的重配置时间。

图8 虚线区为局部重构部分可动插入或删除

4 实现

该部分描述了一个重构的FIR滤波器在Xilinx Virtex-4 FPGA上的实现过程。

4.1 硬件描述语言编码及综合

局部重构是一种分层设计方法,在编码过程中必须严格遵守。首先,用ISE软件设计3种HDL文件,分别是顶层HDL设计,静态模块HDL设计和局部重构模块HDL设计,然后独立综合各文件。

顶层模块不包含任何逻辑,只有输入输出实例、静态和可重构模块实例、信号声明,以及定义了各个子模块的连线,区域及总线宏的分配。静态模块和可重构模块主要完成移位相加、乘法、输出相加功能,但静态模块在重构过程中保持固定不变,局部重构模块在重构前后功能改变。当多个重构模块使用同一个可重构区域的时候,每个模块的文件名和端口配置必需和顶层实例化的可重构模块一样[7]。

4.2 实现局部可重构

完成前面的编码和综合工作后,将进入实现局部重构的过程,如图9所示。此过程在Xilinx的局部重构平台PlanAhead集成环境下实现。

图9 局部重构的流程

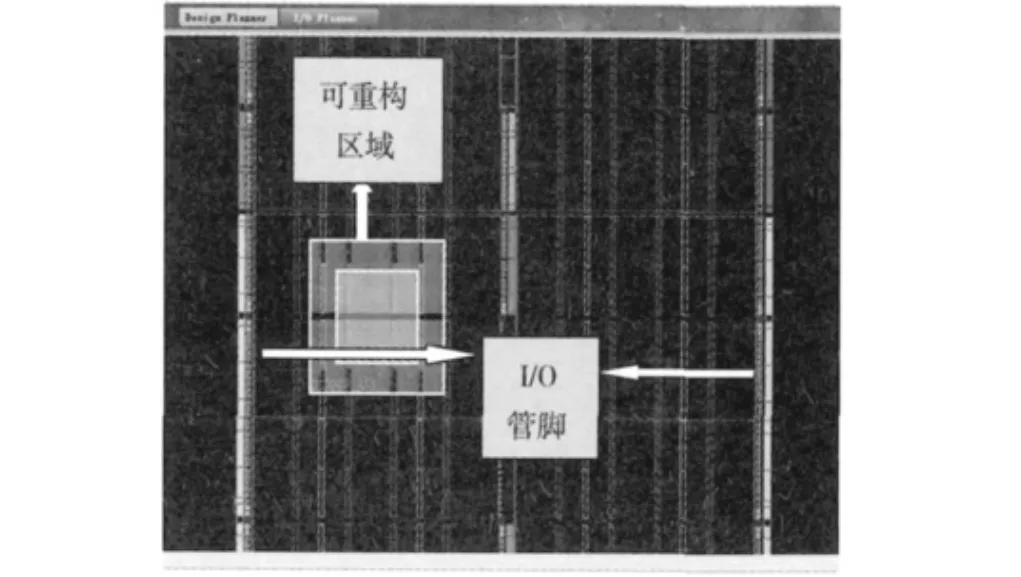

图10 显示了在FPGA上可重构区域和I/O管脚的布局以及总线宏的位置。实现的最后一步是组装,组装静态模块和局部可重构模块,并创建配置FPGA的位流文件。在此过程中,将创建好两种位流文件:整体位流文件(full bit file),根据需要,在每个可重构区域中选择一个可重构模块作为缺省模块被并入整体位流文件,用于FPGA初始化时装载配置;局部位流文件(partial bit file),由重构模块生成,该文件在整体位流文件配置FPGA后再下载到FPGA中,此时静态模块仍处于运行状态,最后实现FIR滤波器阶数的转变。

图10 可重构区域和I/O管脚的布局

5 验证和结果

本实验选择一个只含8阶FIR滤波器系数的可重构模块和一个静态模块(8阶FIR滤波器功能)合并为整体位流文件,该文件大小为1 673 kbyte,通过下载线下载到Virtex-4 XC4VSX35 FPGA设备上。之后下载构成16阶滤波器的可重构位流文件,大小为74 kbyte,该部分只重构可重构区域的电路,静态部分将不受任何影响。验证时,把两频率的正弦波信号叠加后,经过ADC,再通过FPGA上的滤波器模块,最后通过USB传输到计算机,并用MATLAB显示出滤波前后的时域及频域图形,如图11所示。叠加信号经过可重构FIR滤波器后,将高频信号滤除了,从而验证了可重构设计的正确性。

由于位流大小直接与占用硬件资源大小及配置时间成比例,只加载重构模块74 kbyte的配置信息就能实现更高阶FIR功能,而代替了整个FPGA重构(整体文件为1 673 kbyte),这样一来大大缩短配置重构时间。表1显示了整体和重构位流文件的配置速度。

表1 两种位流文件的配置速度

本文还与直线型结构的可重构FIR滤波器的进行对比,同一性能的FIR滤波器,映射后的Slice、LUT及DSP48使用个数对比,如表2所示,从表中可以计算出对称转置结构的可重构滤波器可以节省大约12%的Slice资源、45%的LUT资源及50%的DSP48资源。

6 总结

本文描述一个在Xilinx Virtex-4 XC4VSX35 FPGA设备上采用动态局部可重构的方法来设计阶数可变的FIR数字滤波器,与同类的滤波器相比,资源配置更少,Slice、LUT和DSP48s资源分别节省大约12%、45%和50%,重构时间提高了80%,并能实现重构区域资源的时分复用,同时提高了该区域资源的利用率及灵活性。动态局部可重构技术能够动态插入或删除局部可重构模块,使得FIR滤波器系数得到实时更新,阶数能够更灵活地改变。

[1]王静,鱼云岐.基于FPGA的FIR数字滤波器设计与仿真[J].国外电子元器件,2008(11):90-92.

[2]梁甲华,林争辉,林涛.基于可重构FPGA技术的自适应FIR滤波器的实现[J].电子工程师,2004,30(12):48-50.

[3]谷銮,徐贵力,王友仁.FPGA动态可重构理论及其研究进展[J]计算机测量与控制,2007,15(11):1415-1418.

[4]刘庆良,卢荣军,李建清.FIR数字滤波器的FPGA实现研究[J].电子设计工程,2010(3):59-61.

[5]KARTHIK S,SHILPA J.Implementation of partial reconfigurable FIR filters using dynamic partial rconfiguration[J].Computer Science,2011(1):65-69.

[6]CARDOSO J M P,HUBNER M.Reconfigurable computing[M].New York:Springer-Verlag,2011.

[7]YEONG J,HANHOLEE O,LEE C H.Dynamic partial rconfiguration FIR filter design[J].Computer Science,2006(5):30-35.