基于FPGA的DDS波形发生器设计

2012-12-21蒋志勇

蒋志勇

(1.桂林电子科技大学 广西 桂林 541004;2.桂林航天工业高等专科学校 广西 桂林 541004)

基于FPGA的DDS波形发生器设计

蒋志勇12

(1.桂林电子科技大学 广西 桂林 541004;2.桂林航天工业高等专科学校 广西 桂林 541004)

信号发生器作为电子技术领域中最基本的电子仪器,广泛应用于各个领域中。随着电子信息技术的发展,对其性能的要求也越来越高,如要求频率稳定性高、转换速度快,具有调幅、调频、调相等功能,另外还经常需要两路正弦信号不仅具有相同的频率,同时要有确定的相位差。因此基于FPGA的DDS波形发生器,具有一定的实际意义。以FPGA芯片EP2C8Q208C8为核心,辅以必要的模拟电路,在Verilog编写的程序控制下,构成了一个基于直接数字频率合成技术的波形发生器。

FPGA;DDS;波形发生器

0 引言

随着半导体技术的发展,FPGA的集成度越来越高,资源越来越多,单位成本变得相对便宜。相对专用集成电路(ASIC),FPGA有更短的开发周期,如果产品数量不大,FPGA更有低成本的优势。FPGA擅长逻辑和高速可并行运算,不是通用DSP芯片可比拟的,一般单片机更是望尘莫及。

直接数字频率合成(简称 DDS)技术是一种新的全数字的频率合成技术,从相位的角度出发直接合成所需波形。这种技术由美国学者J.Tiercy,M.Rader和B.Gold于1971年首次提出,但限于当时的技术和工艺水平,DDS技术仅仅在理论上进行了一些探讨,而没有应用到实际中去。近30年来,随着VLSI、FPGA、CPLD等技术的出现以及对DDS理论上的进一步探讨,使得DDS技术得到了飞速的发展。DDS以有别于其它频率合成方法的优越性能和特点成为现代频率合成技术中的姣姣者。

DDS的主要优点有:(1)频率转换快,一般在纳秒级(2)分辨率高(3)频率合成范围宽(4)相位噪声低,信号纯度高(5)可控制相位,在频率变换时也能保持相位联系(6)生成的正弦/余弦信号正交特性好等。与此同时,用FPGA设计DDS电路比采用专用DDS芯片更为灵活。因为只要改变ROM中的数据,就可以产生任意波形,因而具有相当大的灵活性。FPGA芯片还支持在线升级,将DDS设计嵌入到FPGA芯片所构成的系统中,并采用流水线技术,其系统成本并不会增加多少,而购买专用芯片的价格则是前者的很多倍。因此,采用FPGA来设计DDS系统具有很高的性能价格比。

DDS问世之初,构成DDS元器件的速度的限制和数字化引起的噪声这两个主要缺点阻碍了DDS的发展与实际应用。近年超高速数字电路的发展以及对DDS的深入研究,DDS的最高工作频率以及噪声性能已接近并达到锁相频率合成器相当的水平。随着这种频率合成技术的发展,现已广泛应用于通讯、导航、雷达、遥控遥测、电子对抗以及现代化的仪器仪表工业等领域。

设 计 所 用 到 的 是 ATERAL公 司 的 CycloneII系 列 的EP2C8Q208C8N,拥有两个锁相环,8000多的LE单元,4KB的RAM和64KB的ROM等,最高运行频率可达到250MHz。

1 电路的构成

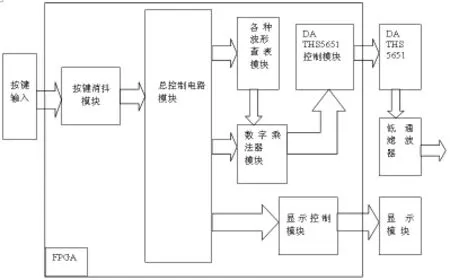

图1 系统框图

设计主要是基于FPGA的DDS波形发生器的实现,要求输出频率范围在1Hz~5 MHz,采用EP2C8硬件为核心平台,再加上FPGA的外围电路,利用至顶向下的方法,将数字频率合成器(DDS)、存储器和 I/O接口等硬件设备集中在一片FPGA上,有利于直接数字频率合成技术产生所需波形,通过状态机控制解决不同频率和幅值的实现,其中片内正弦表 ROM传出的数据经数字乘法器再经THS5651完成数模转换,通过控制乘法器的乘法系数实现信号幅值的控制,之后再将输出接入示波器的输入端,即可观察所设计的波形。开发板提供的主时钟频率f=50 MHz,由于各个模块需要不同时钟信号,按键及控制电路所需时钟要求并不高,10kHz就行,而累加器、查询表ROM模块和DA驱动需要高达100MHz的时钟,所以在此调用quartusII软件自带的PLL单元生成100MHz和20MHz两种频率,再用一个分配器将20MHz的时钟分频到10kHz,这样系统各模块要求的时钟频率都已生成。系统框图如图1所示。

1.1 FPGA核心部分的设计

1.1.1 按键输入信号处理模块的设计

按键输入信号处理由按键消抖和单脉冲发生器两部分组成。用Verilog语言编程的有限状态机的设计方法来实现按键的消抖,经仿真分析和下载实现,这种方法设计的消抖电路能够很好地实现电路功能,进行快速按键时都能保证每按一次作一次的响应,且性能稳定。

键控单脉冲发生器是利用上述电路得到稳定的信号,再用两个D触发器和一个与门产生单脉冲。

1.1.2 系统控制模块的设计

系统控制模块主要由波形选择单元、频率控制单元和幅值控制单元和相位累加器组成。其中波形选择、频率控制和幅值控制的时钟频率为10K,相位累加器频率为100MHz。

频率控制单元主要是实现控制频率控制字,由公式fout=M×fC2N可知,当系统时钟和相位累加器位数N一定,只要改变频率控制字M就可改变输出频率。因为设计要求频率精度为1Hz,根据要求及现有条件,确定系统时钟频率为100MHz,相位累加器位数N为32位,由公式Δfmin=fC2N可得频率分辨率为0.023283064,所以频率控制字的大小需为43的倍数就可实现1Hz的精度要求。由于输出频率范围较大,且按键有限,故设置步进单位为1Hz、100Hz、10kMz、1MHz四个档位,由一个按键通过状态机实现步进单位选择,再由两个按键分别实现频率增减控制。

幅值控制单元是通过改变幅值控制字实现输出波形幅度的控制,因为幅值(峰峰值)范围是0~5V,所以设计两个步进单位0.1V和1V,通过一个按键实现步进选择,再用两个按键分别实现增减控制。相位累加器相位累加器是实现DDS的核心之一,它由一个N位字长的二进制加法器和一个固定时钟脉冲取样的N位相位寄存器组成。相位寄存器的输出与加法器的一个输入端在内部相连,加法器的另一个输入端是外部输入的频率控制字X。这样,在每个时钟到达时,相位寄存器采样上个时钟周期内相位寄存器的值与频率控制字X之和,并作为相位累加器在这一时钟周期的输出。频率控制字X决定了相应的相位增量,相位累加器则不断地对该相位增量进行线性累加,当相位累加器积满两时就会产生一次溢出,从而完成一个周期性的动作,这个动作周期即是DDS合成信号的一个频率周期。于是,输出信号波形的频率表示式为f0=(fC× )K 2N,由该式可知,输出信号频率主要取决于频率控制字X,当X增大时,f0可以不断的增高,由抽样定理,最高输出频率不得大于fC2,而根据实验所得,实际工作频率小于fC3时较为合适。

本设计中只须将频率控制字送入相位累加器中然后取其高12位输出做为查找表的地址,这样在符合频率精度的前提下能够节省ROM的资源。

1.1.3 显示模块

显示模块包括频率显示模块和电压显示模块,分别各用一块四位七段数码管实现。

1.1.4 ROM查找表设计

FPGA的结构是由基于半定制门陈列的设计思想而得到的。所用的EP2C8Q208C8是查找表型FPGA,利用QuartusII综合可以自动编译LPMROM元件的文件,在EP2C8Q208C8的EAB上产生ROM功能。利用QuartusII自带的LPM ROM核预置已生成的波形.mif文件。因为DAC是10位的,又考虑到数字信号存在的杂散波干扰,根据实验可知,在一定范围内ROM单元每增加一位地址就可减少6dB的杂散干扰,综合考虑,取ROM地址线为12位,输出数据为10位。其中LPM_FILE的“.mif”中存放波形的值,为了保证波形的平滑,设计时将一个周期分为1024个点。本设计中的波形文件.mif是用波形生成软件得到。

1.1.5 数字乘法器模块

数字乘法器主要功能是实现波形幅值的控制。由于经查找表输出的波形幅值已是最大,所以该数字乘法器实际是一个小数点乘法器或者叫做分数乘法器,因为现有的乘法器IP核都是基于整数相乘的,由总控制模块输出的幅值控制字也是无符号整型的,所以将幅值控制字与波形量化的幅值数相乘,再左移,左移位数直接影响幅值的精度和误差,综合考虑,取左移位数为6,能很好实现要求。

1.1.6 DAC芯片THS5651驱动模块

THS5651是一个10位分辨率的数字模拟转换器(DAC),特别适合用于数字数据传输的有线和无线通信系统。THS5651是高速低功耗COMS数字模拟转换器,它在提供优良的AC和DC性能同时,支持更新率可达100MSPS。

THS5651在时钟CLK的上升沿锁存数字信号,在下一个时钟将转换好的模拟信号输出。所以只要保证在转换CLK的上沿时ROM输出数据稳定即可正确转换。将芯片工作时钟设为100MHz可以对速率为100M/S的数据流进行转换。

1.2 外围接口硬件电路

硬件电路包括FPGA核心板和与之配合的外围接口电路,外围接口电路又包含按键LED指示电路、显示电路和DA转换电路。

DA转换电路由电源部分、DA芯片 THS5651和高速运放THS4001组成。高速运放THS4001主要是实现低通滤波功能,因为经THS5651输出的电流外接50欧电阻转化为电压后的波形并不平滑,还需低通滤波器(6 MHz以下)对转换的波形进行滤波才能得到干净的波形。又由于THS4001需要双电源供电,同时为了避免FPGA电路部分对DA和运放的干扰,为此将DA转换板的电源独立。

2 调试

调试过程主要围绕FPGA+DAC为核心的DDS信号输出、频率显示进行及按键控制进行。利用QuartusII提供的嵌入式内置逻辑分析仪,通过JTAG口实时观察FPGA内部信号,以便及时发现、定位和修复FPGA当中的存在的逻辑错误。频率显示和按键控制调试主要是通过建立波形仿真文件单独对按键模块或频率显示模块进行仿真,以便发现其逻辑错误并改正。最后接上外围接口硬件,实时按键控制观察波形和显示,并调整DAC的输出电流和运放外接阻值参数,直至调出理想波形为止。

3 测试结果

周期性波形包括频率和幅值可调的正弦波、方波和三角波。用示波器来测试波形的频率和幅值(峰峰值),测试结果表明频率误差均在0.2%以下,幅度误差均在2%以下。达到设计要求。

4 结束语

设计以FPGA为核心,利用DDS技术和独特的控制算法实现了信号生成和控制显示等功能,在系统设计过程中,力求硬件线路简单,充分发挥FPGA设计灵活的特点,来满足系统设计要求。

[1]黄智伟,王彦,陈琼,等.FPGA系统设计与实践[M].北京:电子工业出版社,2005.

[2]刘波.精通Verilog HDL语音编程[M].北京:电子工业出版社,2007.

[3]夏宇文.Verilog数字系统设计教程[M].2版.北京:北京航空航天大学出版社, 2008.

[4]清华远见嵌入式培训中心.FPGA应用开发入门与典型实例[M].北京:人民邮电出版社,2008.

[5]王卫东.模拟电子电路基础[M].西安:西安电子科技大学出版社,2003.

蒋志勇(1966—),男,广西桂林人,桂林电子科技大学信息与通信学院2006级工程硕士研究生,桂林航天高等专科学校电子工程系教师,副教授。

江广霞]