一种低噪声高PSRR的LDO线性稳压器

2012-11-22邹静杨维明蒋师刘雪

邹静,杨维明,蒋师,刘雪

(湖北大学物理学与电子技术学院,湖北 武汉 430062)

对采用电池供电的便携式设备而言,高性能、高效率的电源管理芯片必不可少.在电源管理芯片中,低压差线性稳压器( low dropout voltage regulator,LDO)通常位于DC-DC变换器之后,为模拟电路等对电源噪声和稳定度要求较高的电路提供电源电压[1].因此,电源电压抑制比(power supply rejection ratio,PSRR)和噪声是LDO的两个重要指标.近年来学术界和工业界提出了许多提高LDO PSRR的技术.比如,在LDO的输入端增加RC滤波电路、两个LDO级联[2]、利用NMOS和PMOS级联构成功率管[3]等.这些方法简单实用,但会增加LDO的最小压降,降低LDO的效率.为提高效率,文献[4]用电荷泵驱动NMOS功率管,但引入电荷泵会增加设计复杂度,增加输出噪声.本文中针对这种需求设计了低噪声、高PSRR的LDO线性稳压器,并设计出合适的频率补偿方案,保证整体电路的稳定性[1].

1 LDO的系统架构及电路设计

图1 PMOS功率管型LDO线性稳压器

1.1LDO系统的噪声分析基本的LDO线性稳压器包括误差放大器(error amp)、调整功率元件(pass element)、基准(voltage reference)与偏置电路以及反馈电阻网络[2].图1为PMOS功率管型LDO线性稳压器的基本结构图.

(1)

通常情况下,R1与R2的比值固定,所以优化噪声的有效方法是设计低噪声的带隙基准源.

图2 PMOS型LDO的PSRR交流小信号模型

1.2LDO系统的PSRR分析基准电压源产生的基准电压Vref以及电阻反馈网络产生的反馈系数直接影响该LDO线性稳压器的输出.只要保证反馈电阻的高度匹配和基准电压的稳定,就可以实现恒定的LDO输出电压.LDO线性稳压器的电源抑制比特性反映了输出电压对输入电源电压的小范围波动的抑制能力.图2是对PMOS作为功率管的LDO的PSRR小信号交流等效模型.

LDO的电源抑制比的数学表达式近似为:

(2)

(3)

(4~5)

(6)

(7)

式中:G1=(Roa)-1、G2=(Rout)-1,AVOTA(0)、BWOTA、GBW分别为误差运算放大器的直流增益、带宽以及LDO的增益带宽积.通过PSRR的零极点分析,可以得出以下结论:

(1)误差运算放大器的直流增益AVOTA(0)与低频段的PSRR成正比,但是高增益的放大器将会使单位增益频率变大,过多的极点包括在单位增益带宽之内可能导致相位裕度偏低,影响系统的稳定性.所以稳定性和PSRR之间要做一个折衷考虑;

(2)PSRR的第一个零点Z1和放大器的带宽成正比;第一个极点P1与环路的增益带宽积成正比,它们应尽可能靠近,以补偿相位的变化,但它们同样影响环路的稳定性,必须折衷考虑;

(3)PSRR的第二个极点P2与输出电容Cout成反比,虽然增大输出电容可以将第二个极点向低频方向推进,来获得较好的PSRR特性, 但该方法同样可能会导致整个环路的不稳定,所以输出电容的大小必须和PSRR折衷考虑.

1.3核心电路设计LDO的核心电路由PTAT电流源,误差放大器,功率管构成.如图3所示.

1.3.1 PTAT电流源设计 由启动电路和正温度系数电流源两部分组成.出于低功耗设计的考虑,尽量在LDO正常工作的时候将启动电路关闭.如图3所示,该结构的启动电路由晶体管M15~M19,以及电容C1、C2组成.当芯片上电时,C1未被充电,M19的栅极电位为低电位,此时M19导通,并将M13、M14的栅极电位拉高,破坏其静态平衡点,使PATA电流源正常启动.此时,由M15~M18构成的两级反相器对C1充电,当C1上极板的电位被拉高以后,M19截止关断.整个启动电路完全关闭,不影响PTAT电流源的正常工作[3].

图3 LDO的核心电路图

1.3.2 误差运算放大器设计 误差放大器的电路组成如图3所示.这是一个高增益、高PSRR的两级放大OTA.主要由三部分构成:第一级放大器Gm1、第二级放大器Gm2及稳压器频率补偿电路.第一级放大器Gm1是差分对输入的对称性OTA,由晶体管M1、M2、M3、M4、M5以及电阻R4、R5组成,对稳压器输出反馈电压和基准电压的差模信号进行放大;第二级放大器Gm2由晶体管M8、M9组成,用来提高误差放大器的开环增益,也可减小放大器的输出阻抗(可增大带宽);频率补偿电路由C3、R3组成,由密勒效应使得极点分离,并通过R3的调整,产生一个左半轴的零点做频率补偿[4].由图可计算出误差放大器的性能参数.

(8)

第一级输出阻抗为:Ro1≈ro5

(9)

第二级增益为:A2≈gm9(ro9‖ro8)

(10)

第二级输出阻抗为:Ro2≈ro8‖ro9

(11)

(12)

(13~14)

式中功率管自身寄生的栅极电容Cpar≈Cgs+Cgd;根据式(12)~(14)对相位裕度和环路增益进行折衷,从而优化环路的幅频特性和相频特性[5].

1.3.3 基准与偏置电路设计 基准电压源是LDO的核心模块之一,LDO输出电压的线性调整率、电源抑制比、温度特性等相关指标均与基准电压有关.因此设计一种电路结构简单而又具有良好性能的基准产生电路是非常关键的.从低功耗的角度考虑,尽量减小基准电路所消耗的静态电流的同时保证基准电压具有较好的温度系数、电源抑制比、线性调整率等要求.

本文中设计的基准电压源电路如图3所示,由晶体管M11、M12、M13、M14,电阻R6、R7、R8以及两只PNP型双极型管Q1、Q2组成.

基准源输出端的电压噪声为:

(15)

又因为带隙基准源应满足零温度系数:

(16)

其中M为两只PNP型双极晶体管的集电极电流之比,进一步简化得:

(17)

2 LDO 整体电路仿真

本文中基于BCD 0.5 μm CMOS工艺,采用cadence和Hspice对整体电路做仿真,并对各仿真波形做出详细的分析,若仿真条件未作说明,则默认是在tt工艺脚下,电源电压为3.3 V时,25 ℃环境温度下进行的.LDO线性稳压器输出电压的温度特性曲线如图4所示.仿真条件:负载电流为300 mA,Vin=3.3 V,工作温度从-40 ℃变化到85 ℃.

图4 LDO的输出电压的温度特性曲线(tt)

图5 LDO线性调整率变化曲线(tt)

(18)

(19)

LDO稳压器的负载调整率仿真结果如图6所示.仿真条件:输入电压为3.3 V,负载电流从0线性变化到300 mA,温度为25 ℃.从图中可以看出输出电压从1.826 1 V变化到了1.820 3 V,因而电路的负载调整率为:

(20)

图6 LDO负载调整率的仿真曲线(tt)

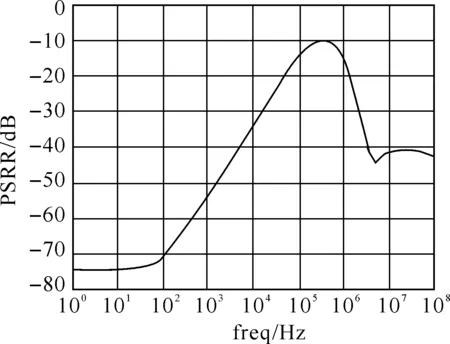

图7 LDO的PSRR特性曲线(typical corner)

LDO线性稳压器整体电路的PSRR特性曲线如图7所示.仿真条件:输入电压3.3 V,电流为300 mA,输出电压1.8 V,负载电容1 μF.由图可得,在Typical工艺脚下,低频的PSRR约为-75 dB;高频的PSRR约为-20 dB左右.该电路对电源电压的波动抑制能力符合设计要求.

3 测试结果

图8 芯片的显微照片

图8所示为该芯片的显微照片.对样片(sample)分别在空载、负载电流100 mA及满载(300 mA)3种情况,及3种输入电压(2.5 V、3.3 V、5.1 V)和3种工作温度条件(-20 ℃、27 ℃、85 ℃)下进行测试,结果显示,该电路有较宽的输入电压范围,输出电压为1.8 V.

图9所示为空载情况下,Vin=3.3 V时,LDO输出电压随温度的变化曲线;图10所示为满载情况下,Vin=2.5 V时,LDO输出电压随温度的变化曲线.对5个样片在-27 ℃条件下进行电源电压抑制比的测试,得出其均值曲线如图11所示.从图中可以看出,LDO线性稳压器的PSRR在3.25 MHz频率以下,最低约为-45 dB@1 MHz,最高约为-75 dB@217 Hz.图12所示为输出电压噪声测试曲线.结果显示,在10 Hz频率以下的输出电压闪烁噪声约为0.78 μV(P-P),在10 Hz至100 kHz频率范围内输出电压噪声约为0.1 μV(RMS),满足设计要求.

图9 空载时输出电压随输入电压和温度的变化

图10 满载时输出电压随输入电压和温度的变化

图11 -27 ℃下PSRR测试曲线(均值)

4 结论

图12 输出电压噪声测试曲线

本文中设计的这款LDO线性稳压器,有较宽的输入电压范围(2.5~5.1 V),输出电压1.8 V,高电源电压抑制比(PSRR≈-66 dB@1 kHz),该LDO的负载电流为300 mA(满载)、静态电流IQ低至μA级,具有低功耗和低噪声的特点,且芯片面积小(die size:X=836 μm,Y=796 μm)、外围电路简单.从芯片的测试数据来看,本文中设计的LDO线性稳压器能满足低功耗、低噪声和高稳定性的指标设计要求.

[1] 赖凡. 低压差电压调节器技术发展动态[J].微电子学,2004, 34(4):416.

[2] 吴晓波,李凯,严晓浪.高性能低压差性稳压器的研究与设计[J].微电子学,2006,36(3):347-351.

[3] Lam Y, Ki W.A 0.9 V 0.35 μm adaptively biased CMOS LDO regulator with fast transient response[C]//Proc of ISSCC Dig Tech,San Francisco, CA, USA,2008:442-443.

[4] Alicea P, Ortiz C, Perez R. Design of an adjustable, low voltage, low dropout regulator[J].Proceeding of the Fifth IEEE International Caracas Conference on Devices, Circuits and Systems,2004,5:24-26.

[5] Robert J M, Jose S M, Edgar S S. Full on-chip CMOS low-dropout voltage regulator[J].IEEE Transactions on Circuits and Systems,2007,54(9):1879-1890.

[6] 温晓珂,谈熙,闵昊. 用于射频SOC芯片的低噪声高电源抑制比LDO[J].固体电子学研究与进展,2011,31(3):432.