静态随机存储器低泄漏设计技术

2012-08-09郭雅琳

郭雅琳 ,程 滔

(1.工业和信息化部软件与集成电路促进中心,北京 100846;2.国家基础地理信息中心,北京 100830)

高性能SoC 系统,泄漏功耗已经与动态功耗越来越接近,目前国内外针对低泄漏设计技术进行大量研究。由于SoC 芯片性能需求越来越高,系统中内嵌的SRAM(用于多级Cache)容量也越来大,因此每次存取数据仅小部分容量的存储阵列工作,大部分阵列绝大部分时间处于非工作状态。其次,泄漏电流是与晶体管数目近似成正比,根据ITRS 预测,典型的微处理器中存储器的晶体管数目约占70%,且未来可能达到80%[1]。因此对于SRAM 低泄漏设计技术的大量研究,主要从3个方面考虑:(1)工艺材料的改进,采用高介电常数的栅氧化物等;(2)电路设计层面低功耗技术,采用众多电路设计方法降低静态泄漏电流;(3)系统设计层面低功耗技术,根据系统架构和应用采用动态电源电压和频率的调节(DVFS)技术等。本论文主要总结电路层面的低泄漏设计技术,并结合主流工艺进行分析。

一个CMOS 晶体管存在多种类型的泄漏电流:亚阈值泄漏,漏感应势垒降低GIDL 泄漏,耗尽层结穿通泄漏,栅隧穿泄漏,PN 结泄漏[2]。以上泄漏电流主要可以分为3种类型[3]:亚阈值泄漏电流、栅泄漏电流和耗尽层结泄漏电流。最新的先进工艺(45 nm 以下)采用了高介电常数的材料作为栅氧化物,因此栅泄漏电流并没有论文中预测的突出,因此泄漏电流主要是亚阈值泄漏[4]。亚阈值泄漏电流表示MOSFET 处于截止区时源端和漏端的泄漏电流,此电流通常在pA 量级,但是存储器晶体管数目越来越大,因此总的亚阈值泄漏电流对于功耗贡献越来越突出,因此本文总结了电路级的低泄漏设计技术,主要针对存储阵列的亚阈值低泄漏技术。

本文分两个方面总结亚阈值低泄漏技术:位线低泄漏技术,包括位线和字线的设计方法;存储阵列低泄漏技术,包括工作时和待机时存储阵列的低泄漏设计方法。

1 位线低泄漏技术

与存储阵列的泄漏相比,位线泄漏电流的值较小,但此泄漏会影响存储单元的可靠性。本文总结了降低位线泄漏电流的主要设计方法:(1)位线泄漏补偿;(2)位线电压校准;(3)负电压字线控制;(4)新型存储单元。

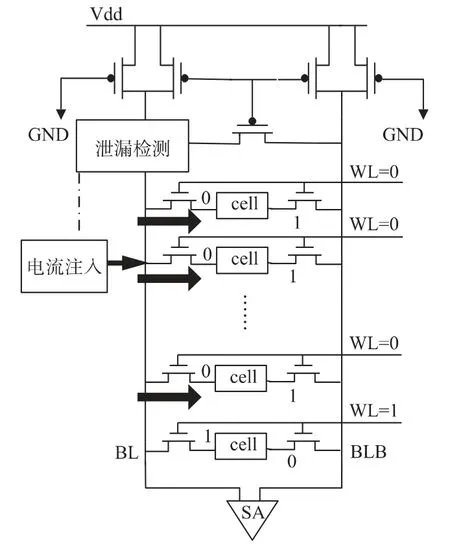

位线泄漏补偿是通过检测位线的泄漏电流值从而补偿泄漏电流,最终消除泄漏电流对灵敏放大器影响,如图1。此方法需要两个相位:首先,位线泄漏电流检测,其次位线上注入等量的电流来补偿泄漏电流。论文[5]在预充电相位,将位线的泄漏电流存储于额外的电容上,此电容的电压值与泄漏电流成正比。电容上的电压值控制PMOS 晶体管的栅端,实现电压到电流转换,从而补偿位线泄漏电流。此方法存在两个方面的缺陷:(1)检测和补偿基于动态电流镜实现,受晶体管阈值电压波动较大;(2)补偿相位时,电容直接连接PMOS 栅端,耦合噪声对于此节点的影响非常大。

图1 位线泄漏补偿原理

图2 给出位线电压校准原理[6],检测相位,得到位线失调电压,补偿相位,校准位线失调电压,消除位线泄漏对灵敏放大器影响。与位线泄漏补偿相比,位线电压校准模块位于位线与灵敏放大器中间,增加了SRAM 读取延迟。

图2 位线电压校准原理

负电压字线控制可以直接降低位线泄漏电流[7],通过增大栅源端和栅漏端的电压差,降低亚阈值跨导,从而降低泄漏电流的值。但是此方法中晶体管各端口间的电压差超过电源电压值,因此晶体管可靠性恶化。

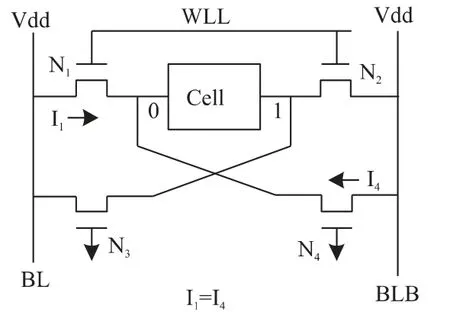

新型存储单元用于补偿和消除位线泄漏电流。图3 给出一种8 管的新型存储单元[8],2个额外的晶体管N3和N4可以完全补偿存储单元的泄漏,此方法受工艺偏差影响小,但是相比传统6 管存储单元,新型存储单元面积损耗40%。

图3 8T 存储单元

2 存储阵列低泄漏技术

存储阵列低泄漏技术同时需要考虑存储单元稳定性问题,下文分别总结了存储器工作时的低泄漏技术和待机时的低泄漏技术。

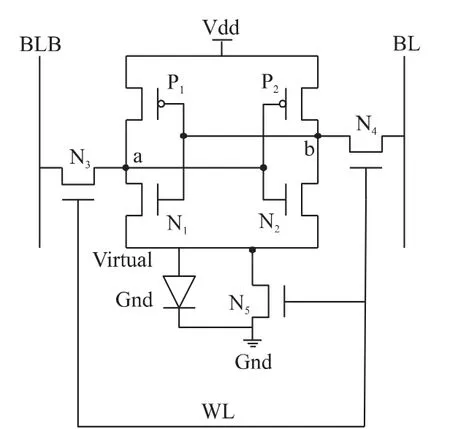

工作时低泄漏技术主要有3种方法:(1)调整存储单元中晶体管的阈值电压[9],为降低泄漏同时不影响性能,存储单元中PMOS 管可以采用高阈值管。为进一步降低泄漏电流,可以将存储单元中传输管改为高阈值管。存储单元中晶体管全采用高阈值管,可以更进一步降低泄漏电流。但是后2种方法会增加存储器的读取延迟,且需要工艺支持。(2)改变存储单元结构[10-11],通常采用8 管、9 管和10 管的新型存储单元,从而降低泄漏电流,但是此类方法都会增大存储阵列的面积消耗,降低面积效率。(3)动态调节体偏置电压[12],如图4,将非工作的存储阵列中NMOS 管体偏置电压抬高,而工作的存储阵列中NMOS 管体偏置电压调整为低电平,通过动态调节体偏置电压降低存储阵列的泄漏电流,但是此方法需要双阱工艺支持,增加了实现成本。

图4 动态体偏置电压调节

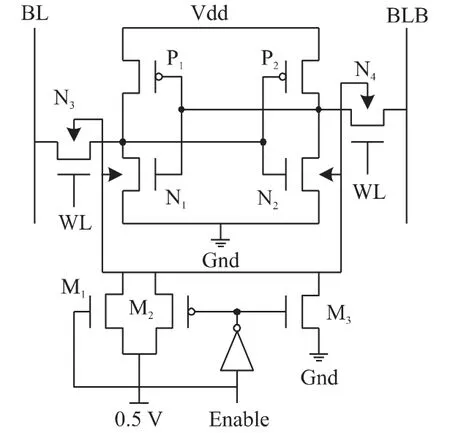

待机时低泄漏技术重点是考虑存储单元可靠性和泄漏之间的折中,低泄漏技术主要有3种方法:(1)存储阵列电源切断技术[13],通常采用睡眠管控制存储阵列的电源地,当处于待机工作时,这些晶体管可以切断存储阵列到电源地端的通路。此方法实现简单,存储阵列的电源地端电压值被抬高,从而降低泄漏,但是此方法易受耦合噪声干扰。为解决此问题,通常一个二极管连接的MOS 管并行连接切断管,如图5,但是这会影响泄漏电流的降低幅度。(2)体偏置电压控制[14],对存储阵列中晶体管的衬底偏置电压进行调节,提高MOS 管的阈值电压,从而降低泄漏电流。此方法效果明显,但对于主要泄漏的NMOS 管衬底电压调节需要双阱工艺,工艺要求高。(3)低电源电压控制[15],直接降低存储阵列的电源电压值,可以很明显的降低泄漏电流,如果采用LDO 供电,降低电源电压非常方便,但是相比于增加存储阵列电源地的电压值,此方法对于泄漏的降低更少。

图5 电源地切断技术

[1]International Technology Roadmap for Semiconductors[EB/OL].http://www.itrs.net/Links/2009ITRS/ Home2009.htm.

[2]Roy K,Mukhopadhyay S,Mahmoodi-Meimand H.Leakage Current Mechanisms and Leakage Reduction Techniques in Deep-Submicrometer CMOS Circuits[J].Proceedings of the IEEE,2003,91:305-327.

[3]Mukhopadhyay S,Raychowdhury A,Roy K.Accurate Estimation of Total Leakage in Nanometer-Scale Bulk CMOS Circuits Based on Device Geometry and Doping Profile[J].Computer-Aided Design of Integrated Circuits and Systems,IEEE Transactions on,2005,24:363-381.

[4]Calimera A,Macii A,Macii E,et al.Design Techniques and Architectures for Low-Leakage SRAMs[J].Circuits and Systems Ⅰ:Regular Papers,IEEE Transactions on,2012,59:1992-2007.

[5]Agawa K,Hara H,Takayanagi T,et al.A Bitline Leakage Compensation Scheme for Low-Voltage SRAMs[J].Solid-State Circuits,IEEE Journal of,2001,36:726-734.

[6]Ya-Chun,Shi-Yu H.A Technique for Combating Excessive Bitline Leakage Current in Nanometer SRAM Designs[J].Solid-State Circuits,IEEE Journal of,2008,43:1964-1971.

[7]Itoh K,Fridi A R,Bellaouar A,et al.A Deep Sub-V,Single Power-Supply SRAM Cell with Multi-VT,Boosted Storage Node and Dynamic Load[C]//VLSI Circuits,1996.Digest of Technical Papers.,1996 Symposium on,1996,132-133.

[8]Alvandpour A,Somasekhar D,Krishnamurthy R,et al.Bitline Leakage Equalization for Sub-100 nm Caches[C]//Solid-State Circuits Conference,2003.ESSCIRC'03.Proceedings of the 29th European,2003,401-404.

[9]Azizi N,Najm F N,Moshovos A.Low-Leakage Asymmetric-Cell SRAM[C]//Very Large Scale Integration(VLSI)Systems,IEEE Transactions on,2003,11:701-715.

[10]Calhoun B H,Chandrakasan A P.A 256-kb 65-nm Sub-Threshold SRAM Design for Ultra-Low-Voltage Operation[J].Solid-State Circuits,IEEE Journal of,2007,42:680-688.

[11]Chang L,Fried D M,Hergenrother J,et al.Stable SRAM Cell Design for the 32 nm Node and Beyond[C]//VLSI Technology,2005.Digest of Technical Papers.2005 Symposium on,2005,128-129.

[12]Kim C H,Jae-Joon K,Mukhopadhyay S,et al.A Forward Body-Biased Low-Leakage SRAM Cache:Device,Circuit and Architecture Considerations[C]//Very Large Scale Integration(VLSI)Systems,IEEE Transactions on,2005,13:349-357.

[13]Agarwal A,Hai L,Roy K.DRG-Cache:A Data Retention Gated-Ground Cache for Low Power[C]//Design Automation Conference,2002.Proceedings.39th,2002,473-478.

[14]Kim C H,Roy K.Dynamic Vt SRAM:A Leakage Tolerant Cache Memory for Low Voltage Microprocessors[C]//Low Power Electronics and Design,2002.ISLPED'02.Proceedings of the 2002 International Symposium on,2002,251-254.

[15]Elakkumanan P,Narasimhan A,Sridhar R.NC-SRAM—A Low-Leakage Memory Circuit for Ultra Deep Submicron Designs[C]//SOC Conference,2003.Proceedings.IEEE International[Systemson-Chip],2003,3-6.