基于FPGA的多通道HB6096航空总线接口设计

2012-08-08刘江

刘 江

(中国西南电子技术研究所,成都 610036)

1 引 言

HB6096航空总线是我国在国外ARINC429航空总线基础上发布的国内航空电子设备总线传输协议,其数据传输方式及传输电平与ARINC429基本相同,是一种单向点对多广播模式高速差分信号[1]。

国内传统HB6096总线接口设计主要依靠国外ARINC429专用集成电路实现。这些专用集成电路不仅面临国外技术封锁,还存在接口单一、集成度低的问题。随着我国航空工业的发展,越来越多的机载设备挂接在系统总线上,这时候传统的HB6096接口设计方案已不能满足小型化、高集成度及国产化设计需求。

为提高硬件集成度,本文立足于国产化设计思路,依据HB6096总线传输标准,根据设计需求,基于FPGA实现了多通道HB6096航空总线接口设计,并给出了总体设计方案、硬件、软件详细设计方法及测试结果。

2 HB6096总线简介

HB6096总线协议标准是我国航空工业部在1986年发布的SZ-01数字信息传输系统。协议要求每传输完成一个32位的数字字之后,以传输周期间至少5位的时间间隔为基准,紧跟该字间隔后要发送的第一位的起点即为新字的起点[2],而ARINC429则要求4位的时间间隔[3]。总线数据传输依靠两根差分信号线完成,速率分为高速工作状态(位速度100×103bit/s)及低速工作状态(位速度12~14.5×103bit/s),并且要求高速率和低速率信息不在同一传输总线上传输。

HB6096总线调制方式采用双极性归零制的三态码调制方式,即调制信号由“高”、“零”和“低”状态组成的三电平状态调制。A、B端总线电平状态及转换为TTL电平后对应的逻辑状态关系如图1所示。

图1 HB6096总线传输电平及数据转换关系Fig.1 The voltage of HB6096 bus and data conversion

3 设计需求

要求总线接口模块能接收、发送多路HB6096总线数据,接口模块通过设备内并行总线实现通信。

(1)HB6096总线要求

1)8路HB6096总线接收接口;

2)5路HB6096总线输出接口;

3)传输速率:100 kbit/s或12.5 kbit/s;

4)缓存要求:每个HB6096总线通道(接收或发送)缓存不小于1 024 byte。

(2)设备内自定义总线接口

1)16位数据总线;

2)16位地址总线;

3)读 、写 、片选 、中断 、复位信号 。

4 总体设计

因HB6096传输电平与ARINC429基本相同,国内传统的HB6096多通道总线接口设计大多借用ARINC429设计方案,即采用处理器加进口协议芯片,如文献[4]采用CPLD和DSP相结合的方式,提出了一种2片DEI1016芯片并行工作的方案并实现。两芯片共构成2收4发6路429通道,采用中断方式并行高速运行;或如文献[5]基于SOPC技术,以NiosII软核处理器为系统核心,并配合ARINC429通信协议芯片HS3282和HS3182实现对429总线数据的收发。

本设计方案立足国产化设计,由FPGA完成HB6096协议解析,每个总线通道(接收或发送)缓存均由FPGA内部RAM生成,每个通道设计一个状态机进行独立管理,由控制内核完成与设备内并行总线的数据访问,即基于FPGA实现多通道HB6096航空总线数据收发。

5 硬件设计

硬件主要由电源、时钟、调试接口、FPGA、电平转换电路、隔离驱动电路等组成,硬件原理框图如图2所示。

图2 硬件原理框图Fig.2 Schematic block diagram of hardware

硬件核心FPGA采用ACTEL公司的A3P1000。设计要求8个接收通道,5个发送通道,每个通道缓存要求1 024 byte,一共需用(8+5)×1 024=104 kbit。A3P1000内部 RAM 资源是144 kbit,满足设计需求。

外围方案是:隔离驱动采用164245系列芯片完成TTL到LVTTL电平的转换与隔离;接收通道的电平转换芯片采用HOLT公司的HI-8588,发送通道的电平转换芯片采用HOLT公司的HI-8585;系统时钟50MHz;电源使用+5 V、+12 V、-12 V电压满足HB6096电平转换芯片的使用。

6 软件设计

6.1 设计方案

HB6096数据是32位串行数据,设备内部数据总线为16位并行数据,需要将HB6096串行数据拆分为两包16位的并行数据。接收通道采用16位宽度、512位深度的DPRAM,发送通道采用32位宽度、256位深度FIFO。每个接收通道分配一个DPRAM,每个发送通道分配一个FIFO缓存,各个通道相互独立,由状态机负责运行工作。当外部CPU需要对模块进行数据读出、写入时由控制内核完成相关地址映射、寄存器读写工作。

整个软件的功能结构框图如图3所示。

图3 软件功能结构框图Fig.3 Block diagram of software configuration

软件语言采用VHDL,编译环境采用ACTEL公司产品适用的Libero9.1版本。

6.2 接收通道设计

6.2.1 32位串并转换器

根据图1所示双极性归零码的特性,32位串并转换器采用A与B异或作为数据采集的触发信号。外部CPU根据系统实际使用情况,通过模块间自定义总线配置速率寄存器,设置分频器参数,生成相应10 MHz或1.25 MHz的采样时钟,以100倍的采样速率对A端和B端的信号同时进行采集。数据采集分为两次校验:单bit采集数据必须满足A和B的异或关系,即A为逻辑“1”时B必须为逻辑“0”,B为逻辑“1”时A必须为逻辑“0”;32 bit数据采集完成后再进行奇偶数据校验,校验不通过的数据直接抛弃。两次校验通过后按照相应协议格式对32 bit的并行数据进行转换,转换完成后将32 bit数据送入锁存器,置相关标志位,并做好下一包总线数据采集准备。

6.2.2 DPRAM写状态机

DPRAM写状态机的流程如图4所示。

图4 DPRAM写状态机流程图Fig.4 The flow chart of state machine for writing DPRAM

图4说明如下:

STEP0:等待;

STEP1:置 CS、WR 有效,将低 16位数据送DPRAM,将虚拟地址+地址指针值送DPRAM;

STEP2:置 CS、WR 无效;

STEP3:置 CS、WR 有效,将高 16位数据送DPRAM,将虚拟地址+地址指针+1值送DPRAM;

STEP4:置 CS、WR 无效;

STEP5:地址指针累加。

在串并转换成功标位RX_SIGN置有效后,启动数据拆分及DPRAM写状态机。将32位并行数据从锁存读出并拆分为 2包16位的并行数据。根据DPRAM的写数据时序,将虚拟的片选、写等控制信号置有效,然后按照先写低位,再写高位的方式,通过分配的虚拟地址,分两次将一包HB6096数据写入DPRAM双口。每写入一组16 bit的数据后,地址指针自动加1,确保数据能够进行累进存储,每写完一包HB6096数据地址指针实际累积加2。当存储到第512个数据(实际上是第256个HB6096数据)时,将地址指针自动清零。第513个数据来后,将原来存储的第1包数据进行覆盖存储。

6.2.3 DPRAM存储

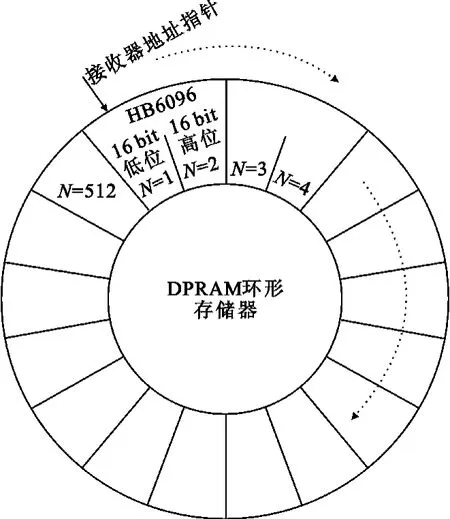

根据产品设计要求,结合FPGA的RAM资源,在数据量不大的情况下,我们采用DPRAM环形存储的方式,即当存储BUFFER装满之后,重复写入该段存储空间,覆盖之前的数据。DPRAM环形存储器结构如图5所示。

图5 DPR AM环形存储器结构Fig.5 Architecture of circular DPRAM

图5说明如下:

(1)每个通道配置DPRAM环形存储器1 kbyte,宽度为16位,深度512位;

(2)每一包HB6096数据先写16 bit低位,再写16 bit高位;

(3)每写入一包HB6096数据,接收器地址指针自动加2;

(4)当存储第256包HB6096数据后,地址指针清零;

(5)当存储第257包HB6096数据时,该包数据将覆盖之前接收到的第一包数据。

抛弃传统外部挂接双口芯片而在FPGA内部开辟DPRAM的优点是:节约印制板空间,节约成本,抗干扰能力强,存储速度快,最重要的是可以实现多通道数据独立并行处理。每个通道设计一个状态机进行独立管理,将数据写入对应通道的DPRAM,完全实现多通道的并行运行。此种方案比外挂一个DPRAM芯片然后再依靠处理器或控制内核去管理各个通道,依次逐个写入各个通道接收数据要合理有效得多,也避免了各通道满负荷运行时的数据堵塞。这也是本方案的创新之处。

6.3 控制内核设计

控制内核是整个总线接口模块的数据传输、协调控制单元,整个控制内核主要分为寄存器配置、总线接收地址指针读取、总线数据接收读取、总线数据发送写入。

控制内核通过对各个接收通道、发送通道统一进行地址编码分配、接口映射,可实现与外部处理器进行总线访问。上电后,外部处理器先配置各个接收、发送通道的HB6096总线传输速率。当接收通道收到数据后,对应接收通道地址指针转动。控制内核可向CPU处理器发送中断信号,也可以由CPU处理器以主动方式查询各个接收通道的地址指针值。当CPU发现接收地址指针偏移后,计算偏移量,得出接收到了多少包总线数据,然后将该段数据读出。当需要发送数据时,CPU通过控制内核先查询该通道的FIFO存储器是否已经存满。若可以继续写入数据,则通过控制内核的发送通道地址映射,将发送数据写入对应FIFO。

6.4 发送通道设计

由于发送数据是外部处理器为主动模式,每一包HB6096数据均依照对应发送通道进行发送,因此只需要对每一个发送通道的地址进行标记。每次往该通道发送数据,只需往该通道的地址写入数据就可以。因此,发送缓存采用基于PIPELINE管道结构的FIFO缓存更合理。

6.4.1 写FIFO状态机

根据设计要求,采用 32×256的 FIFO满足1 kbyte要求。详细设计如下:以发送1通道为例,设置TX1-ADDR地址为发送1通道的数据位低位,TX1-ADDR+1为数据位高位地址。CPU写入数据时,先写入低16位数据到寄存器,再写入高16位数据送入寄存器,同时给出该通道数据已组合好的标志位CPU-WR1。利用此标志位,产生符合FIFO时序的写信号,将32位HB6096数据一次写入FIFO。

其他发送通道类似。

6.4.2 读FIFO状态机

读FIFO状态机采用FIFO缓存在存入数据后状态标志位的跳变信号作为启动信号,再根据FIFO的读时序,产生相应的片选、读信号,将数据读出。读FIFO状态机需要注意的是,状态机在读数前,需要先检查32位并串转换器的忙标志位信号。如果并串转换器处于忙状态,说明上一包HB6096数据还没有发送完成,需要等待;如果已经转换完成,证明上一包数据已发送,才可以读取下一包数据。

6.4.3 32位并串转换器

32位并行数据从FIFO中读出来后,利用发送控制寄存器,将发送数据的传输速率以及发送数据的奇、偶校验方式信息传递给32位并串转换器。转换器根据寄存器配置信息选择分频时钟及数据校验方式,然后对32位并口数据按照100 kHz或12.5 kHz时钟,结合协议要求进行格式转换及编码工作。编码工作开始后置忙标志位,表明转换器正处于发送工作状态,禁止再从FIFO读数,防止数据丢失。直到32位数据已转换完成,并按照HB6096总线要求设置5个比特位的时间间隔后,再将忙标志位置为无效,启动读FIFO状态机读出下一包数据。

7 测试验证

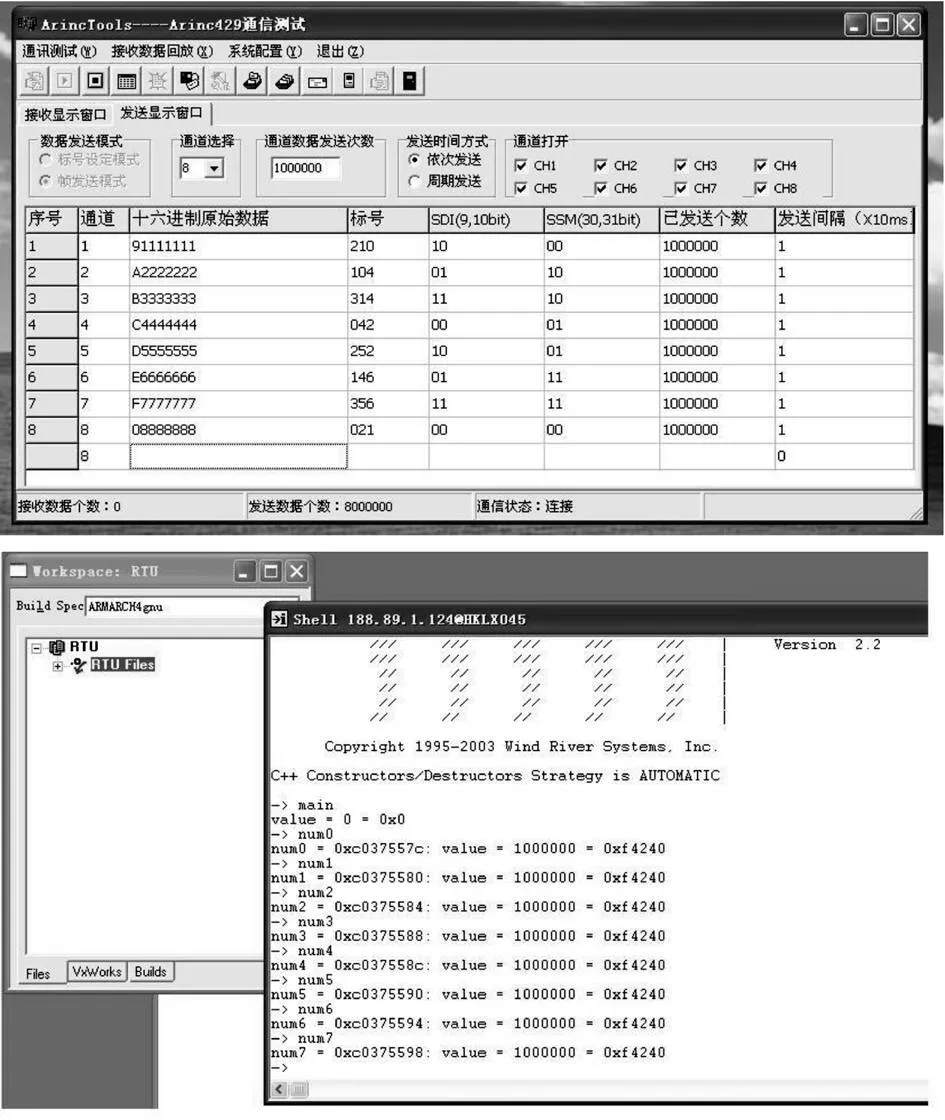

采用旋极公司Arinc429接口板及ArincTools通信测试软件,结合CPU处理器TORNADO软件,分别对本模块的发送和接收通道进行测试。

测试发送性能时,ArincTools软件处于接收状态,利用测试程序使5个发送通道全部打开,每个通道同时发送100万包HB6096数据,通信速率100 kbit/s。检测结果显示本模块所有发送通道均无数据错误或丢失。发送通道测试结果如图6所示。

图6 发送通道测试结果Fig.6 The test result of sending channels

测试接收性能时,ArincTools软件处于发送状态,8个发送通道全部打开,每个通道同时发送100万包HB6096数据,通信速率100 kbit/s。检测结果显示本模块所有接收通道均无数据错误或丢失。接收通道测试结果如图7所示。

图7 接收通道测试结果Fig.7 The test result of receiving channels

8 结束语

本文从工程应用角度,基于FPGA设计了8路HB6096总线接收及5路HB6096总线输出的总线接口,硬件资源开销小,系统满足设计需求,软件设计构架合理。目前该设计已成功应用于某机型HB6096航空总线接口模块,经模拟测试及高低温等各项环境试验条件验证,模块时序工作正常,稳定可靠。

此设计方案摒弃了传统HB6096总线数据处理依赖国外进口ARINC429总线集成协议芯片办法,实现了国产化设计;摒弃了采用ARINC429集成芯片只能单、双路收发的局限性,实现了多通道的数据收发;每个通道配置独立的缓存,实现了多通道的独立并行运转,节约资源,高效稳定;采用CPU主动查询方式读取接收数据,保证了多路总线数据的稳定接收,避免了可能出现的掉数问题。该设计思路还可拓展应用于国内1553B等航空总线多通道接口国产化设计。

[1] 张桢,孙沛.基于FPGA的ARINC429总线通讯板设计[J].航空计算技术,2010,40(4):112-115.ZHANG Zhen,SU N Pei.Design of Multi-channel ARINC 429 Communication Board Based on FPGA[J].Aeronautical Computing Technique,2010,40(4):112-115.(in Chinese)

[2] HB6096-86SZ-01,数字信息传输系统[S].HB6096-86SZ-01,Digital information transfer system for the standards of aeronautic industry department of the prc[S].(in Chinese)

[3] ARINC specification 429P3-19,mark 33 digital information transfer system(dits)-part 3-file data transfer techniques[S].

[4] 宋桂华,赵伟,刘建业.多路ARINC429数据传输的设计与实现[J].微处理机,2009,30(3):116-118.SONG Gui-hua,ZHAO Wei,LIU Jian-ye.Design and Realization of Multi-channel ARINC 429 Data Transmission Technique[J].Microprocessors,2009,30(3):116-118.(in Chinese)

[5] 陈东,韩治中,梁勇.基于 SOPC的ARINC429总线接口设计[J].工业仪表与自动化装置,2010(1):30-33.CHEN Dong,HAN Zhi-zhong,LIANG Yong.The design of ARINC429 data bus interface based on SOPC[J].Industrial Instrumentation&Automation,2010(1):30-33.(in Chinese)