基于DSP系统的FPGA精插补器设计

2012-07-04范良志

乔 桥,范良志

QIAO Qiao,FAN Liang-zhi

(武汉纺织大学 机电学院,武汉 430074)

0 引言

FPGA是新型的大规模可编程数字集成电路器件。它充分利用计算机辅助设计技术进行器件的开发与应用。用户借助于计算机不仅能自行设计专用集成电路芯片,还可在计算机上进行功能仿真和实时仿真,及时发现问题,调整电路,改进设计方案。这样,设计者不必动手搭接电路、调试验证,只须在计算机上操作很短的时间,即可设计出与实际系统相差无几的理想电路。而且,FPGA器件采用标准化结构,体积小、集成度高、功耗低、速度快,可无限次反复编程,因此,成为科研产品开发及其小型化的首选器件,其应用极为广泛。

本文介绍了二次插补算法中的精插补器在FPGA中的实现方法,插补方法经过多年的发展已形成了众多的门类,一般依据数控系统控制方式的不同将插补方法分为两大类:基准脉冲插补和数据采样插补。基准脉冲插补是用于开环控制系统的插补方法,它用理论直线上采用各种方法离散化得出的驱动信号直接驱动传动装置,没有检测实际加工轨迹误差的反馈部件;数据采样插补用于闭环数控系统中,在目前的检测和运算技术还不能较快的实现插补与检测同步修正的情况下,通常采用时间分割的思想,将整个插补过程分为粗插补和精插补两个阶段[1]。粗插补器在给精插补器发送下一段插补数据之前若干个周期从实时位置反馈单元得到实时位置数据,并依据此数据对下一段加工数据进行校正,从而使实际加工轨迹在控制器的监控下始终处于误差允许范围之内,这是一种二次插补方法。本文就是介绍了二次插补方法中精插补器的设计。最终将该精插补器运用于基于DSP控制平台的伺服控制系统中。

1 伺服控制系统硬件设计

1.1 系统硬件组成

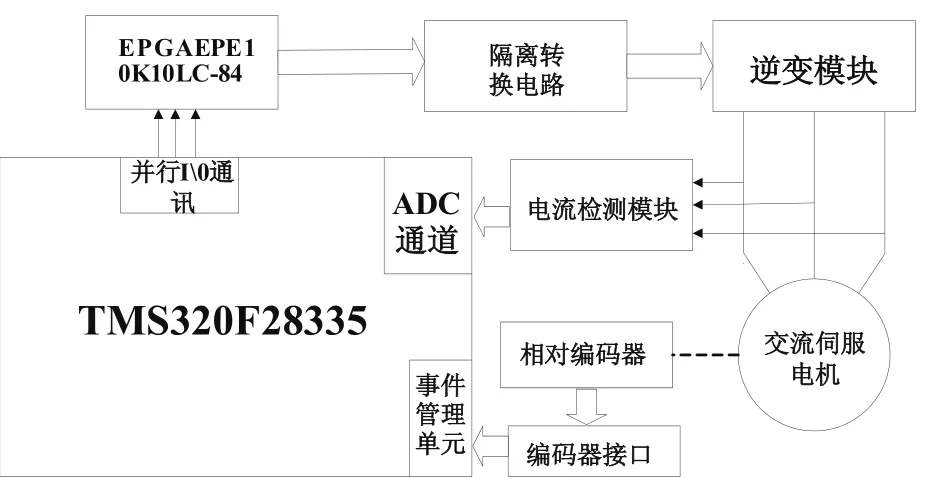

系统硬件框图如图1所示:

图1 系统硬件框图

该伺服系统中心控制电路采用TI公司的TMS32OF28335芯片。外设还包括6个捕获单元,用以捕获编码信号和集成的3路正交编码电路。另外本系统采用FPGA核心芯片EPE10K10LC-84来根据转子位置信号通过逻辑关系输出六路PWM 波[4]。

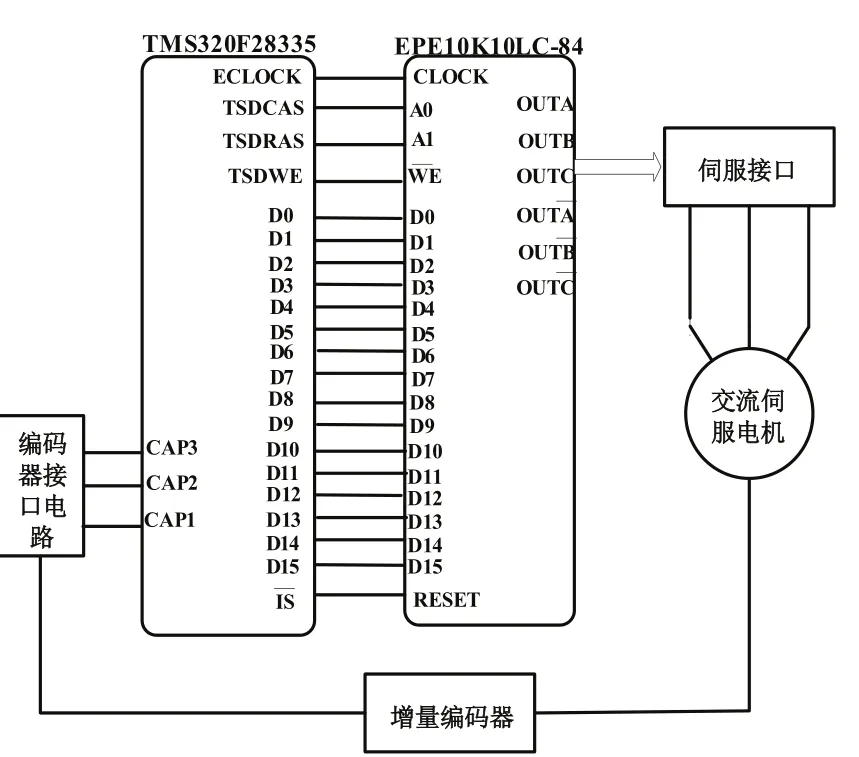

1.2 DSP与FPGA总线接口设计

本设计中TMS32OF28335与EPE10K10LC-84 的接口电路如图2中所示。其中的工作频率为32.47MHz,为保证DSP和FPGA在工作时序上的一致性,FPGA的时钟源由DSP的ECLOCK脚提供,FPGA同步工作在32.47MHz 。DSP地址线TSDCAS(行选通) ~TSDRAS(列选通)、数据线D0~D15分别于FPGA的地址线A0~A1和数据线相连, IS为DSP与FPGA复位信号,WE为DSP的写控制信号,当需要访问 FPGA空间时,引脚输出低电平选通 FPGA。CAP1~CAP3为DSP的事件管理模块的输入端口,用于接收编码器的位置反馈信号[2]。

图2 DSP与FPGA接口图

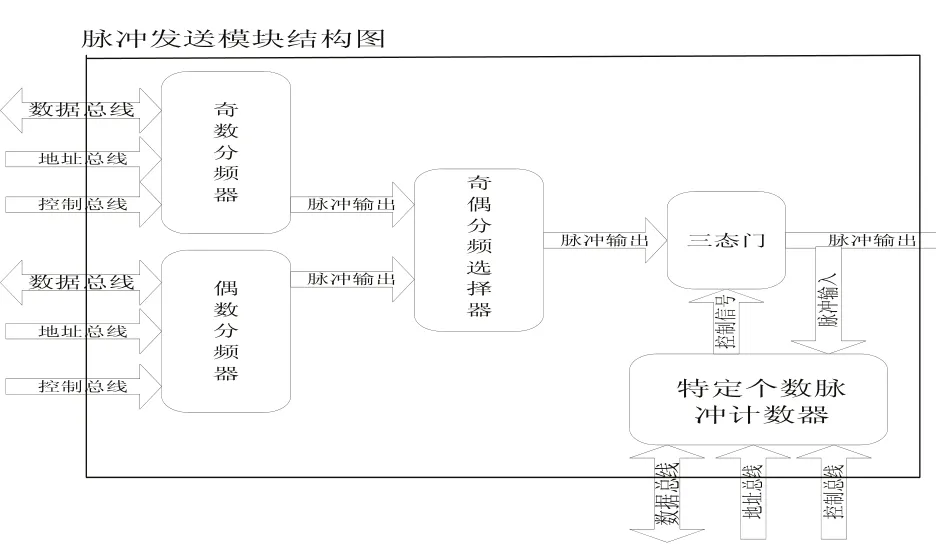

图3 FPGA精插补器模块框图

2 FPGA精插补器内部组成及电路介绍

2.1 FPGA精插补器组成

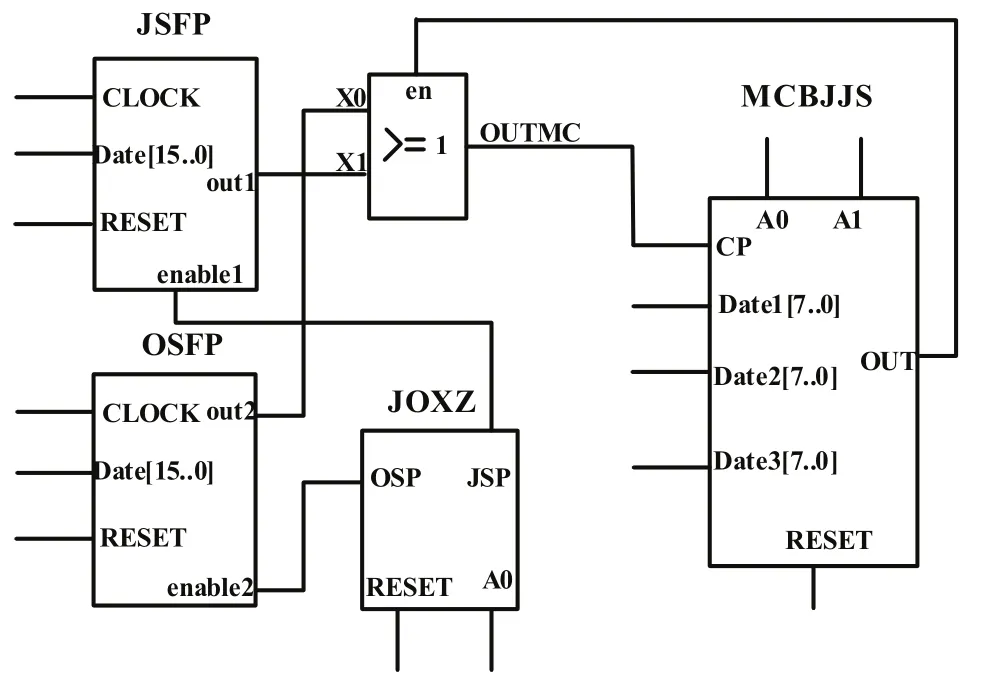

对于FPGA精插补器模块,其中的关键技术就是如何实现占空比为50%整数分频和如何实现特定个数的脉冲发送。在本系统中整数分频是由奇数和偶数两种分频器组成。而实现特定个数的脉冲发送时,系统设计了计数模块,首先通过数据总线、地址总线和控制总线,把24位的二进制代表脉冲个数的数据分三次写到计数模块的三个8位的寄存器中,然后打开计数模块的计数功能,让其记录从分频器中发出的脉冲个数,当它记录的脉冲个数和设定的脉冲个数相等时,就发出信号,停止分频器继续发送脉冲,从而达到实现特定个数脉冲的发送功能。FPGA精插补器整体模块框图如图3所示。奇偶分频选择(J O X Z)和脉冲比较计数(MCBJJS),其内部电路及各模块之间的接线电路如图4所示。

图4 FPGA内部电路图

图中各模块功能及引脚说明如下[3]:

奇数分频器(JSFP)实现的是以1-65536中的奇数为参数的分频功能,该功能模块有一个时钟输入信号“Clock”管脚,用于接受外部基准时钟信号,最大可以接受32.47MHz的时钟信号,参数输入通过“Date[15..0]”数据总线输入,“Reset”管脚为复位管脚,每当一次参数更新时,都要使“Reset”管脚电平为“高”,才能使更新操作有效,但要注意的是:“Reset”管脚电平不能一直为“高”,复位以后要立刻变为“低”,否则输出为“0”。“enable1”为选通使能脚,该信号由奇偶分频选择(JOXZ)寄存器提供。

偶数分频器实现的是以2-65535中的偶数为参数的分频功能其他引脚功能与奇数分频器一致。

奇偶分频选择(JOXZ)的作用在于:当输入的参数是奇数时,就打开奇数分频器通道,让系统输出的脉冲来自于奇数分频器,反之,如果

2.2 FPGA内部寄存器及电路设计

根据2.1所述,FPGA内部寄存器由四部分组成:奇数分频(JSFP)、偶数分频(OSFP)、系统输入的分频参数是偶数,就应该选择偶数分频器,使系统输出的脉冲来自于偶数分频器。该功能模块如图4总图中的JOXZ模块。图中用两个输出信号分别控制奇数分频器和偶数分频通道。当“jfp” 管脚和“ofp”管脚的输出电平组合为“10”时,选择的是奇数分频器;当为“01”时,选择的是偶数分频器;当无操作时,电平组合为“00”,即两个分频器都被关闭。值得注意的是:这两个管脚的输出电平组合没有为“11”的状态,即不可能同时打开两个分频器。而输出状态是由输入的“A0”和“reset”两个信号的状态控制。当“A0”和“reset”的状态为“10”时,即开奇数分频器通道,当为“00”时,即开偶数分频器,一旦“reset”的状态变为“1”时,不管“A0”为什么状态,则都要关闭两个脉冲输出通道。

脉冲比较计数(MCBJJS)的功能主要是完成对输入脉冲的计数,当输入脉冲个数于设定的个数相等时,输出管脚“out”的电平由“1”变为“0”,从而控制三态门的使能端口“en”,是其处于截止状态,这样就使得输出没有脉冲信号了,即使系统停止向电机驱动器发脉冲。代表计数脉冲个数的参数输入到内部三个八位的寄存器里,然后通过“reset”复位信号使该模块重新以新的参数计数,“reset”复位信号有效时为“1”,复位后要使信号变为“0”,否则该模块将不能进入计数状态,被计数的脉冲从“cp”管脚输入。

系统的脉冲输出信号通过三态门的“OUTMC”提供给外部伺服接口。

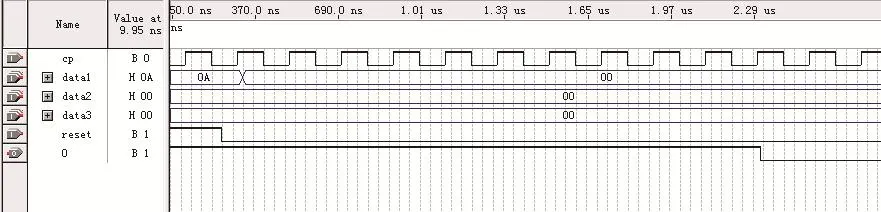

计数10个脉冲的仿真波形图如图5所示。

图5 计数10个脉冲的仿真波形图

3 反馈模块实现

3.1 编码器原理

在该伺服系统中增量式旋转编码器主要起到位置及速度反馈的作用。

增量式旋转编码器通过内部两个光敏接受管转化其角度码盘的时序和相位关系,得到其角度码盘角度位移量增加(正方向)或减少(负方向)。在接合数字电路特别是单片机后,增量式旋转编码器在角度测量和角速度测量较绝对式旋转编码器更具有廉价和简易的优势。

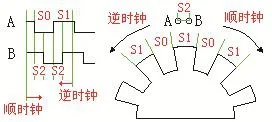

增量式旋转编码器工作原理如图6所示:

图6 旋转编码器工作原理图

其中A、B两点对应两个光敏接受管,A、B两点间距为S2 ,角度码盘的光栅间距分别为S0和S1[4]。

当角度码盘以某个速度匀速转动时,那么可知输出波形图中的S0:S1:S2比值与实际图的S0:S1:S2比值相同,同理角度码盘以其他的速度匀速转动时,输出波形图中的S0:S1:S2比值与实际图的S0:S1:S2比值仍相同。如果角度码盘做变速运动,把它看成为多个运动周期(在下面定义)的组合,那么每个运动周期中输出波形图中的S0:S1:S2比值与实际图的S0:S1:S2比值仍相同。通过输出波形图可知每个运动周期的时序,如表1所示。

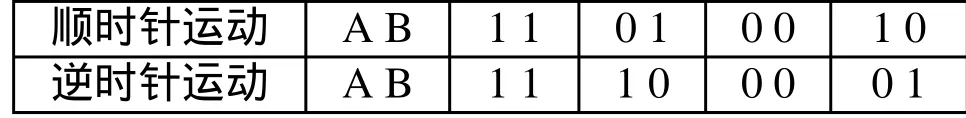

表1 运动周期时序表

我们把当前的A、B输出值保存起来,与下一个A、B输出值做比较,就可以轻易的得出角度码盘的运动方向。如果光栅格S0等于S1时,也就是S0和S1弧度夹角相同,且S2等于S0的1/2,那么可得到此次角度码盘运动位移角度为S0弧度夹角的1/2,除以所消毫的时间,就得到此次角度码盘运动位移角速度。S0等于S1时,且S2等于S0的1/2时,1/4个运动周期就可以得到运动方向位和位移角度,如果S0不等于S1,S2不等于S0的1/2,那么要1个运动周期才可以得到运动方向位和位移角度了。

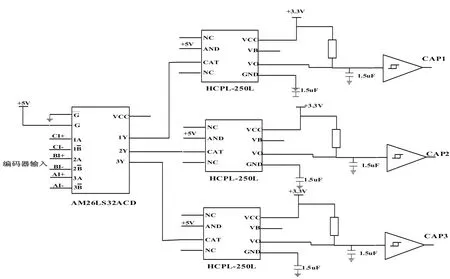

3.2 编码器脉冲采集的差分电路设计

由编码器输出的六路差分信号,经过差分信号处理芯片AM26LS32ACD及其处理电路,转化为DSP芯片能够接受的捕获信号,该差分信号处理电路如图7所示[5]。

其中AI+、AI-、BI+、BI-、CI+CI-为编码器六路输入信号,CAP1、CAP2、CAP3为提供给DSP的捕捉信号。

4 VHDL语言实现

在该系统中,主CPU为DSP控制平台,主要完成数字信号的处理运算,它把位置、方向和速度信号通过数据总线写入FPGA(脉冲发送模块)内的相关寄存器,然后发送启动信号,这样脉冲发送模块会自动完成电动机的定位和调速,达到精确的位置和速度控制。该系统用硬件描述语言(VHDL)编写了精插补器中的各个功能模块,并进行了功能和时序仿真,然后把代码通过专用下载线下载到电路板上的FPGA芯片中进行调试。以下为奇偶分频选择器的VHDL语言实现。

图7 编码器差分信号处理电路

5 结束语

FPGA是一种非常有前途的新技术,很适合于科研工作中的样机及新产品的开发应用。本文主要是研究二次插补算法中的精插补器在FPGA中的实现方法。综合仿真和实际测试表明,设计的基于DSP系统的FPGA精插补器能比较灵活方便的控制伺服电机的速度和方向,达到了设计的要求。

[1] Roche,Stephan.Implement a stepper-motor driver in a CPLDE[J].EDN,2007(2):90.

[2] 刘昌华.数字逻辑EDA设计与实践—— MAX+PLUS与Quartus[M].北京:国防工业出版社.2006.

[3] 王金明.数字系统设计与Verilog HDL[M].北京:电子工业出版社,2006.

[4] 曹东杰,韩峰,任云燕.单片机控制步进电机按S形曲线升降频设计[J].弹箭与制导学报,2006,26.(2):157- 169.

[5] 孙佐.基于8XC196单片机的EPA和PTS实现伺服电机控制[J].控制与检测.2005.