多晶硅部分剥离技术对抗辐照VDMOS动态特性的影响

2012-04-27大连东软信息学院宋文斌蔡小五

大连东软信息学院 宋文斌 蔡小五

1.引言

功率VDMOS器件具有开关速度快,开关损害小、输入电阻高、频率特性好等优点,被广泛应用于高频开关器件领域[1]。功率VDMOS器件的开关特性是由其本征电容和寄生电容共同决定的[2]。单从器件的开关特性考虑,我们希望栅氧化层厚度略大些[3],因为寄生输入电容Ciss的大小随栅氧化层厚度的增加而减小。然而,在考虑VDMOS器件的抗辐照特性时,为了总剂量辐照加固的需求,需要减薄氧化层的厚度,这样势必增加器件的寄生输入电容。因而,如何有效减小VDMOS器件的寄生电容,成为抗辐照VDMOS器件设计的难题。

图1为100V抗辐照VDMOS寄生电容随栅氧化层变化情况曲线。有由图可见,栅氧化层的厚度直接影响器件的寄生输入电容Ciss的大小,随着栅氧化层厚度的增加,VDMOS器件的寄生输入电容Ciss在减小。随着栅氧化层厚度的增加,VDMOS器件的寄生输出电容Coss和反馈电容Crss基本没有改变。在影响VDMOS器件的寄生电容的Ciss参数中,栅漏电容Cgd尤为重要[5]。Cgd直接影响器件的输入电容和开关时间,Cgd通过密勒效应使输入电容增大[5],从而使器件上升时间tr和下降tf时间变大。

2.研究重点

本文在减薄氧化层的厚度,保证总剂量辐照加固的需求的前提下,研究了多晶栅部分剥离技术对器件寄生电容的改善情况,研究了器件结构结构调整对VDMOS器件参数、尤其是Cgd参数的影响。如图2所示,我们采用漂移区多晶硅部分剥离技术以减小器件的寄生电容,该结构断开了VDMOS漂移区上方的多晶硅条,同时,保留了该区域的场氧化层。在该器件结构中,由于移除了多晶栅和漂移区交叠处的部分多晶硅栅,减小了栅漏电容Cgd平板电容的面积,减小了栅电荷Qg。从而降低了栅漏电容Cgd。然而,该结构对栅漏电容Cgd有多大的影响,多晶硅部分剥离窗口的尺寸对电容Cgd的影响究竟有多大,该结构还会对哪些器件参数产生明显改变,需要做进一步的定量计算研究才能确定,这对于分析该结构对器件寄生电容改善的效果是至关重要的,也是本文的工作重点。

图1 寄生电容随栅氧化层厚度变化情况Fig1.parasitic capacitance changing rate with different gate oxide thickness

图2 采用多晶硅部分剥离技术技的VDMOS单元Fig2.The VDMOS cell with polysilicon lift-off technic

图3 寄生电容随VD变化情况Fig3.Parasitic capacitance changing rate with different VD

图4 栅电荷随栅压VGS变化情况Fig4.Gate charge changing changing rate with different Vg

图5 ID-VG转移特性曲线Fig5.the ID-VG transfer characteristics curve

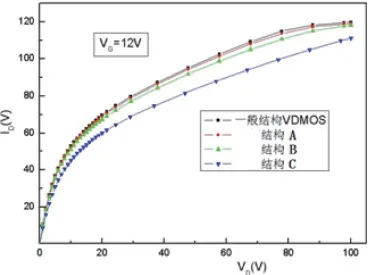

图6 ID-VD转移特性曲线Fig6.the ID-VD transport character-istics curve

3.模拟结果与讨论

为了研究漂移区上方的多晶硅去除的多少对器件的性能有的影响,进行了以下四种结构参数的模拟,条形栅常规VDMOS结构漂移区上方多晶硅的宽度取为10um,按照多晶硅去除的多少分为A、B、C三种情况,其中,结构A去除多晶硅2um,结构B去除多晶硅4um,结构C去除多晶硅6um,去除部分都位于多晶硅的正中央。采用TCAD(ISE)对上述四种结构进行了开启电压、击穿电压、导通电阻、寄生电容、开关时间、栅电荷等参数的详细的对比模拟研究。

VDMOS器件的输入电容Ciss和反馈电容Crss,特别是反馈电容Crss对器件的动态性能影响比较大[6]。图3是VDMOS器件寄生电容随漏电压VD变化情况曲线。由图可见,结构A、B和C能有效减小输入电容和反馈电容,对输出电容改善并不大,这是符合我们预期的结果。

图4是栅电荷随栅压VGS变化情况曲线。栅电荷的值定义为使VGS=12V时所需的电荷值,四种结构的栅电荷分别为3.06216库仑、2.5719库仑、1.94905库仑、1.32614库仑。多晶硅剥离结构能减小栅电荷,其中,结构C的栅电荷Vg比传统结构减小了57%。

表1 优值函数值的比较Table1.comparison between optimization value functions

图5是四种结构的ID-VG转移特性曲线,可以看出四种结构的开启电压曲线完全重合,开启电压相同。因此,结构A、B和C对器件的开启电压没有影响,这是由于所有结构都完整保留了栅材料上方的氧化层的结果。

图6为是四种结构器件的ID-VD转移特性曲线。VDMOS器件通电阻定义为VGS=12V,ID=16A时器件的电压和电流的比值,从图中数据可以计算出四种结构器件的导通电阻,结构A导通电阻比一般结构增大了0.00213欧姆,结构B导通电阻增大了0.00576欧姆,结构C导通电阻增大了0.02601欧姆。导通电阻之所以增大是因为漂移区下积累层面积的减小,减小了积累层面积,电流的导通阻力增大所引起的。

从多晶硅剥离结构的导通电阻和栅电荷的模拟结果来看,该结构从一定程度减小了栅电荷,但却增大了导通电阻,两者是互相矛盾的两个优化参数。在VDMOS转换电路中,降低导通电阻是用来降低导通损耗,降低栅电荷是降低关断损耗,只有全面衡量导通损耗和关断损耗,才能使器件获得最小的功率损耗,为了评价这种优化结果,国际上提出采用优值函数来表征优化的结果。

表1给出了四种结构的优值函数的值,多晶硅剥离结构可以减小VDMOS的功耗优值,其中,结构A功耗优值减小14%,结构B功耗优值减小33%,结构C功耗优值减小46%。因此,从结果可以看出导通损耗和关断损耗的优化函数对于多晶硅的尺寸是非常敏感的,窗口大的结构可以有效减小器件的导通损耗、关断损耗,从而提高器件的动态性能。

4.结论

本文研究了多晶栅部分剥离技术对器件动态特性的改善情况。模拟结果表明,除器件阈值电压参数以外,栅电荷、输入电容、反馈电容、导通电阻、导通损耗和关断损耗的优化函数等参数都依赖于多晶硅剥离窗口的尺寸。其中,栅电荷、输入电容、反馈电容对于晶硅剥离窗口的尺寸是非常敏感的,这对于改善器件的寄生电容,提高器件的动态特性是有利的。尽管采用该技术的器件导通电阻略有增加,会影响器件特性,但好在增加的幅度并不大。在对于器件的导通电阻要求比较严格的设计当中,建议可以采用JFET注入技术来减小导通电阻。因此,在减薄氧化层的厚度,保证总剂量辐照加固的需求的前提下,采用多晶栅部分剥离技术,适当的选取多晶硅窗口尺寸可以降低器件寄生电容,从而改善器件动态性能,对于VDMOS器件在抗辐照领域的实际应用具有一定指导意义的。

[1]MuhammadH Rashid.电力电子学[M].北京:人民邮电出版社,2007,82-149.

[2]Saki T,Murakami N,A new VDMOSFET structure with reduced reverse thsansfer capatance[J].IEEE Trans Elec DEV,1989,36(7):1381-1386.

[3]Raymond J.E.Hueting,Erwin A.Hijzen,Anco Heringa,Adriaan W.ludikhuize,Micha A.A Gate-Drain Charge Analysis for Switching in Power Trench MOSFETs[J].IEEE Trans Electron Devices,NO.8,AUGUST 2004:1323-1330.

[4]Ananda S Roy,Christian C Enz,Jean-Michel Sallese.Source-Drain Partitioning in MOSFET[J].IEEE Trans.on Elec.Dev.,2007,54(6):1384-1393.

[5]MuhammadH Rashid.电力电子学[M].北京:人民邮电出版社,2007,150-152.

[6]Raymond J E Hueting,Erwin A Hijzen,Anco Heringal.A Gate-Drain Charge Analysis for Switching in Power Trench MOSFETs[J].IEEE Trans.on Electron.Devices,2004,51(8):1 323-1330.