嵌入式PLC脉冲信号门槛设定和高速计数的实现

2011-07-03曾晓维高红亮黎立蔡琴

曾晓维 高红亮 黎立 蔡琴

(1湖北师范学院机电与控制科学学院, 武汉 435002; 2湖北师范学院物理与电子科学学院,武汉435002)

1 引言

现代工业中,信号质量关系到设备的实际应用,作为为工业上一种常用到的控制器PLC,同样也面临此问题。专用的信号处理器价格过高,若仅以单片机开发而构成的系统在使用和安装过程中不方便,并且不易于维护,因此,我们采用具有嵌入式操作系统的 PLC来开发信号处理功能。在信号检测和抗干扰等很多实际应用场合,通过对PLC输入信号有效脉冲宽度设定,筛选有效信号,同时还要兼顾系统中对输入信号的高速计数部分,例如在机械位置测量、机械传动控制等方面,要用到高速脉冲计数,把两者结合起来,使PLC功能增强。

2 嵌入式PLC的介绍

嵌入式 PLC是建立在微控制器硬件开发平台和嵌入式操作系统[2]之上,通过开发内核驱动程序与应用程序,将驱动程序添加到嵌入式系统的内核之中,形成嵌入式 PLC系统软件的一部分。用户输入的PLC指令[3](或梯形图转换而成的指令表)所对应的PLC应用程序,经过系统编译程序与内核驱动程序的交互处理,实现对PLC指令表语言程序的解释和执行,实现PLC的控制功能。

作为可二次开发的嵌入式PLC,其硬件功能十分强大,包括为用户提供丰富的扩展接口,并拥有高可靠的数据保持性,以使开发人员能灵活的应用于实际场合。本文所设计的嵌入式PLC是建立在EASY-V1.00[2]操作系统平台之上的,用到的微处理芯片为新华龙公司的C8051F020,它的基本功能包括 CANBUS网络通信、用户应用程序嵌入、梯形图语言处理[6]。

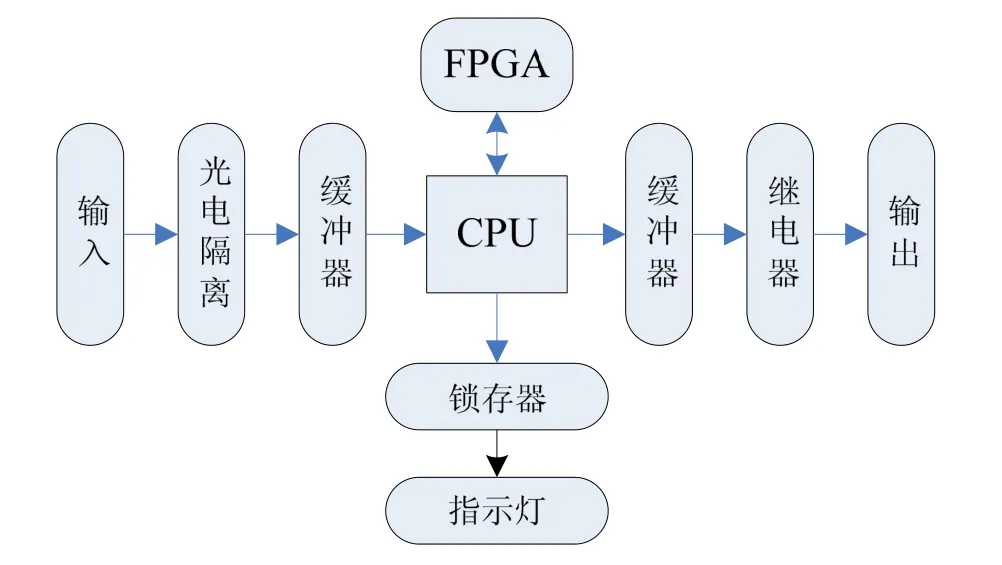

嵌入式PLC系统原理图如1所示,外部输入的开关量经过光电隔离后连接到 FPGA的 I/O口,通过FPGA地址译码,FPGA通过数据地址总线与CPU相连。这样CPU就可以通过数据地址总线获得和设置输入量的工作状态。

图1 嵌入式PLC硬件原理框图

由本思想而写成的代码是嵌入到EASYCORE1.00内核中,通过KELL软件编译而成的二进制文件由 DownHex下载器下载到单片机中,梯形图的编辑、调试与监控由FXGP-WIN-C完成[6]。

3 输入信号脉宽门槛设定的实现

3.1 输入信号脉宽门槛设定分析

输入信号进行脉宽设定主要是为了对输入信号进行滤波。在工业场合,我们希望能够捕获有效信号的同时剔除干扰信号,从而提高系统的安全性。本文设计的脉宽设定可调,即有效信号的脉冲信号可由用户根据实际情况进行调整,满足不同场合的应用。

此嵌入式PLC共有八路输入,系统通过门槛设定的值来确定定时器采样信号的次数,如果在这期间采集的信号相同,则把对应这一路的信号存储到对应输入寄存器RAM_PX中。

3.2 输入信号脉宽设定原理

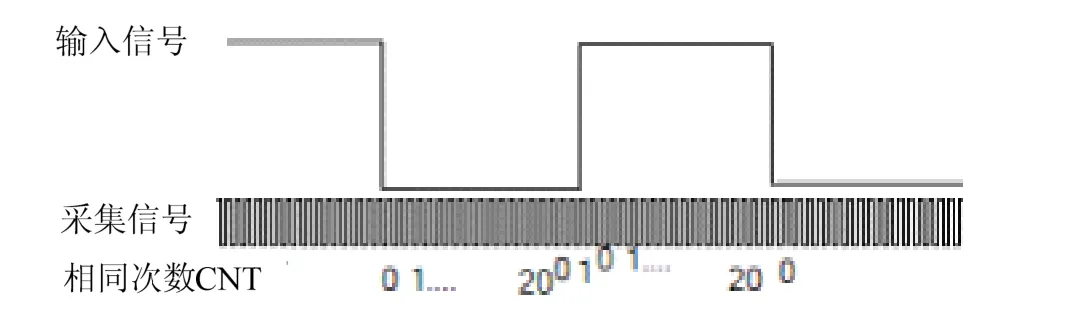

首先用定时器对输入脉冲进行采样,通过采样电平保持的时间来确定输入脉冲信号的宽度。最后通过单片机向 RAM_PX写有效的电平,达到脉冲计数的要求。在程序设计中,设定定时器溢出时间为50 μs,那么对于1 ms的有效脉冲理论上要采集20次,当采集20次的电平一样,则认为脉冲信号有效,输入脉冲采样示意图如图 2所示。

图2 输入脉冲采样

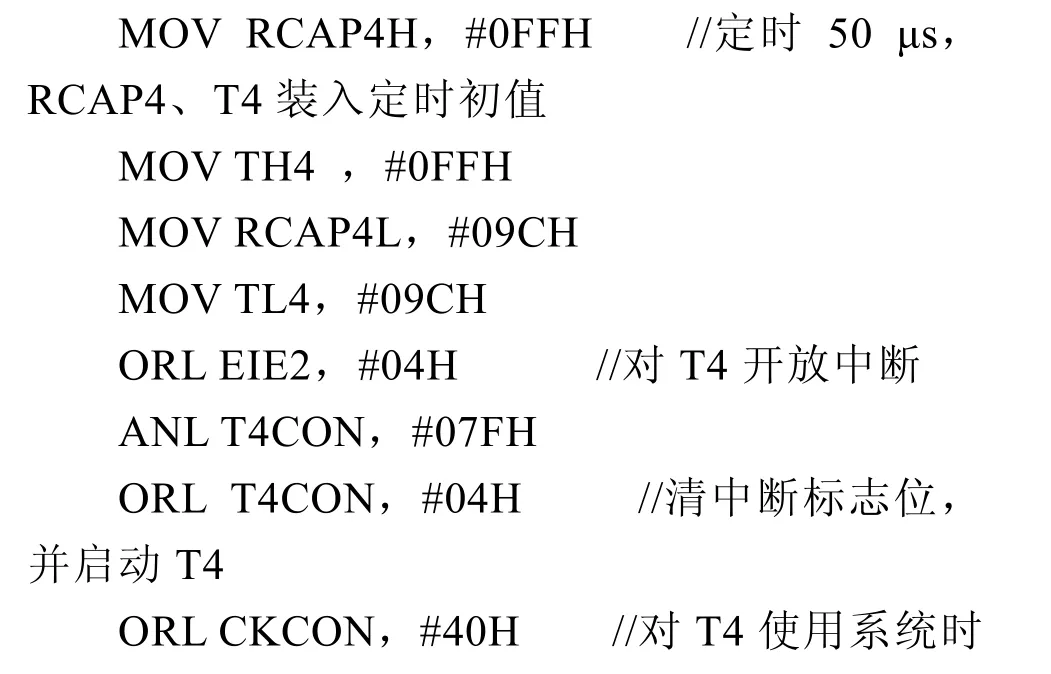

我们对 T4设置为自动重装模式,当定时器溢出时对输入信号进行采样,相邻两次采样的时间间隔称为基准时间,也即是定时的时间长度,为考虑程序有充足的执行时间和便于计算,定位50 μs,系统时钟频率为2 MHz,则T4的定时初值为 65536-50/(1/2)=65436,换成十六进制数为FF9CH,则 RCAP4L=9CH,RCAP4H=FFH。基准时间设定后,采集二十次则为1 ms,因此,只要设定二十一次数据完全相同(共间隔二十个基准时间,前后相比相同次数为十),D5080=20,则有效信号的门槛为1 ms,其他门槛的设定依此类推。

程序中,我们把本次采集到的数据与上次信号作比较,对于每一路信号,若不同,则相同次数CNT置零;若相同则CNT加一,直到满二十次,就把得到相同的信号送给RAM_PX,同时相同次数CNT清零,为下次刷新RAM_PX作好准备。八路数据比较完后,就把本次数据作上次数据,这样就完成了一个周期刷新RAM_PX。

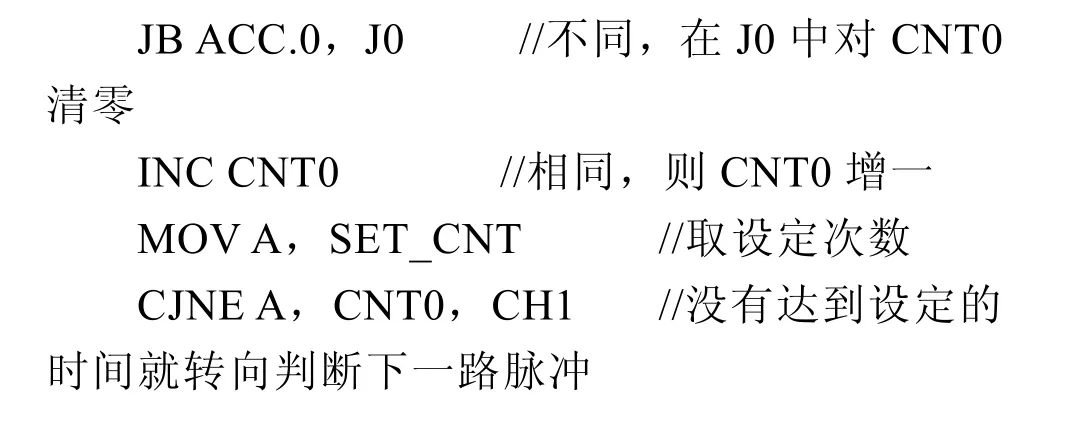

3.3 输入有效信号的采集流程

信号流程如图3所示。

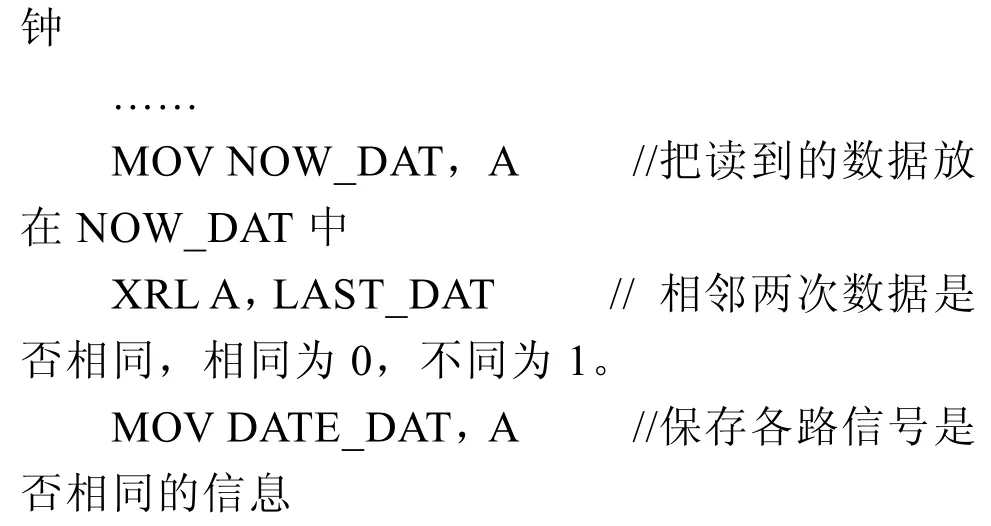

3.4 主要代码分析

嵌入式P L C是基于新华龙公司的C8051F020芯片开发的,我们选用51汇编语言编程。编译器选择KELL C51,由它生成需要的.HEX文件。

图3 输入有效信号采集

4 高速脉冲A、B相计数的实现

4.1 计数原理

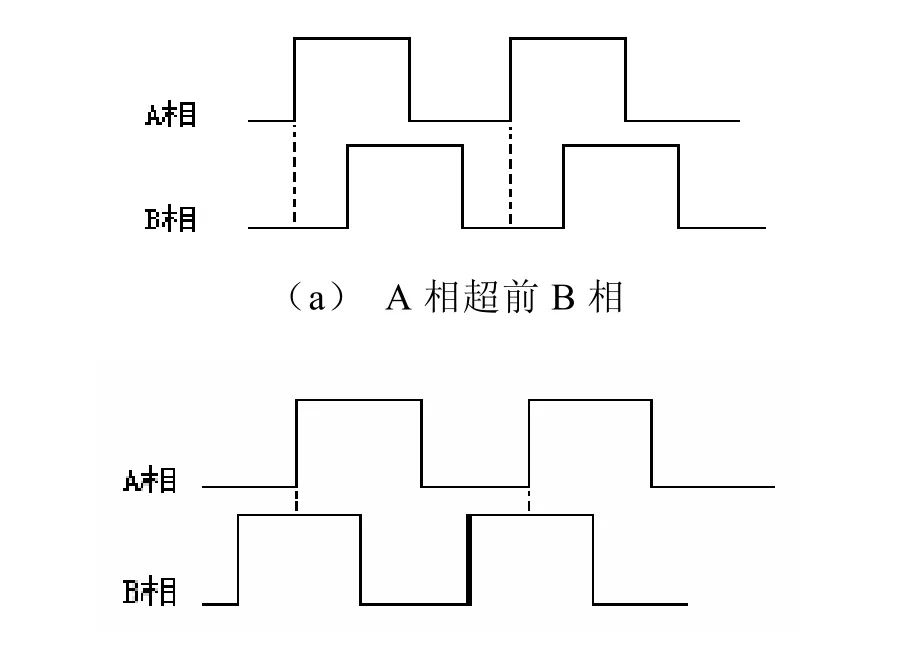

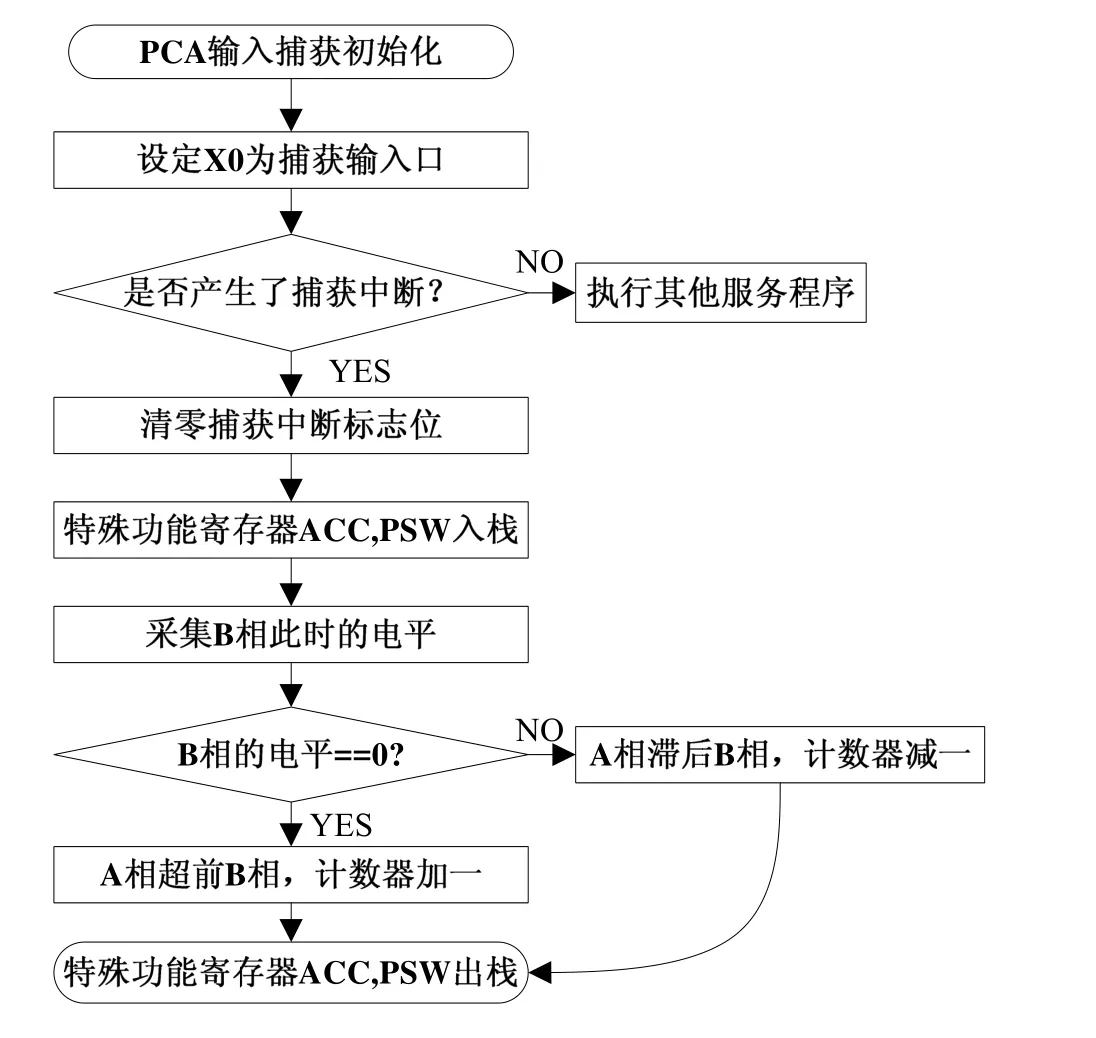

高速脉冲计数是利用中断方式完成的,这里使用C8051F020芯片的PCA0中断,根据外部信号的输入方式,本高速脉冲计数有三种计数方式。单独接A相脉冲,B相接高电平,此时AB逻辑信号01,为则为增计数;单独接B相,A相接高电平,AB逻辑信号为10,则为减计数;若同时接A、B相,A超前B 0 ~90度时为增计数,A滞后B 0~90度时为减计数,A、B分别对应于X0、X1输入端口。计数值存放在D5085、D5086中,D5085为低十六位,D5086为高十六位。

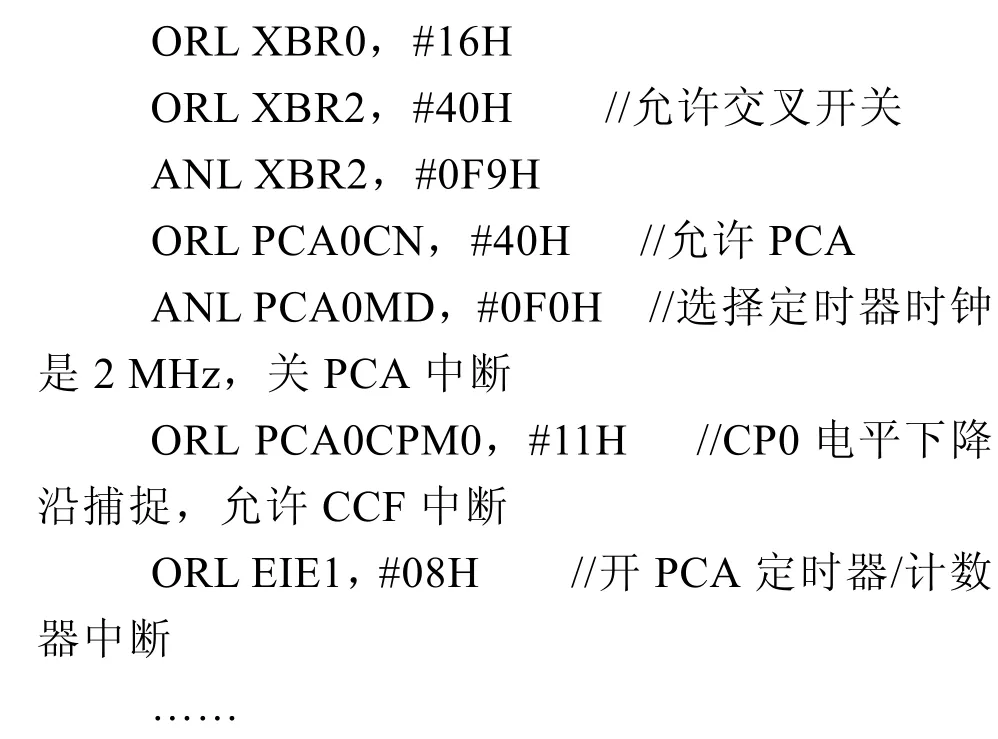

我们把 PCA0设置成下降沿捕捉模式,把CEX0、CEX1分别配置到X0、X1端口,单相计数占用一个外输入端口(X0或X1),而双相计数占用两个端口(X0和X1)。单相计数时,外部高速脉冲的下降沿触发PCA0中断,进入中断后立即读取另一通道的电平信号,若AB信号为01,则向上计数,计数值加一;若AB信号为10,则向下计数,计数值减一。双相计数时,首先要判断相位的超前与滞后,这两路信号的下降沿均能触发PCA0中断,但只要判断AB相相位差形成的特定逻辑关系,就能判断出A超前还是滞后于B。进入中断后,若AB逻辑关系为01,A超前B,向上计数加一;若AB逻辑关系为10,B超前A,向下计数减一,如图4所示。

AB相计数功能的实现如图5所示。

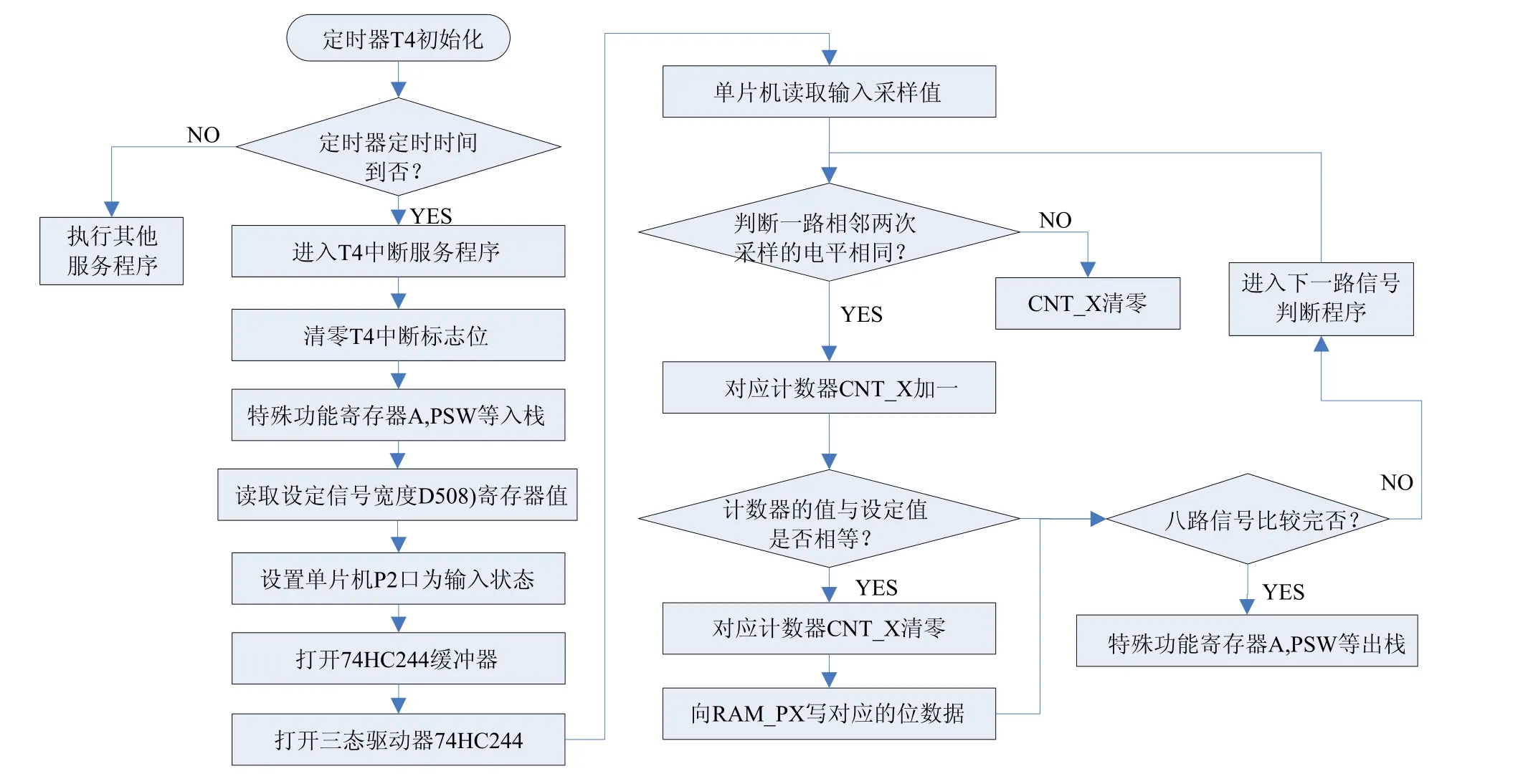

4.2 AB相脉冲高速计数主要代码分析

设计这段程序首先需要先配置交叉开关,然后再对PCA0的各模块进行设置,最后在PCAO中断中设计加、减计数。

在KELL C51中编译嵌入程序,使用科威公司提供的专用下载工具 DownHex.exe把生成的16进制文件通过串口URTA0下载到系统中,是的系统内核可以调用它,从而完成了二次驱动程序的开发[6]。

图4 (b)A相滞后B相

5 结束语

本次设计采用汇编语言编写,程序执行效率高。经过测试,通过设定脉冲宽度能够起到很好的滤波效果,门槛的分辨率为200 μs,而高速相位差计数的误差相隔±1个脉冲。基于嵌入式PLC的对输入信号脉宽门槛限定和高速相位差计数在工业现场中应用十分广泛,可在此基础上继续开发其他功能,不影响梯形图语言功能和CANBUS互联特性,事实上,只需要更多的关注硬件接口的可靠性及软件的时效性,而将工艺交给梯形图,有效地降低了开发难度和开发成本。

图5 功能四实现流程图

[1]童长飞. C8051F系列单片机开发与C语言编程[M].北京: 北京航天航空大学出版社, 2005.

[2]龚云生. EASY -V1.00嵌入式PLC的基本原理[C].黄石科威自控有限公司, 2006.

[3]王永华. 现代电气控制及PLC应用技术[M](第二版).北京: 北京航天航空大学出版社, 2008..

[4]潘琢金. C8051f020/1/2/3混合信号ISP FLASH微控制器数据手册[M]. 沈阳: 沈阳航空工业学院, 2002.

[5]向前进, 周纯洁, 龚云生. 嵌入式 PLC的高速脉冲计数开发[J]. 计算技术与自动化, 2006,25(4):47-50.

[6]嵌入式PLC原理与应用[S]. 黄石科威自控有限公司,2004.

[7]杨惠灵. 嵌入式数控系统中 PLC模块的开发[J]. 机电技术, 2009(2):1-3.

[8]柴瑞娟, 陈海霞. 西门子 PLC编程技术及工程应用[M]. 北京: 机械工业出版社, 2006.