基于FPGA的UART设计

2011-05-12王志学

王志学

(广东轻工职业技术学院,广东 广州 510000)

UART(Universal Asynchronous Receiver/Transmitter,通用异步收/发器),用于控制计算机与串行设备之间的数据通信,它提供了外设用到的RS-232C数据终端设备接口,使计算机可以和调制解调器或其它使用RS-232C接口的串行设备进行通信。常见的UART有8250、8251、NS16450、NS16550等,这些芯片做的比较复杂,功能齐全。但是由于结构和功能相对固定,因而不能根据我们的实际需要去裁剪和移植。当我们不需要用到完整的UART功能和一些辅助功能时,就可以将需要的UART功能集成到FPGA上,从而大大的减少了体积、简化了电路,也提高了系统的可靠性、稳定性和灵活性。

1 UART简介

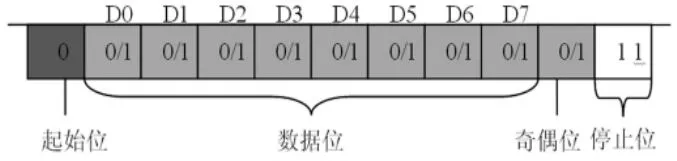

UART是一种串行数据总线,用于异步通信,并且双向通信,可实现全双工传输和接收。基本的UART只需要两条信号线(TXD、RXD)和一条地线就可以完成数据的相互通信,接收和发送互不干扰,这样就大大节省了传输费用。由于UART是异步通信,所以需要对数据进行同步。基本的UART帧格式如图1所示:

图1 UART帧格式

从图中可以看出,串行异步通信的帧格式包括四个部分:起始位、数据位、校验位和停止位。起始位在一个字符中占一位,并且必须为0,表示字符的开始;起始位后面是数据位,一般为5至8位,由串行通信的初始化程序设定,数据的排列方式是低位在前,高位在后。数据位后面是校验位,该位可根据实际需要可选可不选;一个字符的最后是停止位,该位必须存在,表示一个字符的结束。停止位可以是1位、1.5位或2位。异步通信的这种由起始位开始,停止位结束所构成的一串二进制数即为帧,从微观来看,异步通信时一位一位的传输的,从宏观来看,又是一帧一帧传输的。在一帧数据中的每一位之间的时间间隔是一样的,但是帧与帧之间的时间间隔是随机的。

2 UART的模块设计

本文采用模块设计的方法,并且针对实际要求,将整个软件划分为波特率发生器模块、接收启动模块、接收模块和发送模块四个部分。各模块功能分析如下:

2.1 波特率发生器模块

波特率发生器实际上就是一个简单的分频器,它的功能是产生和RS-232C通信所采用的波特率同步的时钟,这样才能按照RS-232C的时序要求进行数据的收发。而波特率发生器的系数在FPGA实现时一般是固定的,但对于不同的实现,这个系数需要更改(因为FPGA在设计时比较容易改动,而专用芯片不易改动,所以UART专用芯片一般通过添加一个接口以便在使用时改变波特率)。可以在VHDL语言中使用Generic语句,或在Verilog HDL语言中使用parameter语句使问题得到解决。因发送和接收时对时钟的要求不同,给发送模块和接收模块提供的时钟频率也不相同。当发送数据时,只需要将数据按照一定的速率串行的输出就可以了,所以,发送的时钟和发送的波特率是一致的;但是,在接收数据时,在数据位的什么位置对数据信息进行判断非常的重要,最理想的情况就是在串行数据每一位的中点对数据进行采样,因为发送方和接收方的时钟是不一致的,所以需要对每一位数据的时间进行分段,分段越多,采样时就越接近中点,并且采样时出现错误的概率也越低,但是,分段越多,采样的时间也越多,系统的开销越大,所以,实际设计时,波特率发生器产生的分频时钟,是波特率时钟频率的16倍。波特率发生器模块如图2所示。clk16x是波特率发生器得到的分频时钟;clk是时钟输入信号;rst是系统复位信号。

图2 波特率发生器模块示意图

2.2 接收启动模块

由于串行数据帧和接收时钟是异步的,由高电平转化为低电平可以视为一个数据帧的起始位。但是,在实际的电路中,会有多方面的原因干扰,为了避免毛刺影响,正确的判断起始位的到来,采样时在时钟的上升沿(即由波特率发生器提供的16倍于波特率的时钟)检验数据是否为低电平,如果接收到的是低电平,则开始计数,如果连续8个时钟内都是低电平,则表示起始信号有效,即要求接收到的起始位在波特率时钟采样过程中有一半是属于逻辑0才表示接收到的起始位有效。如果在采样时,有一次检验到高电平,即逻辑1时,则认为起始信号无效,返回初始的状态重新等待下一个起始位信号。当起始位的信号时有效时,每隔16个时钟采样一次,这样就保证了每次采样都是在数据位的中点。

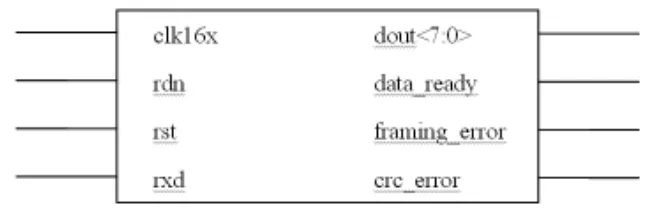

2.3 接收模块

接收模块如图3所示。clk16x是由波特率发生器产生的分频时钟;rst是系统复位信号;rxd是来自其他设备的串行数据;data_ready表示"数据已准备好",在rdn为1的情况下,并行数据转换完毕就可以输出,此时将data_ready置为0;在rdn不为1的情况下,串并转换完成后将此data_ready置1以表示数据己经转换完毕,可以输出了,通知接收模块每隔16个clk16x周期采样一次,接收UART帧中剩余的数据位,否则,接收模块不工作。dout<7:0>是接收模块将接收到的串行数据转换成的并行数据,送给发送模块的输入信号din<7:0>。

图3 接收模块示意图

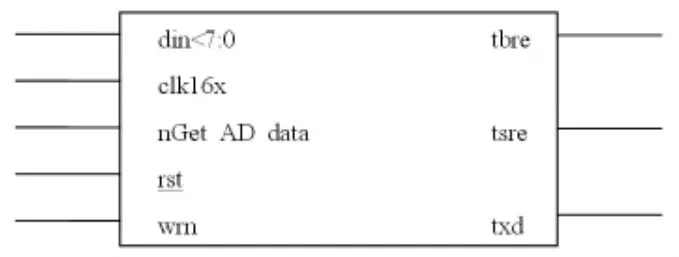

2.4 发送模块

发送模块相对于接收模块要容易处理得多。只要每隔16个clk16x周期输出1位即可,次序遵循1位起始位,8位数据位,1位停止位。发送模块如图4所示。din<7:0>是将要发送出去的并行数据;clk16x、rst信号同接收模块;wrn是数据发送的启动信号;txd是发送出去的串行数据信号。

图4 发送模块示意图

结语

用FPGA实现UART功能,减少了系统的面积,降低了系统的功耗,提高了系统的稳定性,同时,由于数据帧和波特率都比较容易改变,大大的提高了系统设计的灵活性和可移植性。

[1]史故臣,石旭刚,左绪勇.基于FPGA的UART设计与实现[J].中国新通信,2009.4:62-64

[2]聂涛,许世宏.基于 FPGA 的 UART 设计[J].现代电子技术,2006,29(2):127-129

[3]播松,黄继业.EDA 技术与 VHDL[M]北京:清华大学出版社,2007

[4]杨宗国,李艳萍.基于FPGA的UART模块的设计[J].现代电子技术,2009,2:19-22

[5]黄智伟,王彦.FPGA系统设计与实践[M].北京:电子工业出版社,2005

[6]潘松,王国栋.VHDL使用教程.电子科技大学出版社.1999