微波着陆系统信号模拟器设计

2011-03-21王伟,张斌

王 伟,张 斌

(空军工程大学电讯工程学院,西安 710077)

1 引 言

目前,微波着陆系统(MLS)在我军装备的进近引导系统中是最先进的精密引导系统[1]。系统除了能提供完整的方位、仰角和距离引导信息外,还具有完善的监测能力[2],对设备发射的各种信号进行监测,实现设备的工作控制、状态显示,建立遥控和同步通信等,当系统发生故障、监测参数超过误差范围时,能及时予以警示,并自动切换主备用设备或关闭发射信号,保证系统的可靠性和完好性[3,4]。因此,研制微波着陆信号模拟器来提供各种监测信号对系统的性能测试、指标校准和故障维修有着十分重要的意义。国外对该模拟器的研究比较成熟,已经有型号产品提供,例如美国IFR公司的MLS-800,但价格昂贵。

本文提出了一种简易微波着陆系统信号模拟方法,通过采用高速、高性能的FPGA,在设备时钟的同步下按一定规律读取存储器中的信号数据,模拟产生不同场景下的微波着陆系统方位信号、仰角信号和数据字信号。该模拟器成本低、体积小,可脱机对系统进行独立调试和指标校准,保证系统的可靠性和完好性。

2 MLS信号格式

MLS地面台角度信号和数据信息的发射采用了时分多路复用(TDM)技术[2,3],即角度制导信息和数据字都在同一频率上发射,不同功能的信号都占有自己的发射时隙,在每一个功能发射时隙前部用功能码来区分不同的功能块。

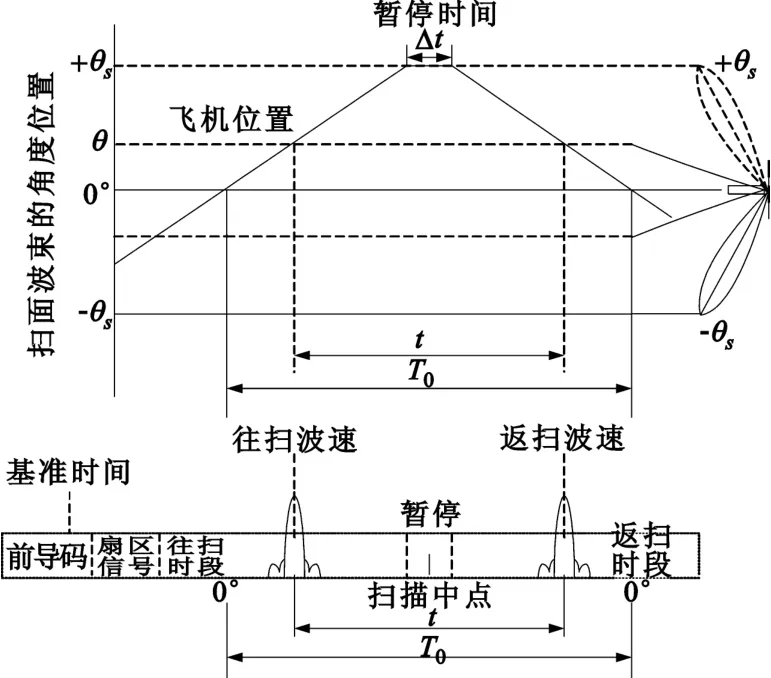

MLS的测角是基于时基扫描波束(TRSB)技术。在比例制导区内,飞机接收地面角度引导设备扫描天线发射的“往”扫脉冲与“返”扫脉冲,测出这两个波束之间的时间差,通过计算得到它所处的位置相对于跑道中心线的方位角[5],如图1所示。

图1 微波着陆系统角度测量示意图Fig.1 Sketch map of the MLS angle measurement

制导角度值与脉冲间隔时间差之间的关系为[5]

式中,θ为方位制导角度值,t为任意进近角时飞机接收到“往”和“返”脉冲间的时间差,T0为以零度角进近时飞机接收到“往”和“返”脉冲间的时间差,v为扫描速率。

角度引导信号包含了前导码、扇区信号、“往”扫描区间、扫描间隙和“返”扫描区间等要素,这些要素都是按照严格的时间要求发射的。

数据字信号采用DPSK调制方式,调制速率为15625 bit/s,其结构和时序有着严格的规定。

3 系统结构

模拟器的主要功能是复现微波着陆系统方位引导信号、仰角引导信号和数据字信号。该模拟器主要由波形存储电路、FPGA及其附属电路、波形形成电路、信号分离电路组成,如图2所示。

图2 总体组成框图Fig.2 Block diagram of simulator

根据MLS信号格式,FPGA及其附属电路读取波形存储器中的数据信息,处理后进行数模转换,同时形成各功能信号的同步信号,在各同步信号的控制下,产生满足指标要求的方位信号、仰角信号、数据字信号,同步信号和各功能信号分别用来控制发射机和检验监测器。

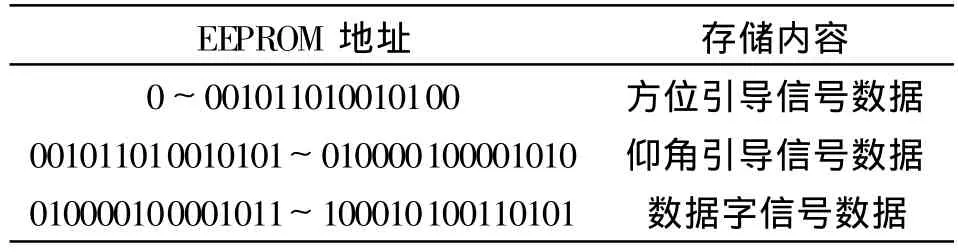

波形存储器为电可擦除存储器,存储了形成方位引导信号、仰角引导信号、数据字信号的包络数据信息,存储区分配如表1所示。

表1 EEPROM存储区分配Table 1 Distribution of EEPR OM

FPGA及其附属电路是模拟器的核心部分,选用Alter公司的EPF10K20TC144-4作为主控芯片,它采用FLEX结构,具有63000个系统门、144个逻辑阵列块、1152个逻辑单元、12288位 RAM、102个 I/O。该款FPGA的内部资源以及管脚数量能够完全满足本方案的设计需求,故选用该款FPGA作为主控逻辑芯片。FPGA的配置数据存储在片外的EPC2LC20中。配置数据是用Quartus软件将设计所得的pof格式的文件烧录进去。这样设计程序就固化在外部配置芯片EPC2LC20里,在上电时,FPGA把设计程序从EPC2读入SRAM并运行[6,7]。

FPGA及其附属电路主要完成两个功能:一是产生波形存储器读逻辑控制信号和地址信号,分别通过控制总线和地址总线送入波形存储器,调用存储的数据信息;二是产生各功能信号的同步信号,送入信号分离电路。

波形形成电路完成数字量到模拟量的转换。采用8位数模转换芯片AD7528KR外接运算放大器TL082完成波形形成,且输出视频信号幅度和直流电压的大小是可调的。将信号分成三路送入信号分离电路,每一路中都含有方位引导信号、仰角引导信号和数据字信号。

信号分离电路中,在同步信号的控制下,每一路只允许一种功能信号输出。

4 系统工作流程

根据微波着陆系统的信号格式,在计算机上应用MATLAB软件建立矩阵函数,根据需要灵活地改变波形参数,产生正常或异常的信号波形,将波形数据下载到存储器中[8,9],对存储的数据按照功能设置各自的时隙分配标志;搭建以FPGA为核心的硬件电路,用VHDL语言编写软件,在程序控制下,通过标志进行识别,调用存储的数据,按照规定的格式依次产生所需信号,从而实现模拟器的功能。

4.1 波形数据产生

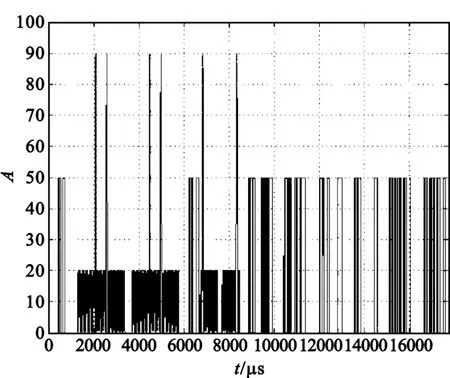

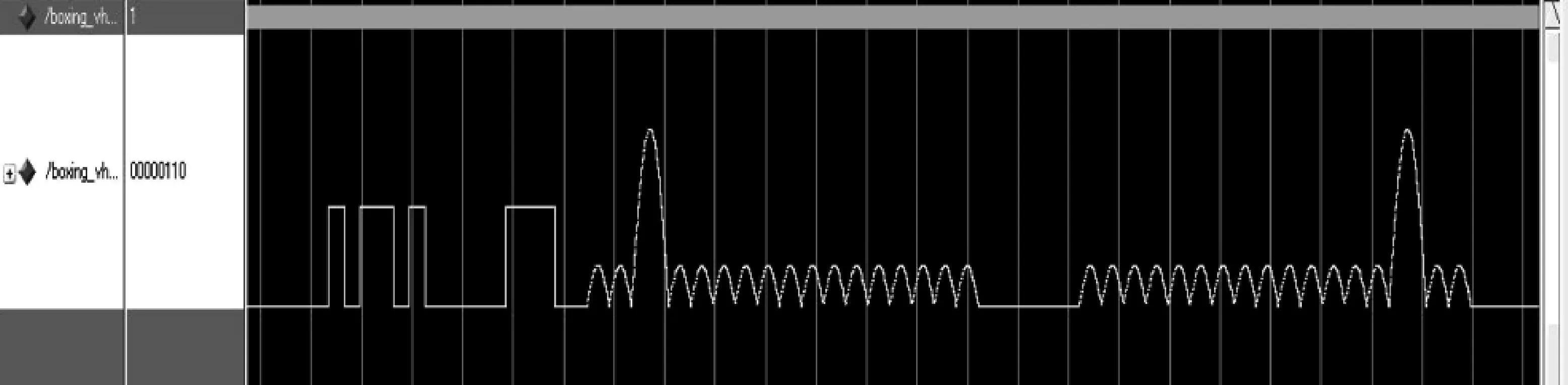

以500kHz的采样频率依次对理想的±10°高速方位信号、3.5°仰角信号和数据字信号进行采样,信号波形如图3所示。将波形数据下载到波形存储器中。

图3 信号数据信息仿真波形图Fig.3 Simulation of the signal data message

4.2 信号输出

该过程主要包括存储器数据读取和信号输出时序控制,其完成的具体操作包括时隙分配标志识别、地址信号产生、数据信息读取、D/A数据分配、DPSK信号形成等。

当模拟器正常工作时,根据方位信号、仰角信号和数据字信号产生的先后顺序,产生相应的时隙分配表,然后对时隙分配标志进行识别,主要分为3种情况。

(1)若为方位(或仰角)信号标志,则产生方位(或仰角)信号的地址信号,调用存储的信号数据,根据微波着陆系统的信号格式,在相应时隙内产生DPSK信号,输出D/A分配数据。另外,根据系统设计要求:在整个方位(或仰角)引导功能时隙,产生方位(或仰角)同步信号。

(2)若为数据字信号标志,则产生数据字信号的地址信号,在相应时隙内产生DPSK信号及其同步信号。

(3)若为延时标志,则做相应延时后返回时隙分配信息表。

主程序流程图如图4所示,在Modelsim软件中的部分仿真结果如图5所示。

图4 主程序流程图Fig.4 Flow chart of main program

图5 仰角信号仿真波形Fig.5 Simulation of the elevation signal

5 信号分析

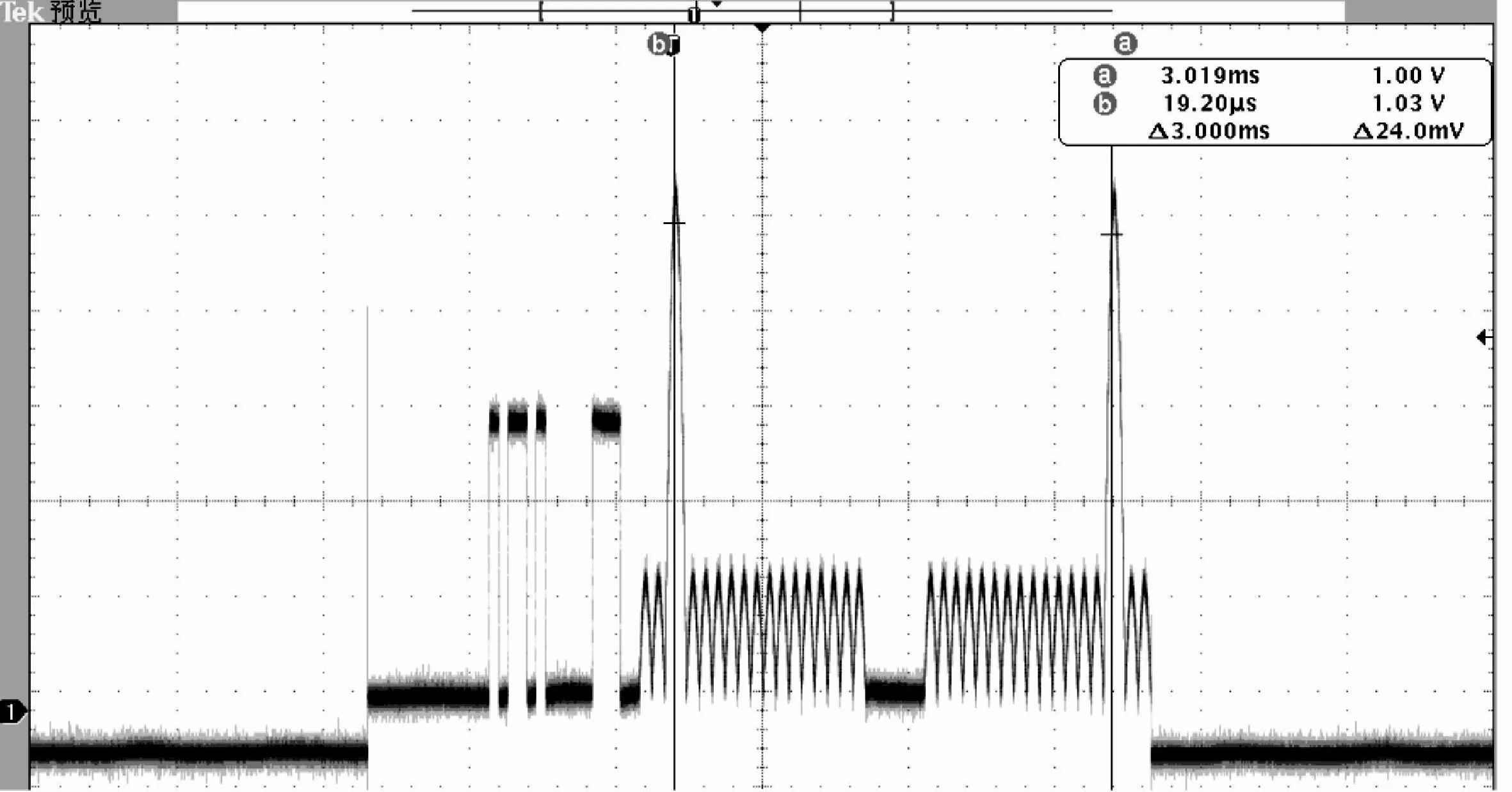

以仰角信号为例,用标准+15 V、-15 V和+5 V直流电源给信号模拟器供电,通过示波器对相应功能管脚进行测量,得到的仰角信号波形如图6所示。

图6 实测仰角信号波形Fig.6 The measured elevation signal

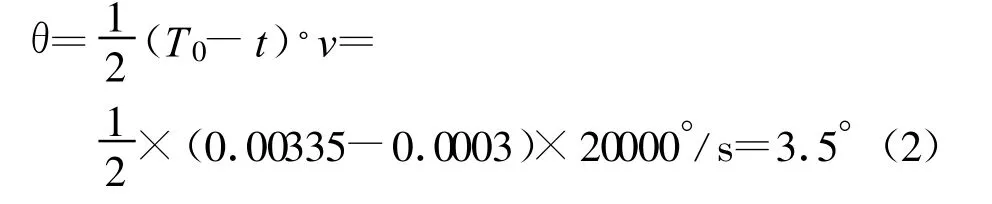

根据MLS信号格式,仰角信号以零度角进近时飞机接收到“往”和“返”脉冲间的时间差 T0为3.35ms,扫描速率为20000°/s,已知存储器中仰角信号为3.5°,由示波器测出“往”和“返”脉冲间的时间差为3ms,计算仰角信号角度:

可以看出,实测值与理论值完全相符。另外,从图中可以看出,前导码和扇区信号的实测值与理论值是一致的,主瓣和旁瓣的幅度满足指标要求,系统整体达到了设计要求。

6 结束语

针对微波着陆系统测试、调试、校准困难等难题,本文设计了一种基于FPGA的信号模拟器,通过实际电路验证,该模拟器能够实时高精度地模拟微波着陆系统的各种信号,且结构简单,易于生产,实现成本较低。目前,该模拟器已经投入使用,使用结果表明,系统性能稳定,满足实际需要。

以此电路为基础,通过灵活改变存储器中的信号数据和控制软件,该模拟器可广泛应用于多种设备调试和各类测试仪器,具有广阔的应用前景。

[1] 弋沛琦,高瑞乾,刘石源.飞机着陆系统的现状与发展[J].海军航空工程学院学报.2005,20(4):461-464.GE Pei-qi,GAO Rui-qian,LIU Shi-yuan.Present and Development of the Plane Landing System[J].Journal of Naval Aeronautical Engineering Institute,2005,20(4):461-464.(in Chinese)

[2] 周其焕,魏雄志,崔红跃.微波着陆系统[M].北京:国防工业出版社,1992.ZHOU Qi-huan,WEI Xiong-zhi,CUI Hong-yue.Microwave landing system[M].Beijing:National Defense Industry Press,1992.(in Chinese)

[3] 张忠兴,李晓明,张景伟.无线电导航理论与技术[M].西安:陕西科学技术出版社,1998.ZHANG Zhong-xing,LI Xiao-ming,ZHANG Jing-wei.Radio Navigation Theory and Technology[M].Xi′an:Shaanxi Science and Technology Press,1998.(in Chinese)

[4] Arnold R.MLS:Keeping Pace with the Future[J].IEEE Aerospace and Electronic Systems Magazine,1990,5(5):23-26.

[5] GB2598-1996,微波着陆系统机载设备通用规范[S].GB2598-1996,MLS Equipment General Criterion[S].(in Chinese)

[6] 罗朝霞,高书莉.CPLD/FPGA设计及应用[M].北京:人民邮电出版社,2007.LUO Zhao-xia,GAO Shu-li.Design and Application of CPLD/FPGA[M].Beijing:People′s Posts&Telecommunications Press,2007.(in Chinese)

[7] 周润景,图雅,张丽敏.基于QuartusII的 CPLD/FPGA数字系统设计实例[M].北京:电子工业出版社,2008.ZHOU Run-jing,TU Ya,ZHANG Li-min.Design Examples of CPLD/FPGA Digital System Based on QuartusII[M].Beijing:Publishing House of Electronic Industry,2008.(in Chinese)

[8] 蔡琳洁,单涛,陶然.多功能雷达视频模拟器的研制[J].系统工程与电子技术,2002,24(10):19-20.CAI Lin-jie,SHAN Tao,TAO Ran.Design of aMultifunction Radar Video Signal Simulator[J].Systems Engineering and Electronics,2002,24(10):19-20.(in Chinese)

[9] 朱灿焰,龙腾,何佩琨.雷达中频视频信号模拟的一种实现方法及研究[J].系统工程与电子技术,1999,21(11):34-37.ZHU Can-yan,LONG Teng,HE Pei-kun.Realization and Research of Radar Intermediate Frequency Video Signal Simulator[J].Systems Engineering and Electronics,1999,21(11):34-37.(in Chinese)