一种采用FPGA设计的SDRAM控制器

2011-01-18卢安军王信杰谭大祝

黄 勇,卢安军,王信杰,谭大祝

(湖北民族学院 信息工程学院,湖北 恩施 445000)

随着大规模集成电路的发展,FPGA芯片的性能得到了极大的提高,使得以FPGA来构建一个片上系统成为一种比较好的选择.在完成这样一个系统开发中,常常需要用到存储容量大、速度快的存储器,由于SDRAM的价格低、速度快、存储容量大,从而成为比较理想的器件.但SDRAM存储器存在控制逻辑复杂、接口方式与普通的存储器有较大差异的问题[1-2],因此需要设计专门的SDRAM控制器.本文提出了一种基于Xilinx公司Spartan-3系列的FPGA芯片K4S643232H的SDRAM控制器设计方案.

1 SDRAM简介

本文采用三星的K4S643232H[3]型号SDRAM进行测试和仿真、调试.K4S643232H是容量为2Mbyte的动态同步RAM,由位宽为32的4×512 Kbyte字节组成.其中列地址7位,块地址2位,行地址11位,控制命令采用标准的SDRAM控制命令.

SDRAM的控制命令主要包括:模式寄存器设置命令、激活命令、预充命令、读命令、写命令、带预充的读命令、带预充的写命令、自动刷新命令、自我刷新命令、突发停命令、空操作命令.SDRAM器件的管脚分为控制信号、地址和数据三类.控制信号传递读写控制信息,地址和数据线分别传输读写地址和数据信号.所有的信号同步于SDRAM的控制时钟,从而实现了数据的同步传递.

因为SDRAM的结构原因,每间隔一定的时间就必须对整个存储空间进行一次刷新,以保持存储的数据.此外,SDRAM寻址采用行激活的方式,首先在控制命令的指导下激活相应的行,然后传递列地址,在操作完成以后还要关闭相应的行.

根据输入命令,SDRAM状态在内部状态间转移.内部状态包括模式寄存器设置状态、激活状态、预充状态、写状态、读状态、预充读状态、预充写状态、自动刷新状态及自我刷新状态.

2 硬件设计

2.1 控制器整体结构

为了提高控制的效率,本控制器采用简洁的接口时序、状态机.控制读写外部接口仅仅包括write_req、write_en、read_req、read_en以及地址信号、数据信号、控制信号[4].当外部需要写入数据时,即将write_req拉高,SDRAM控制器调整状态机进入写状态,并将write_en拉高,外部检测到write_en为高即传递需要写的地址和数据.同理,完成读操作.为了防止读写操作的冲突,可以对读写操作设置优先级.如果写优先,当write_req、read_req同时为高电平,首先进行写操作,只有当write_req为低、read_req为低时才进行读操作.

因为SDARM控制器不能自由的换行换块,在换行读写、换块读写之前必须对新的行或者块进行激活.如果让外部模块调整不同行、块地址之间的间隔,会使控制显得复杂繁琐,为此在SDRAM控制器中加入了特有的地址检测模块.

当地址检测模块检测到读写地址换行或者换块时,会通知状态机停止当前的读写操作,关闭当前的行或者块,然后激活新的行或者块.然后进入读写操作.

对于外部模块,SDRAM控制器的上述操作是屏蔽的,外部模块只需要关心write_en,read_en即可.整体的接口图如图1所示.

参照通用的SDRAM控制器,将SDRAM分为时序状态机、数据通道、地址通道、控制命令、接口电路等几个部分.以状态机为核心,其他模块依照不同的状态产生相应的操作,构建SDRAM的模块,各个模块之间的接口如图2所示.

图1 整体接口图 图2 SDRAM的模块结构图Fig.1 The overall interface diagram Fig.2 SDRAM module structure diagram

2.2 控制器的模块

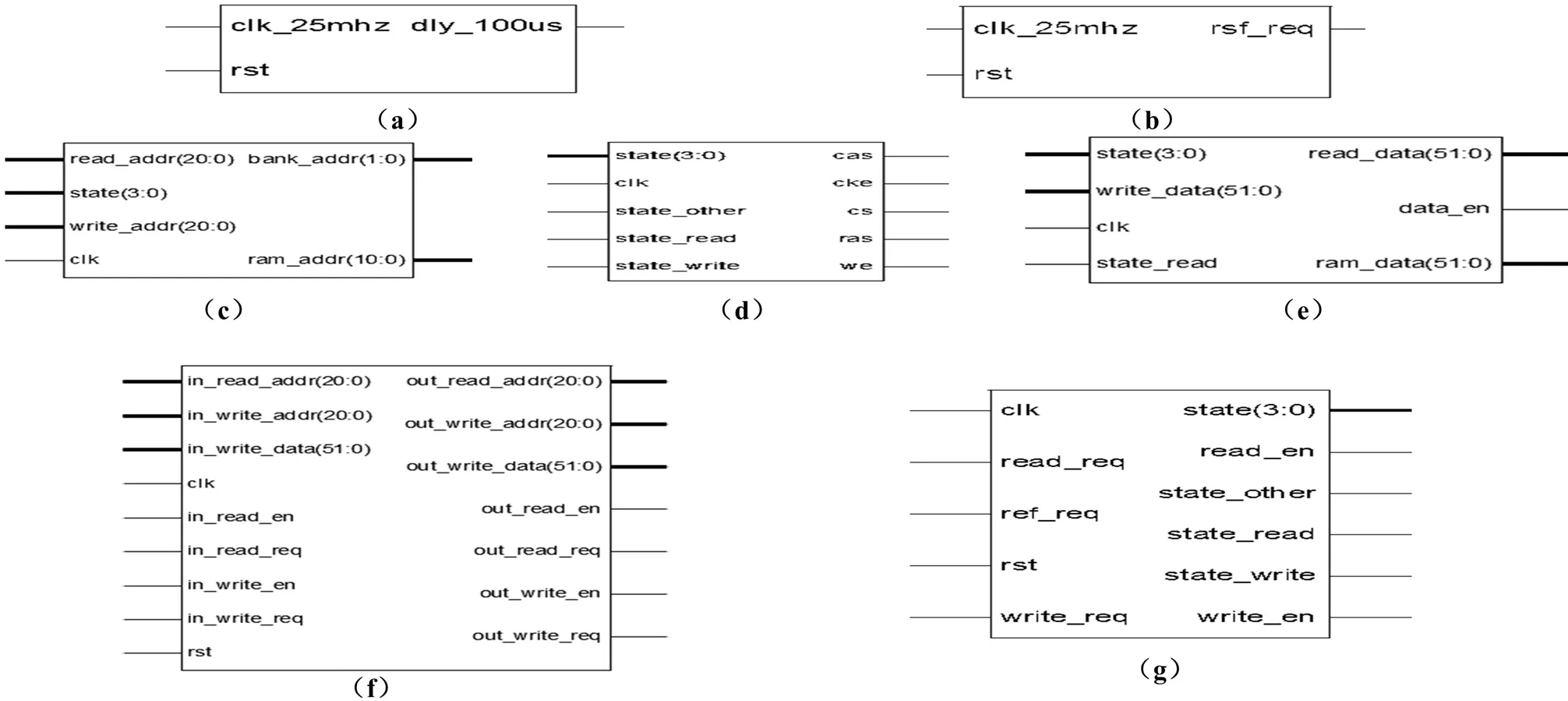

SDRAM控制器由七个模块构成[5-6],分别包括100 us的延时模块delay_100 us、刷新模块ref_req、地址控制模addr_channel、命令控制模块command_output、读写数据控制模块data_channel、状态机模块state_machine、接口模块.如图3所示.

100 us的延时模块delay_100 us完成正常工作之前的100 us的延时操作,初始状态的dly_100 us信号线为低电平,100 us后置高电平完成100 us的延时.接口模块如图3(a)所示.

刷新模块ref_req为状态机提供必要的刷新信号,每个65ms/4096的时间单位,rsf_req信号线置高电平,状态机检测到这个高电平后进入刷新操作状态,完成刷新操作.刷新模块如图3(b)所示.

地址控制模块addr_channel是SDRAM控制器与SDRAM进行地址传递的通道,读状态输出读地址,写状态输出写地址,地址控制模块如图3(c)所示.

命令控制模块command_output是SDRAM控制器的命令输出接口,按照不同的状态,该模块输出相应的控制命令,控制SDRAM完成不同的操作,命令控制模块如图3(d)所示.

读写数据控制模块data_channel是SDRAM控制器与SDRAM进行数据交换的通道,ram_data为输入输出端口,写状态时向SDRAM输出数据,读状态时从SDRAM中读取数据,读写数据控制模块如图3(e)所示.

状态机模块state_machine控制SDRAM工作的状态,是SDRAM控制器的核心,其他各个模块按照状态机模块state_machine提供的状态工作,状态模块如图3(f)所示.

接口模块是SDRAM控制与外部进行通讯的接口,该模块将外部的请求和使能信号转化为SDRAM可执行的操作信号,从而实现SDRAM控制器与外部的信息交流,接口模块如图3(g)所示.

(a)100 us的延时模块;(b)刷新模块;(c)地址控制模块;(d)命令控制模块;(e)读写数据控制模块;(f)状态机模块;(g)接口模块 图3 SDRAM控制器各模块结构图Fig.3 SDRAM controller every module structure diagram

3 软件设计

3.1 控制器的工作状态机

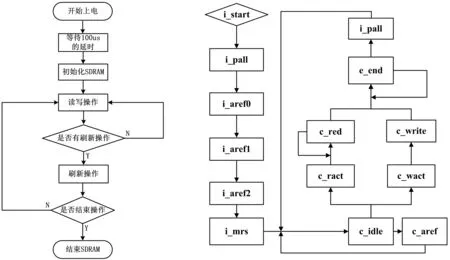

控制器的状态机包括:初始化状态机、工作状态机[7].初始化状态机由i_start、i_pall、i_aref0、i_aref1、i_aref2、i_mrs组成,分别完成延时、预充电、刷新、模式寄存器编辑操作.工作状态机由c_aref、c_end、c_pall、c_idle、c_ract、c_read、c_wact、c_write组成,分别完成自我刷新、预充电、激活、读、写操作,其中c_end、c_idle是用来调整时序的中间状态.

SDRAM在启动之前存在100 us的等待时间,以保持电压的稳定.当电压稳定以后进入初始化状态机,初始化包括预充电和若干次的刷新、模式寄存器的设置.整个工作流程如图4所示.

SDRAM初始化完成以后即进入空闲状态,等待外部的写请求或者读请求、刷新请求.其中刷新请求的优先级最高,写请求次之,读请求最后.当然,各种请求的优先级可以按照要求灵活的改变.整个工作的时序状态机如图5所示.

图4 工作流程图 图5 SDRAM控制器状态机 Fig.4 Work flowchart Fig.5 SDRAM controller state machine

每次完成读写操作之后,SDRAM自动进入预充电状态,关闭当前的行或者块,再次进入空闲状态,等待下一次请求的到来.

3.2 各模块的控制机

3.2.1 数据通道模块 当状态机进入c_write状态时,输入输出的端口线导通,即:assign ram_data = ram_data_selct ? output_ram_data:52'bz;中的ram_data_selct拉高,为写数据做好准备;当状态机进入c_read状态时,输入输出双端口线高阻,为接受读数据做准备,即:assign ram_data=ram_data_selct?output_ram_data:52'bz;中的ram_data_selct拉低,为读数据做好准备.

3.2.2 地址通道模块 地址通道不仅传输读写数据的地址,而且传输控制命令,模式寄存器的数据.在i_mrs状态,数据通道传递模式寄存器的相关参数,在c_ract状态传递读操作的行地址,在c_read状态传递读操作的列地址,在w_ract状态传递写操作的行地址,在w_read状态传递写操作的列地址.

3.2.3 命令模块 在不同的状态,控制命令不同,也使命令模块的输出不同.在i_start、c_end、c_idle时输出NOP命令,在i_aref0、i_aref1、i_aref2、c_pall状态时输出自刷新命令,在c_ract、c_read、c_wact、c_write状态分别输出激活、读命令、激活、写命令.

3.3 SDRAM仿真模型

采用三星SDRAM的verilog模型[8]进行功能仿真、时序仿真,仿真模型的部分程序如下:

ifdef CS2_CKE2

ifdef DPD_PIN

module sdram(clk, cs0b, cs1b, cke0, cke1, ba, ad, rasb, casb, web, dqm, dqi, dpdb);

else

module sdram(clk, cs0b, cs1b, cke0, cke1, ba, ad, rasb, casb, web, dqm, dqi);

endif

采用sdram(clk, cs0b, cs1b, cke0, cke1, ba, ad, rasb, casb, web, dqm, dqi);因为在电路板上已经将dpdb全部拉低.

4 仿真结果

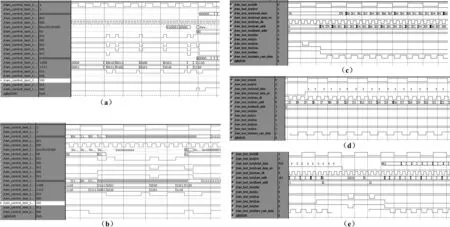

经过modelsim功能仿真[9-10]后的结果完全正确,仿真波形图如图6所示.

(a)SDRAM控制器初始化;(b)SDRAM控制器换行;(c)写操作的数据;(d)读操作的数据;(e)读写之间的切换 图6 仿真波形图Fig.6 The Simulation waveform

SDRAM能顺利的完成读写、刷新和预充电,行与行、块与块之间的交换平稳迅速,无论是连续读写还是单个的操作都非常的顺畅.如果读写请求的时序安排合理,按照SDRAM读写的效率计算公式:

其中有256个时钟周期,则连续读写时间为256;换行时间包括:c_end、c_pall、c_idle、c_wact/c_ract,总共需要10个时钟周期;SDRAM每个64ms刷新一次,采用的时钟为125 MHZ,SDRAM行地址为4096,则总的刷新时钟数为:64 ms/(8 ns*4096)= 1930,所以刷新间隔为1930;刷新操作包括:c_end、c_pall、c_idle、c_ref、c_wact/c_ract,总共需要18个周期,即刷新操作时间为18.从仿真结果可知本SDRAM的最高效率可以达到90%以上.先将连续增加的数据写到SDRAM的储存空间,然后从相应的存储空间读取数据,输入数据与输出数据应当相等,实际的仿真结果如所图6(b)所示.

下面是三段modelsim时序仿真的结果:

第一段:读写之间的切换

# >> write (D Bank) at 351430.0 ns

# >> precharge (A,B,C, and D bank) at 351486.0 ns

# >> active (A Bank) at 351518.0 ns

# >> write (A Bank) at 351542.0 ns

当写地址要换块时,先停止当前的写状态,然后进入预充电状态(precharge),关闭所有的块(A,B,C, and D bank),最后再次激活新的块(active (A Bank)),并再次进入写状态,重新写下一个块的数据.

第二段:读过程中换块

# >> read (B Bank) at 311190.0 ns

# >> precharge (A,B,C, and D bank) at 311246.0 ns

# >> active (C Bank) at 311278.0 ns

# >> read (C Bank) at 311302.0 ns

当读地址要换块时,先停止当前的读状态,然后进入预充电状态(precharge),关闭所有的块(A,B,C, and D bank),最后再次激活新的块(active (A Bank)),并再次进入读状态,重新读下一个块的数据.

第三段:写过程中自我刷新

# >> write (D Bank) at 349518.0 ns

# >> precharge (A,B,C, and D bank) at 349574.0 ns

# >> auto refresh at 349606.0 ns

# >> active (D Bank) at 349678.0 ns

# >> write (D Bank) at 349702.0 ns

当SDRAM需要自我刷新时,停止当前的状态,然后进入预充电状态(precharge),关闭所有的块(A,B,C, and D bank),最后进入自我刷新状态(auto refresh),刷新完成以后再次回到以前的读写状态.

可以发现SDRAM顺利地完成了相应的操作:如读操作、写操作、自我刷新、换块、读写之间的切换、预充电、激活等.

5 结束语

本控制器采用简化的接口电路,读写控制方便,为了配合本控制器的操作可以编写相应的读写地址模块.从仿真结果可以看出,在读写操作和换行换块的过程中,有几个时钟周期的空白命令,

4 结论

在充分考虑蚂蚁群算法计算代价大、容易早熟收敛的缺点,利用非线性单纯形算法局部搜索能力强的的特点,将两者合理融合,设计单纯形蚁群算法,通过标准函数测试表明该算法较一般蚁群算法较好.并且应用该算法解决了大规模垃圾站运输问题.

[1] Dorigo M,Di Caro G,Gambardella L M.Ant algorithms for discrete optimization[J].Artificial Life,1999,5(2):137-172.

[2] Dorigo M.Optimization,learning and natural algorithms[D].Department of Electronics,Politecnico diMilano,Italy,1992.

[3] 吴启迪,汪镭.智能蚁群算法及应用[M].上海:上海科技教育出版社,2006.

[4] 段海滨,王道波,朱家强,等.蚁群算法理论及应用研究进展[J].控制与决策,2004,19(12):1321-1326,1340.

[5] 段海滨,王道波,于秀芬.蚁群算法的研究现在及其展望[J].中国工程科学,2007,9(2):99-101.

[6] 向长城,黄席樾,杨祖元,等.小生境粒子群优化算法[J].计算机工程与应用,2007,43(15):41-43.

[7] 刘云忠,宣慧玉.蚂蚁算法在车辆路径问题中的应用研究[J].信息与控制,2004,33(2):249-252.

[8] 崔雪丽,马良,范炳全.车辆路径问题(VRP)的蚂蚁搜索算法[J].系统工程学,2004,19(4):418-422.

[9] 中南大学数学建模网站资料下载[EB/OL].(2009-08)[2011-07-26].http://mcm.csu.edu.cn/resource/show resouce.aspx?resouceid=105.