基于FPGA的UART通信接口电路设计

2011-01-17张蕾

张 蕾

(山西煤炭进出口集团有限公司,山西 太原 030006)

目前,我国的煤矿设备自动化程度不断提高,井下作业对信号传输的要求也愈趋严格。本文研究的通用串行收发器(universal asynchronous receiver and transmitter,UART)可通过串行线传输并行数据,其本质功能是作为控制器和串行设备间的编码转换装置,在基于RS232、RS485等标准协议的通信系统中广泛应用[1-3],非常适合矿井通信系统。常用的单片机、DSP控制器等一般都集成有专用的UART外设,极大地方便了基于RS232等协议的通信系统设计。但这类预先固化好的系统也存在一定的不足,如工作模式不够灵活,数据位数固定、通信的波特率一般限制在几个固定的数值,可扩展性较小。

FPGA是在传统PAL、GAL等可编程器件的基础上进一步发展的产物,其使用非常灵活,同一片FPGA通过不同的编程数据可以产生不同的电路功能[4-6]。随着 FPGA技术的突飞猛进,其在通信系统、数据处理、网络通信、仪器仪表、工业控制、军事和航空航天等众多领域得到越来越广泛的应用。

现有RS232标准对接口的电气特性做了规定,但对连接的具体协议并不做详细规定,故用户可根据需求建立自己的高层通信协议。本文使用FPGA来设计满足矿井通信的RS232接口电路。使用FPGA设计UART接口电路,既能自定义波特率、高层的通信协议,且具有电路功能重配置功能,完全适合煤矿环境恶劣、系统复杂的通信要求。本文所设计的接口电路主要包括5个子模块:UART接收子模块、波特率发生器、FIFO接口、UART发送子模块、通信校验模块,现场试验表明了该接口电路具有良好的实用性及可靠性。

1 功能设计

1.1 过采样流程

一个UART一般包括发送器和接收器两部分。UART发送器的主要功能是读入并行的待发送数据,然后通过移位寄存器,以一定的波特率,将数据一位位地串行移出;接收器的主要功能则是串行读入接收到的数据,然后将其组合为并行数据,最终变换为实际数据。以数据发送为例,在RS232标准中,其常用的数据格式为:1位起始位(一般为0),6~8位数据位,1位可选的校验位,及停止位(一般为1)。

在接收到的数据中不包含波特率信息,为减小在通信中信号位的偏移,UART接收子模块只能从预定义参数中读出数据位[7]。本文使用过采样的方法来估计所接收数据的中点,相应读出数据位。例如,若过采样率为X,则串行数据将被采样X次。设通信中数据位位数为N,停止位位数为M,过采样率为16,则过采样的工作方式为:

1)等待收到的数据变为0,即接受到起始位时,启动采样计数器。

2)当采样计数器的值为7时,清空计数器并重新开始计数。

3)当计数器的值为15时,将接受到的位移入寄存器,并重新开始计数。

4)重复步骤3)(N-1)次,从而接收剩下的所有数据位。

5)如果通信中使用了校验位,则再重复步骤3)1次。

6)重复步骤3)M次,从而获得停止位。

本文对UART信号进行16倍过采样。在FPGA接收数据后,取过采样所得到的每个16位二进制数据字的中间四位,若中间四位中1的个数不小于3,则表示收到当前的UART数据位值为1;若中间四位中0的个数不小于3,则表示收到当前的UART数据位的值为0,否则认为数据传输出错。过采样功能在本质上代替了时钟信号的功能,相比使用上升沿检测法检测输入信号有效值的方法,使用过采样法可提高数据采样的准确性。

1.2 波特率产生器设计

设计过采样率为X的数据接收子系统之后,需使用1个时钟速率为X倍波特率的波特率产生器。在基于FPGA的设计中,通过简单的分频操作或者更高精度的时钟信号发生器即可产生一个满足需求的时钟信号,其实现较为灵活。以波特率为19 200 bps、过采样率为16倍为例,采样率为307 200次/s。设FPGA主时钟频率为常用的50 MHz,则波特率产生器需要一个模-163的计数器,即50×106/307 200=163。在本设计中,将过采样率X作为波特率产生器的一个可调参数,从而可以根据需求方便地重配置波特率产生器。

1.3 UART系统FIFO设计

在通信电路中,常使用FIFO来提供数据缓存,并减小数据溢出的概率。本文所研究的FIFO,从FPGA架构的特点来看,是一块基于块RAM的缓存。接收FIFO是一个128×8 bit的先进先出型缓存器,处理器通过检测rx_full或者rx_empty来决定是否读取FIFO内的数据。接收FIFO始终检测wr信号,若此信号有效,则表示接收部分接收到新的数据;若FIFO非满,则产生一个读信号rd_uart,把数据存储到FIFO中;若FIFO已满,则只产生读信号,并丢弃该数据。发送FIFO的设计与接收FIFO的实现方法基本类似,仅需对数据方向和读写信号进行少量的修改。

1.4 UART发送子模块设计

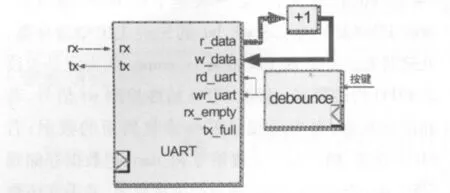

UART发送子模块的功能设计与接收子系统的构成基本相同,它的主要功能是将并行的数据通过移位寄存器串行发送出去,同时在数据头部加起始位,在数据位尾部加奇偶校验位和停止位。发送的速率通过波特率发生器产生的单时钟循环使能标记来控制。因为发送子模块不再需要设置接收子模块那样的过采样计数器,其频率计数器的时钟频率仅需要为接收子模块的1/16。为了节约资源,这里不再额外设置新的计数器,而是使用与接收子模块相同的同一个波特率发生器。综上所述,可以得出一个UART系统的整体框图,见图1。

图1 UART系统的整体框图

1.5 UART验证子模块

为了对UART的通信进行自校验,在通信链路中隔离故障,本文使用了一种执行回环测试的诊断机制,其原理框图见图2。回环模式仅用于测试目的,在正常操作模式下,该模块不被激活。在回环模式下,发送的数据的输出置为高电平。测试的基本过程是:从PC向FPGA发生一个字符串,收到的数据被储存在UART的接收FIFO中。按键开关在被按下之后,给出的信号被去抖动处理,然后产生rd_uart和wr_uard两个信号;FPGA读到这两个信号之后,将UART接收FIFO中的的数据每次递增加1,再通过发送子模块发送回FPGA进行循环测试。

图2 UART回环测试的原理框图

2 实验验证

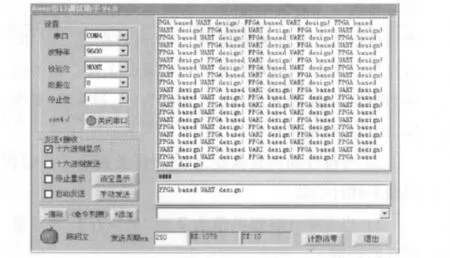

本文基于 Xilinx公司 Spartan3E系列的XC3S500E FPGA,实现了所设计的UART系统。首先,使用Verilog HDL语言编写了整个系统的代码;其次进行功能仿真、时序约束、软件综合、生产bit流文件及烧写FPGA的配置文件等FPGA开发的基本操作。测试的方法为:首先进行回环测试,如无误则点亮FPGA开发板上的LED表明系统正常。其次,在PC上发送“FPGA based UART design!”这样一个字符串至FPGA;在FPGA收到并判断为“!”之后,通过所设计的UART系统循环向PC发送所收到的字符串,并通过串口调试助手显示收到的数据。实验结果见图3。

图3 实验结果图

3 总结

本文结合煤矿自动化生产中对信号传输的实际要求,设计了一个基于FPGA的RS232接口电路,包含有过采样机制、波特率发生器、FIFO及回环测试功能的UART系统。经逻辑综合并下载到芯片中,通过实际的接收与发送实验,验证了本设计的正确性和可行性。在将来的研究中,还可对全双工通信中的读写控制等进行改进,并将整个系统封装为IP核,便于在后续的大系统中进行灵活的调用。

[1] 作 者,基于Actel FPGA的UART应用[J].电子产品世界,2009(6):76-77.

[2] 成 兰,崔亚量,田 原.一种基于TMS320C55x DSP的UART通信设计[J].微计算机信息,2008(5):153-154.

[3] 段素蓉,庄圣贤.一种内置FIFO全双工UART的设计与实现[J].通信技术,2010(2):46-47+50.

[4] 李萌萌,彭建朝,许向众.基于FPGA的多通道控制器的设计与模拟实现[J].微计算机信息,2009(14):168-170.

[5] 田 耘,徐文波,胡 彬,等.Xilinx ISE design Suite10.x FPGA开发指南—逻辑设计篇[M].北京:人民邮电出版社,2008:409.

[6] Harding,B.F.,R.C.Cofer,Rapid system prototyping with FPGAs- Embedded technology series[M].Amsterdam:Elsevier/Newnes,2006:301.

[7] Chu,P.P.FPGA prototyping by Verilog examples[M].Xilinx Spartan -3 version.Hoboken,N.J.:J.Wiley & Sons:488.