JTIDS传输符号产生模块的FPGA设计

2010-09-26牛强军1莫新康赵文俊1宋家友

牛强军1,莫新康,赵文俊1,宋家友

(1.空军第一航空学院 航空电子工程系,河南 信阳 464000;2.郑州大学 信息工程学院,郑州 450001)

1 引 言

Link16[1]是美国国防部选择的高速视距战术数据链,由时分复用(TDMA)协议、联合战术信息分发系统(JTIDS)波形和TADIL J消息标准组成,采用直接序列扩频、调频等抗干扰技术,具有容量大、保密性好、抗干扰能力强、使用灵活、功能齐全等特点。鉴于数据链在现代战争中的重要作用,对Link16进行研究具有重要意义。

JTIDS终端是Link16的通信载体,承载了Link16数据链数据发射前的信息处理和数据接收后的信息还原,传输符号产生模块是JTIDS发射端基带信息处理部分。为便于在实验室内对JTIDS进行测评,采用FPGA设计了一种可实现JTIDS终端基带数据处理功能的实验板,经过测试验证了该设计的正确性与可靠性。由于该系统集成度高,资源占用少,且留有前置和后置接口,可方便嵌入相应系统中完成相关性能的测评,也可在该模块基础上添加JTIDS射频处理模块设计成为一个完整的JTIDS发射终端。

2 传输符号产生原理及子模块设计

传输符号产生模块是指待发送信息经过RS编码、交织、CCSK软扩频、CCSK码字加密等一系列(图1)的处理[2-3]后得到传输符号,从而为下一步MSK调制提供激励。

图1 JTIDS传输符号产生模块系统框图Fig.1 Systemic diagram of JTIDS transmission code generator

2.1 RS编码

Link16采用TADIL J系列消息格式。J系列报文中,包含20 bit的报头和3组75 bit的消息,将每5 bit作为一个码元,即为4码元的报头和3组15码元的消息,共49码元,对报头进行RS(16,4)编码,对3组消息字分别进行RS(31,15)编码,最后得到编码后的16码元报头和93码元消息字共109码元。

下面以RS(31,15)为例介绍RS编码原理及其电路设计实现[4-6]。

对应RS码的参数,RS(31,15)为编码后码长n=31,信息码长k=15,检错能力2t=16,最大纠错能力t=8,5位32进制码。

设信息多项式为

m(x)=mk-1xk-1+mk-2xk-2+…+m1x+m0

(1)

校验多项式为r(x),码多项式为c(x),生成多项式为

gx=x+αx+α2…x+α2t-1x+α2t

(2)

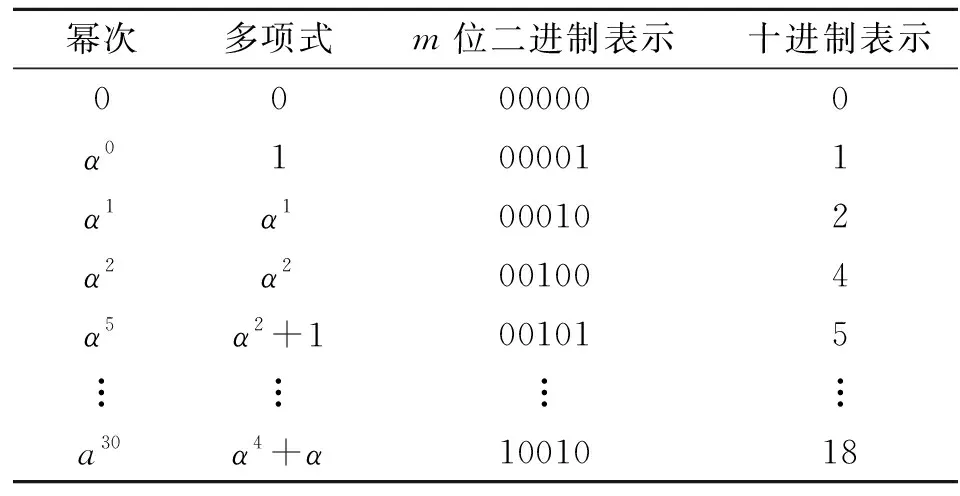

RS编码过程中涉及的运算均是在伽罗华域进行。对于32进制RS编码,m=5,选择本原多项式f(x)=x5+x2+1,由本原多项式生成的伽罗华扩域如表1所示。

表1 由f(x)=x5+x2+1生成的GF(25)扩域Table 1 Extension field GF(25) generated by f(x)=x5+x2+1

伽罗华域加法和乘法运算方法如下:

加法(减法相同):模二运算,如:

α8+α20=01101+01100=00001=α0=1

(3)

乘法:指数相加后对2m-1取模,如:

α8×α25=α8+25mod 31=α2

(4)

按照上述运算方法将生成多项式g(x)展开得:

gx=x2t+gn-k-1x2t-1+…+g1x+g0

(5)

根据RS编码原理有如下运算关系:

rx=xn-kmxmodgx

(6)

cx=xn-kmx+rx=

xn-kmx+xn-kmxmodgx

(7)

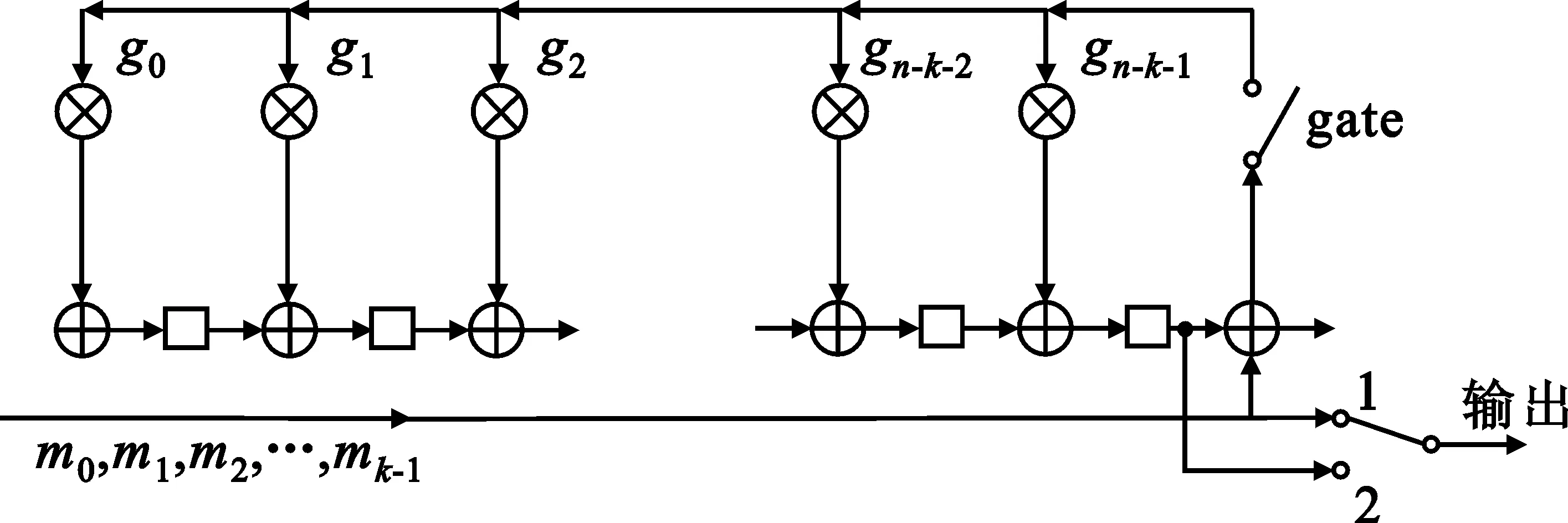

则c(x)的编码电路可由多项式除法电路改进后实现,如图2所示,图中方框表示寄存器。

图2 RS编码电路图Fig.2 Circuit diagram of RS encoding

编码电路流程说明如下:

(1)开关接通1,gate闭合,随着时钟的继续,输入数据一方面输出,另一方面进入除法器完成除法运算,并将余式的系数存于各级寄存器中;

(2)k个时钟之后,开关拨到2,gate打开,将存储在寄存器中的余式系数输出,与先前的输出信息码组合即为最终的RS码,待2t个时钟后,重复上一步,即可实现无缝连续编码。

对于RS(31,15)编码,只需要将各个参数输入编码电路中,编码运算即可实现并正确输出;对于RS(16,4)编码,由于标准的RS码要求n=2m-1,如果n≠2m-1,则该RS码是对应标准RS码的截断码,RS(16,4)是RS(31,19)的截断码,只需要写出后者的编码程序(方法同RS(31,15)),并且调整使能信号在输入到第四位有效信息时跳变,然后开始输出校验信息即可,相当于在4位信息前补15个0位。

2.2 31×3交织

交织技术有利于提高消息的保密性和JTIDS的抗干扰能力,将传输过程中出现的错码离散化,使得纠错能力从RS(31,15)的最多纠正8个错码,增加到最多纠正8×3个错码。

交织采用块交织的方式,如图3所示。在设计时采用片内双口SRAM,将93个码元依次写入SRAM然后读使能,按照行入列出的顺序通过地址变换读取SRAM中的数据,经过比较,若采用传统数组下标转换的方法会占用较多的FPGA逻辑资源(大于等于20%,只针对本设计所使用FPGA芯片型号),而采用双口SRAM则只占用不到1%。

图3 块交织示意图Fig.3 Diagram of block interleaver

2.3 循环码移位键控(CCSK)编码

CCSK软扩频是将原始的5 bit码元用一组32 bit的CCSK码字来代替,进一步提高了系统的抗干扰和保密性能。表2列出了5 bit码元和32 bit的CCSK码字之间的对应关系,通过对长度为32 bit的CCSK码字S0循环左移n次,就可得到第n个码元对应的长度为32位的CCSK码字,n是被编码码元的值(00000~11111)。

表2 循环码移位键控(CCSK)码字(32 bit)Table 2 CCSK code(32 bit)

在设计时采用片内ROM。由于5 bit码元和容量为32的ROM地址一一对应,将上述对应关系写入ROM中,即可正确调取ROM里的CCSK码字。

2.4 CCSK码字加密

此步骤是为了提高JTIDS波形的传输保密能力。CCSK码字加密指的是将生成的CCSK码字与一个32 bit伪随机噪声进行异或运算,因此,当数据最终发送时,数据看起来就像不相干的噪声。对非法窃听者而言,传输脉冲信号以随机调制的形式出现,无法预测。对合法接收机而言,具有准确已知的系统时间(实现同步后),能够实现对伪随机噪声信号的检测,恢复出CCSK码字,并解码为CCSK码字所代表的5 bit数据,从而实现数据的还原。

伪随机序列(Pseudo-noise,PN)也称作伪码,它既有近似随机序列(噪声)的性质,又能按一定规律(周期)产生和复制序列。

最常见的二进制PN序列是最大长度线性移位寄存器序列,也称m序列,可由m级线性反馈移位寄存器(LFSR)生成。选取适当的反馈方式,m级LFSR所产生的序列周期可以达到2m-1。定义LFSR的特征多项式:

px=xm+fm-1xm-1+…+f1x+1

(8)

则由p(x)所对应的m级LFSR输出最长序列的充要条件是p(x)为本原多项式。

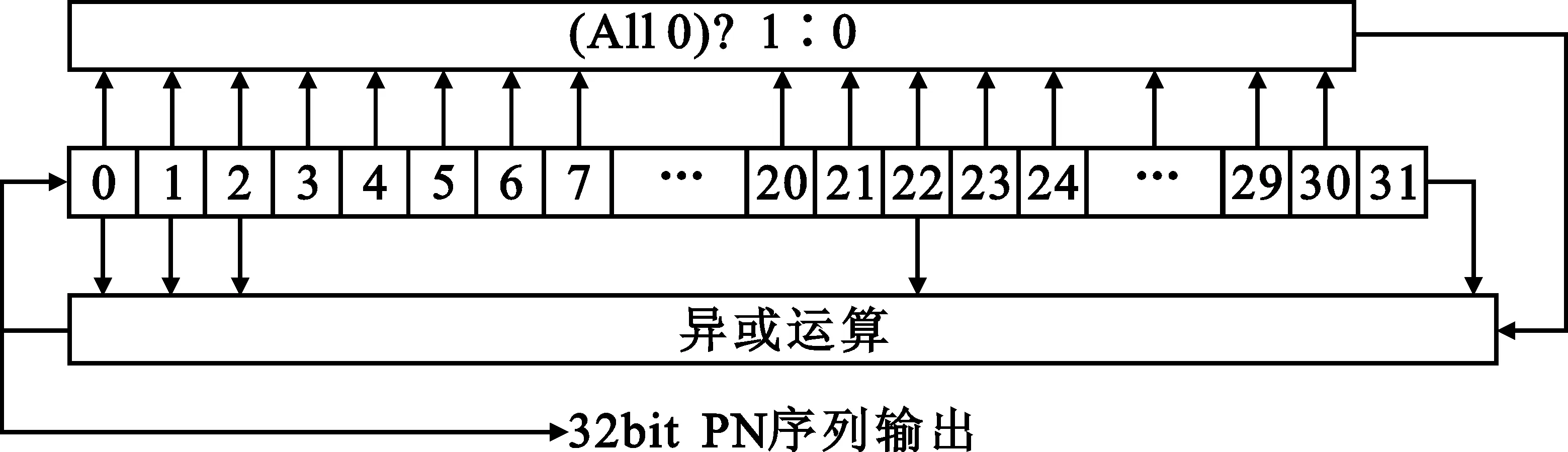

本伪随机序列产生器需要产生32 bit伪随机序列,需要32级LFSR,所用到的特征多项式经过查询列出如下:

px=x32+x22+x2+x+1

(9)

在设计时把全零的状态也考虑了进去,使得该伪随机序列产生器序列的周期达到了2m。PN码产生流程如图4所示,32级LFSR中存储的是移位初始值,该值决定了后续解密时的同步问题。

图4 伪随机序列产生器流程图Fig.4 Flow chart of pseudorandom sequence generator

3 传输符号产生模块综合设计与仿真

综合各个子处理模块的原理及设计方案,给出了传输符号产生模块的系统级设计框图,如图5所示。在Quartus II环境[7]下选择Cyclone II系列的EP2C8Q208C8 FPGA芯片进行了系统级功能仿真与时序仿真。

图5 JTIDS传输符号产生模块设计流程图Fig.5 Flowchart of JTIDS transmission code generator

进行整个系统的综合设计时需要解决一系列问题,其中最主要的影响处理结果正确性的因素是时序问题,即在将各子模块综合处理过程中注意各模块之间的无缝衔接,本设计的综合过程如下:利用一个容量为64、位宽为5的SRAM对输入的49码元数据进行存储(15×3码元信息+4码元报头),通过读取SRAM的地址调取前4码元报头进行RS(16,4)编码,调取后45码元信息进行连续的3组RS(31,15)编码,将后者输出直接送至31×3交织器进行交织,然后将前者输出与交织器的输出组合后的109码元(31×3+16)存入事先设计好的容量为128、位宽为5的SRAM中,之后通过调取SRAM中的数据在存有CCSK码字的ROM中获取各自对应的32 bit CCSK码字,最后与独立的PN序列产生器产生的32 bit伪随机序列异或输出即为最终的传输符号。

为便于观察结果,仿真时设置输入49码元用十进制表示为:1 2 3 4 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 1 2 3 4 5 6 7 8 9 10 11 12 13 14 5,并用计数器自始至终跟进,得到的时序仿真波形图如图6所示,传输符号的仿真结果与预期正确结果相同。

图6 JTIDS传输符号产生模块系统级时序仿真图Fig.6 Time simulation of JTIDS transmission code generator

counter为计数器,rst为高电平时开始计数,out1为容量为64的SRAM写入49位din并按照要求输出的结果,out2为对SRAM中的后45位数据进行连续RS(31,15)编码后的结果,out3为对SRAM中的前4位数据进行RS(16,4)编码后的结果,out4为对out2进行31×3交织后的结果,out5为将out3和out4按照先报头后信息顺序(前16位,后93位)组合后存入容量为128的SRAM后的结果,out6为读取128位SRAM中的数据进行CCSK编码后的结果,out7为实时产生的32 bit伪随机序列,dout为out6与out7异或(CCSK码字加密)后的最终传输符号。

4 结 论

整个JTIDS传输符号产生模块在Quartus II环境下选择Cyclone II系列的EP2C8Q208C8 FPGA芯片进行系统级综合与仿真只占用5%~6%的逻辑资源,芯片内部存储资源也只占用了1%左右,并在Cyclone II FPGA开发板上验证了其正确性与可行性。利用FPGA对JTIDS传输符号产生模块进行可编程设计,可以使硬件设计工作转换为软件设计工作,缩短了系统设计周期,提高了实现的灵活性,降低了成本,且由于设计集成度高,加上FPGA的高速数据处理和控制能力,系统有效性和稳定性得到了保证。

参考文献:

[1] 梅文化,蔡善法.JTIDS/Link16数据链[M].北京:国防工业出版社,2007:79-84.

MEI Wen-hua, CAI Shan-fa. JTIDS/Link16 Data Link[M].Beijing:National Denfense Industry Press, 2007:79-84. (in Chinese)

[2] 冯天雨,邓双成,杨家玮.JTIDS系统物理层的研究与实现[J].空间电子技术,2007(7):74-77.

FENG Tian-yu,DENG Shuang-cheng,YANG Jia-wei.Research and Implementation on JTIDS Physical Layer[J].Space Electronic Technology,2007(7):74-77.(in Chinese)

[3] 孙颖.JTIDS系统及其干扰研究[D].西安:西安电子科技大学,2006.

SUN Ying. Research of the JTIDS and its Interference[D]. Xi′an:Xidian University,2006. (in Chinese)

[4] 曲伟华,鞠建波,别庆,等.JTIDS系统的RS码性能分析[J].电讯技术,2007,47(2):48-50.

QU Wei-hua,JU Jian-bo,BIE Qing,et al.Performance Analysis of RS Code in JTIDS[J].Telecommunication Engineering,2007,47(2):48-50.(in Chinese)

[5] 倪燕,陈颖,杨云志,等.高速RS(31,15)编译码器的FPGA实现[J].电讯技术,2005,45(1):174-177.

NI Yan,CHEN Ying,YANG Yun-zhi,et al.Implementation of RS(31,15) Encoder and Decoder with FPGA[J].Telecommunication Engineering,2005,45(1):174-177.(in Chinese)

[6] 刘福奇,刘波.Verilog HDL应用程序设计实例精讲[M].北京:电子工业出版社,2009:465-472,388-392.

LIU Fu-qi, LIU Bo.Verilog HDL Language Example Applications[M]. Beijing:Publishing House of Electronic Industry,2009:465-472, 388-392. (in Chinese)

[7] 周润景,图雅.基于Quartus II的FPGA/CPLD数字系统设计实例[M].北京:电子工业出版社,2008:298-306.

ZHOU Run-jing, TU Ya. FPGA/CPLD Digital System Example Applications[M].Beijing:Publishing House of Electronic Industry,2008:298-306.(in Chinese)