基于DSP的任意波形信号发生器的设计与实现

2010-04-08西北工业大学自动化学院西安710072杨建华

西北工业大学自动化学院(西安 710072) 苏 坡 杨建华

西北工业大学 航海学院(西安 710072) 侯 宏

0 前言

在现代测控领域,任意波形信号发生器已经成为系统研发和调试必不可少的工具。而目前市场上的信号发生器价格昂贵,体积比较大,而且波形可编程灵活度小,不能满足实际的需要。

随着电子技术和数字技术的飞速发展,DSP系统已经在众多高科技领域获得广泛的应用,它具有速度快、编程方便、精度高、稳定性好、接口方便、集成度高等特点。本文借助DSP系统的这些优点,设计了一种基于DSP的任意波形的信号发生器AWG(Arbitrary Waveform Generator),具有成本低,稳定性好,结构简单的特点。

1 信号生成原理

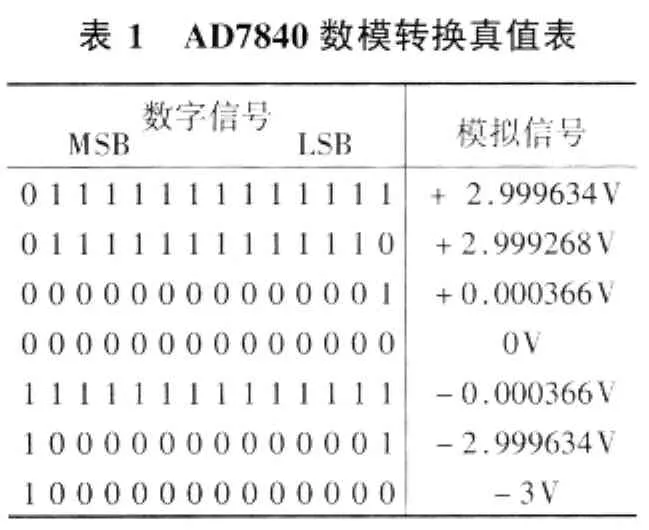

运用Matlab仿真[1]产生待生成信号的数据文件,通常该数据文件都是浮点形式的,根据数/模芯片转换的真值表,将浮点形式的数据文件转化成对应的十六进制INTEL格式数据文件,然后将该数据文件Load载入到DSP的数据存储空间,接着通过DSP控制DA转换芯片产生所需的信号。

2 系统硬件设计

根据任意波形信号的生成原理,本文选用DSP和CPLD联合控制的方式,系统主要分为4大功能模块:1)DSP及其外围;2)DA模块;3)存储扩展;4)CPLD。

2.1 DSP极其外围

考虑到成本和易开发性,主控芯片选用TMS320VC33。VC33是TI推出的一款32位浮点DSP,它的运算速度达150MFLOPS[2],单周期完成32位整数、40位浮点乘法运算;它的地址总线为24位,寻址空间为16M×32bit,为了方便外部存储器存取,把16M×32bit空间分为PAGE0,PAGE1,PAGE2,PAGE3,当STRB和其中一个PAGE同时有效时,存储器接口选通;片内34K×32bit SRAM,片上集成一个同步串口,两个32bit的定时器,一个DMA通道;支持IEEE Std.1149.1(标准),0.18-us工艺,1.8V 核心电压,3.3V I/O电压,低功耗。

电源芯片选用TI公司的TPS767D318芯片,它把5伏的输入电压转化成+3.3V和+1.8V分别供给DSP的外围和内核。

2.2 DA模块

选用AD公司生产的AD7840单通道DA转换芯片,该芯片转换速度可达到400kHz,转换精度14bit,转换范围为-3V至+3V[3],能够满足任意波形信号产生的要求。该芯片的数据线与DSP芯片数据线的低14位相连,它的电压转换公式为其中Vou+为输出的模拟电压,PEFIN为参考电压(+3伏),N值为数据总线上提供的数字信号,其范围是:-8192#N#8191。其数字信号转换成模拟电压信号对应的真值表如表1所示。

?

在DA模块的前端设置滤波调理放大电路。

2.3 存储扩展模块

包括外扩RAM和外扩FLASH。由于VC33内部的存储空间有限,所以要对VC33进行存储扩展。外扩RAM选择CY7C1041,它是一款256K×16bit的静态RAM。VC33没有内部Flash,为了完成脱机运行和保存数据,本设计选择DA28F320作为外扩FLASH,它是一款2M×16位的NOR FLASH。

2.4 CPLD控制模块

CPLD控制模块是本设计的关键模块。使用CPLD器件可以提高系统设计的灵活性,并且可以简化电路设计,节省很多常规电路中的接口器件和I/O口线。由于VC33的内部资源有限,有较少的I/O口,而本设计外围设备比较多,因此采用DSP和CPLD联合控制的方式。CPLD控制模块主要实现对外围设备的选址,使能和逻辑协调控制。

本设计CPLD选用的是ALTERA公司MAX7000系列的EPM7128STC100芯片,它具有高阻抗、电可擦等特点,可用门单元为2500个,管脚间最大延迟为5ns,工作电压为+5V。在本设计中,将DSP地址总线的高八位A16至A23、读写、片选及分页管脚PAGE0至PAGE3、外部存取选通信号STRB等控制信号接入CPLD,实现对外围设备的选址、使能、中断控制和有关逻辑控制[4]。

当STRB和PAGE0有效,地址线的高8位A16-A23等于0x20时,选通AD7840芯片(=0);外扩RAM CY7C1041的地址线与VC33的低18位相连,当STRB和PAGE0有效,地址线的高6位等于001011时,选通外扩 RAM(=0);当 PAGE1有效时,选通 FLASH DA28F320(=0),通过 CPLD的 I/O口输出高电平给使FLASH工作在普通模式。

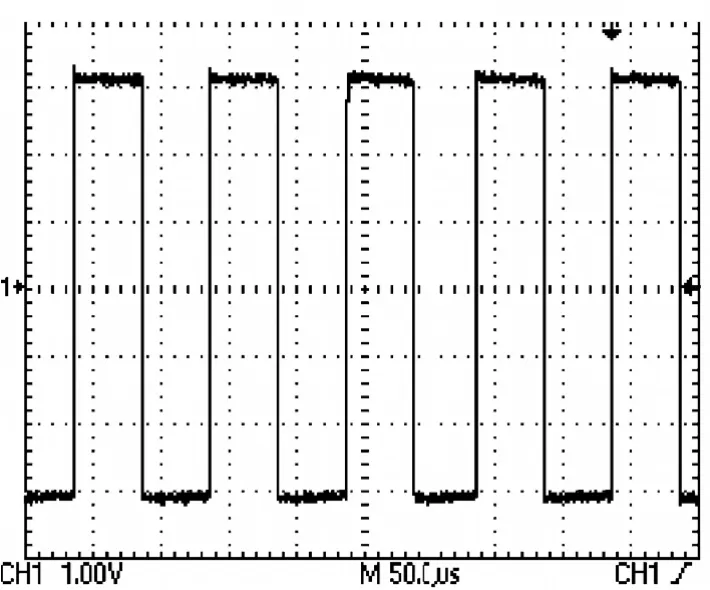

图2 生成的幅度为3V频率为10KHz的方波信号

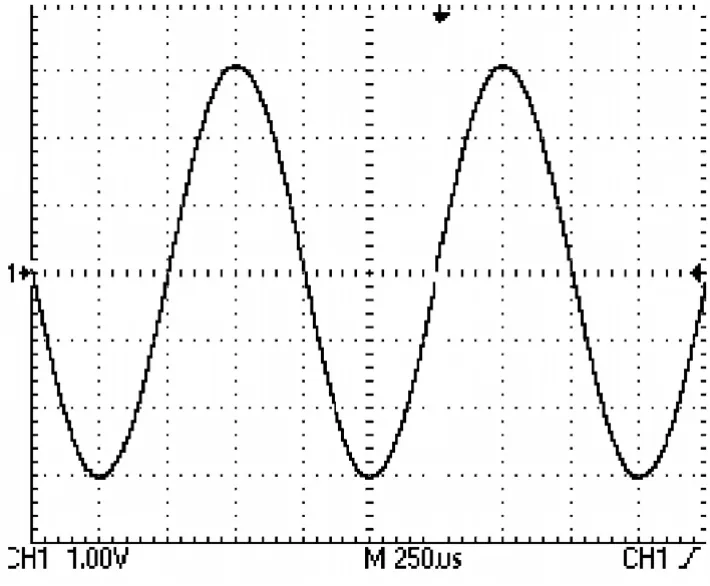

图3 生成的幅度为3V频率为1KHz的正弦波波信号

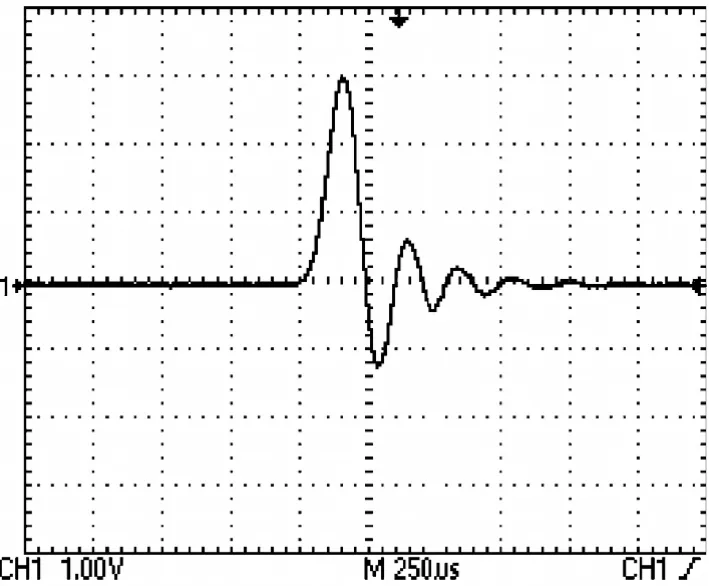

图4 生成的幅度为3V长度为3ms的巴特沃斯脉冲信号

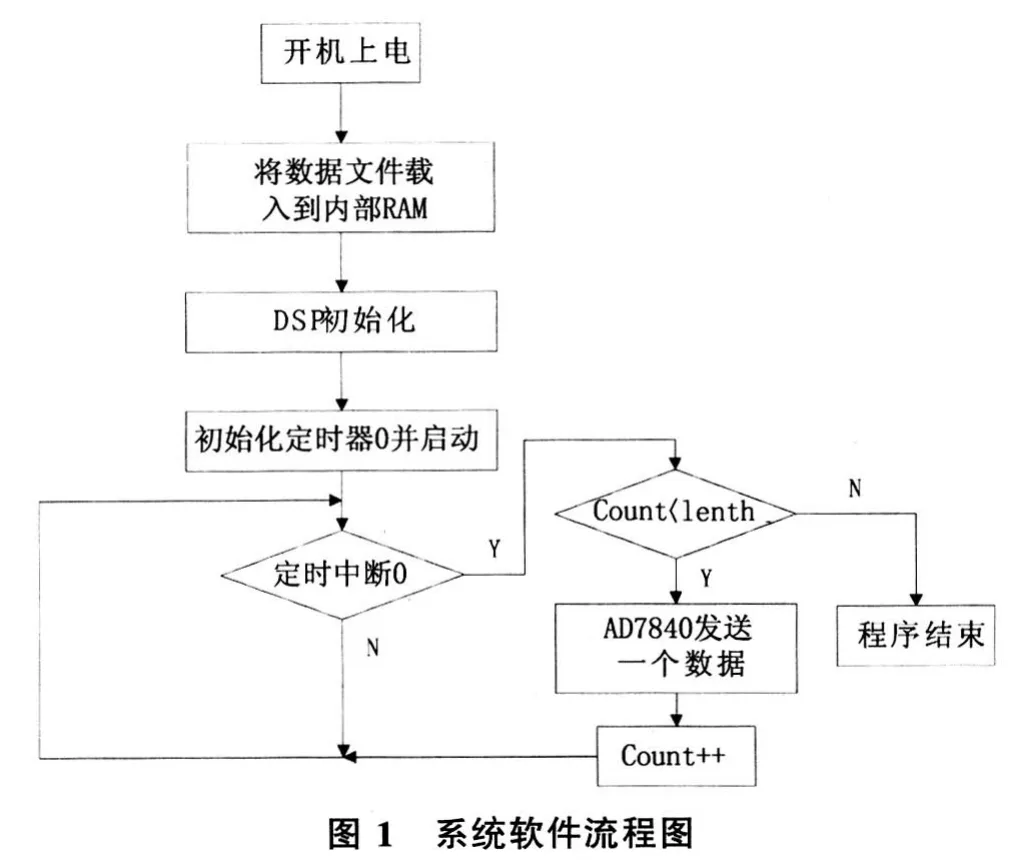

3 系统软件设计

系统软件包括两个部分:数据格式转换程序和DSP控制程序设计。

3.1 数据格式转换

该部分程序采用Matlab编程。先用Matlab仿真产生待生成信号的数据文件,根据DA芯片数模转换的真值表,对信号的数据文件进行逐点转换,将数据文件转换成十六进制的INTEL格式。VC33的数据总线为32位,而AD7840的数据位数为14位,因此,转换后的十六进制INTEL格式低4位有效,高4位均为0,例如0x00001FFF表示+2.999634 V。转换的方法如下:

根据转换公式 N=round(Vou+×8192/3),将浮点形式的数据转换成十进制的整型形式。N为转换后的十进制整型形式,round()表示按四舍五入的方法取整。

如果 N为正,直接将其存储为十六进制的INTEL格式。

如果 N为负,首先将转换成14位的补码形式,然后存储为十六进制的INTEL格式。将 N转换成补码形式的方法为 N=214-abs(N),其中 abs()表示取模。

3.2 DSP控制程序设计

系统用定时器0控制模数转换芯片AD7840产生所设计的信号,转换速率要与Matlab仿真产生的信号的采样率一致。系统的软件流程图如图1所示

4 信号生成实验

利用本系统生成了三种波形的信号;分别为幅度为3V频率为10KHz的方波信号;幅度为3V频率为1KHz的正弦波信号;幅度为3V长度为3ms的巴特沃斯脉冲信号。通过示波器观察到的波形分别如图2,图3,图4所示。

从图2,3,4可以看出,该系统产生的波形与设想产生的波形一致。实验证明该系统可以产生所需要的波形。

5 结束语

本设计利用DSP+CPLD作为硬件平台,成功实现了任意波形发生器,该系统具有成本低、体积小、硬件电路简单、使用方便的特点,能够满足工程实际的需要,具有良好的应用价值。

[1] 任绪科,赵俊渭,周明.基于CPLD和单片机的任意波形发生器设计[J].电子产品世界,2005(1)

[2] 党瑞荣,谢燕,李利品.TMS320CX DSP原理及应用[M].西安:陕西科学技术出版社,2006,3

[3] 唐健,雷轶鸣,邹健.14位串/并行D/A转换器AD7840及在程控电流源中的作用[J].四川文理学院学报,2007,17(5)

[4] 周 健,闫建国,周志久.CPLD在在惯性测量单元数据采集系统中的应用[J].电子测量技术,2008,11(31)