基于FPGA 的FLASH 存储器三温功能测试系统设计

2024-03-01侯晓宇常艳昭

侯晓宇,郭 贺,常艳昭

(中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

0 引言

存储器的测试主要由内建自测试和外部测试构成[1⁃3]。内建自测试由于芯片内部测试电路已固化,测试图形无法改变,也无法保障测试的故障覆盖率[4];而外部测试一般由ATE(Automatic Test Equipment)机台来进行批量化测试[5⁃6]。大容量FLASH 存储器因存储容量大[7⁃9],在保障故障覆盖率的情况下,其测试向量较大,而ATE 测试系统因有限的存储容量,很难保障大容量存储器的高覆盖率测试。此外,为保障器件的可靠性,需对大容量FLASH 存储器进行三温环境测试。传统的基于ATE 和热流罩的环境测试装置及方法存在如下缺陷:一方面,热流罩体积较小,多工位测试能力受限;另一方面,热流罩无法长时间扣压在ATE 机台上,否则会导致ATE 机台掉电重启,而大容量的FLASH 存储器全地址功能测试耗时数小时,故该方法仅能在常温下对大容量FLASH 存储器进行全地址功能测试,且占用大量ATE测试机时,测试成本较高。因此,亟需在原有的技术基础上进行突破创新,实现大容量FLASH 存储器的三温环境测试,同时提高测试效率,降低测试成本。本文提出了一种基于FPGA 驱动板+工位板的板级FLASH 存储器三温功能测试系统,实现了12 工位的大容量FLASH存储器的三温功能测试,解决了ATE 机台无法长时间进行高低温测试的难题,同时释放大量ATE 机台时,提高了测试效率,降低了测试成本。

1 FLASH 功能测试原理

FLASH 存储器的故障主要有固定型故障、转换故障和固定开路故障等[10]。固定型故障是指存储单元内的逻辑值始终为0 或1。转换故障是指存储单元内的逻辑值可以从1转换为0,但无法从0转换为1,或逻辑值可以从0 转换成1,但无法从1 转换成0。固定开路故障是指无法访问当前存储单元内的逻辑值。通常,采用特定的测试图形来检测FLASH 存储器存在的故障,理论上存在一种测试图形算法可以检测出所有的故障类型,但由于其时间复杂度而无法完全应用于实际工程中[11]。MSCAN算法也被称为全0或全1算法[12],即在所有存储单元中写入逻辑0 或逻辑1。MSCAN 算法见图1。

图1 MSCAN 算法

Checkerboard 算法也被称为棋盘法,如图2 所示,该方法用于检测相邻单元在存储数据时是否存在相互影响,即在相邻两个存储单元写入不同的逻辑值。

图2 Checkerboard 算法

2 硬件设计

基于上述方案设计,采用子母方案实现硬件平台的设计。硬件平台如图3 所示,该平台由驱动板和工位板两个部分组成。驱动板主要包括FPGA、串口模块、电源模块、时钟模块、存储模块、电平转换模块和金手指接口。工位板和驱动板之间通过金手指相互连接,12 个工位的被测芯片依次排列在工位板上组成测试阵列。

图3 硬件平台总体框架

为满足多工位测试要求,FPGA 选用Xilinx Kintex7系列XC7K325T,其外挂DDR 和FLASH 存储模块分别用于数据缓存与烧写程序的启动。此外,FPGA 通过串口模块实现与上位机之间的通信。

3 软件设计

基于上述硬件平台,本测试系统软件任务由FPGA和上位机两个部分构成,如图4 所示。FPGA 主要负责对12 个工位的被测芯片施加激励信号、测试结果比对和与上位机串口数据的传输工作。上位机主要负责与FPGA 的串口传输工作、测试结果的显示和测试结果的保存。

图4 测试系统软件总体框架

测试系统工作流程如图5 所示。上位机首先通过串口将配置命令发送至FPGA,接着FPGA 对被测芯片施加激励信号,随后FPGA 将接收到的返回信号进行数据比对,进而通过串口发送至上位机,最后上位机在界面上实时显示测试结果并将数据保存至硬盘。

图5 测试系统工作流程

3.1 FPGA 软件设计

FPGA 对被测芯片依次施加激励信号,并对返回的数据结果进行比对,其状态机如图6 所示。首先对被测芯片进行全地址擦写,读全地址,若非全1 则跳转至错误状态;接着对芯片进行全地址写0,读全地址,若非全0,则跳转至错误状态;随后对芯片进行全地址擦写,全地址写0xAA55,读全地址,若非全0xAA55,则跳转至错误状态;最后对芯片进行全地址擦写,全地址写0x55AA,读全地址,若非全0x55AA,则跳转至错误状态。

3.2 上位机软件设计

上位机采用Qt 作为开发工具,该软件主要将界面上的控制命令进行组帧并通过串口发送出去[13],解析串口中收到的数据,将测试结果显示在可视化界面并存储至硬盘。为有效区分串口接收的数据类型,定义了如图7 所示的数据帧格式,共分为5 个部分,如下:

图7 数据帧格式

1)帧头:长度为32 bit,定值为0x1234567。

2)内容形式:长度为32 bit,0x0 表示命令参数,0x1为被测芯片返回的测试结果。

3)长度:长度为32 bit,该变量表示为数据帧中发送内容的字节大小。

4)内容:具体发送数据。

5)帧尾:长度为32 bit,定值为0x89ABCDEF。

4 实验与分析

FLASH 存储器三温功能测试系统的驱动板和工位板实物图如图8 和图9 所示,两块板卡通过金手指接口插入三温测试箱实现互联。

图8 FLASH 存储器三温功能测试系统驱动板

图9 FLASH 存储器三温功能测试系统工位板

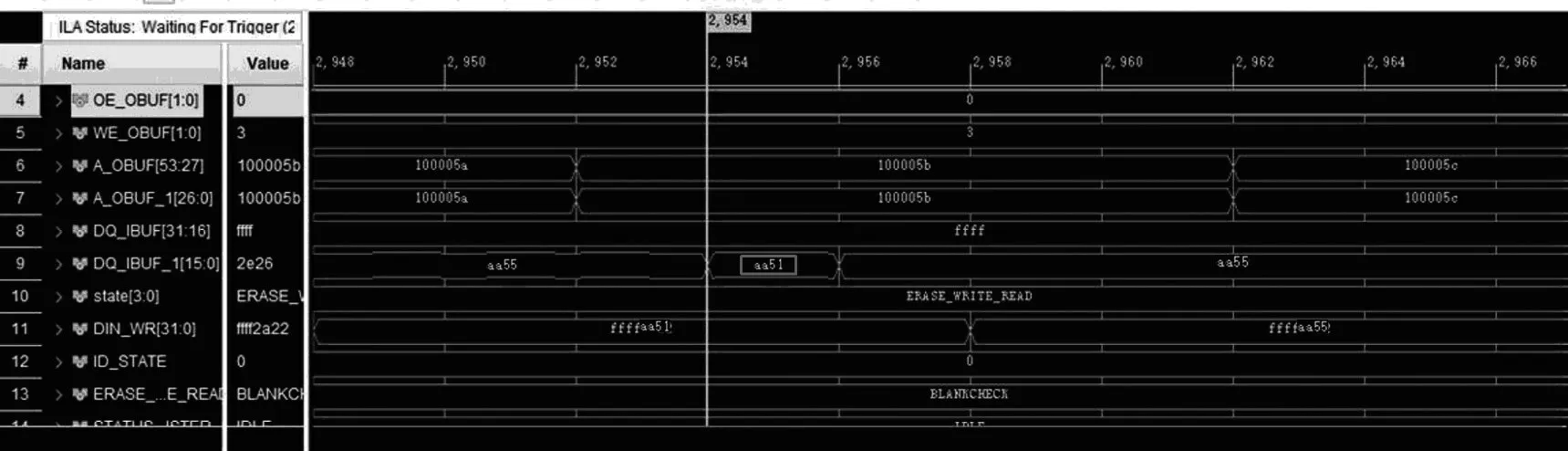

如图10 所示,当被测芯片写入的数据0xAA55 和读出的数据0xAA51 出现不一致时,则当前芯片测试停止,并将测试结果上传至上位机。

图10 错误数据显示

如图11 所示,上位机接收到数据后,实时显示出错误工位号、错误地址和读出的错误数据。

图11 上位机结果显示

5 结论

本文设计一种基于驱动板和工位板的FLASH 存储器的实装测试系统,并完成了对此系统的验证。结果表明,该测试系统可实现12 工位的大容量FLASH 存储器在三温环境下的全地址擦写和读功能测试,以及测试结果的实时显示与本地存储。相较于传统使用ATE 机台对FLASH 存储器进行测试的方法,该测试系统有效解决了ATE 机台在高低温环境下无法长时间测试的缺点,同时释放大量ATE 测试机时,大幅降低了FLASH存储器芯片的测试成本。此外,12 工位的同步测试大幅提高了测试效率,且工位板具有高可扩展性,对于后期的FLASH 存储器量产化测试具有广阔的应用前景。