基于免疫算法的铁电场效应晶体管多态门设计方法

2023-10-17张立宁胡伟晨王新安崔小乐

张立宁 胡伟晨 王新安 崔小乐*②

①(北京大学深圳研究生院集成微系统重点实验室 深圳 518055)

②(鹏城实验室 深圳 518055)

1 引言

随着信息技术行业的高速发展,电子设备的功能日益复杂,对电路集成度的需求逐渐提升,集成电路(Integrated Circuit, IC)设计成本也会升高。为了解决这些问题,基于知识产权(Intellectual Property, IP)复用的设计方法越来越多地被IC设计公司使用。芯片设计者只需修改IP核模块中的部分参数即可将其重复应用于大型电路设计中,从而大大降低了设计周期和设计成本。然而,基于IP核复用的设计方法也导致行业中出现了一些侵权行为,例如IP盗用、伪造等。为了解决IP核的版权问题,业界提出了硬件伪装、水印、指纹、逻辑锁等硬件保护方案。通过在普通的电路模块中嵌入仅设计者可知的水印、指纹等硬件模块,当IP核遭到盗版时,IP设计者可以通过提取其中的水印和指纹信息来证明其原始版权。多功能电路是实现硬件水印、指纹、逻辑锁的有效方法,因为它们可以在保留电路模块原始功能的同时扩展新的功能,使硬件保护方案更加灵活。

传统的多功能电路是通过开关或多路选择器在多个独立的常规子电路之间进行选择来实现的,往往带来较大的面积开销。2001年,Stoica等人[1]提出了多态电子学,通过在同一个电路结构中嵌入两个或更多的内置功能,实现利用如温度、电源电压、外部控制电压等外部信号来完成不同逻辑功能的切换。与传统可重构电路相比,多态电路无需通过改变和重新配置电路结构即可改变电路功能。在实现相同功能的情况下,多态电路使用的器件更少,具有更紧凑的电路结构和更小的面积开销。目前,多态电路在电路自测试[2]、自适应电路系统[3]等许多领域都有所应用。

2008年,Ruzicka等人[2]基于AMIS 0.7μm CMOS工艺设计出电源电压控制的多态门。同年Starecek等人[4]提出了外部信号电压控制的多态门。2016年,Suarez等人[5]提出了一系列基于控制信号电压的多态门,包括NOR/AND门、OR/NAND门等。2018年,Wang等人[6]基于SMIC 130 nm CMOS工艺,提出了一系列基于温度控制的多态门。同年Nevoral等人[7]利用进化算法和Hspice仿真工具,基于45 nm CMOS工艺,生成了基于控制信号电压控制的完整的两功能多态门库。这些基于CMOS器件设计的多态电路的结构往往也比较复杂。新型器件,如双极器件、纳米电子结构和阻变存储器(Resistive Random Access Memory,RRAM)在设计多态电路方面的潜力也被研究人员广泛探索。2014年,Bi等人[8]提出使用具有双极性的硅纳米线场效应晶体管(SiNW FET)器件来设计多态门。2017年,Parveen等人[9]提出了使用5端口多层磁性畴壁运动(Domain Wall Motion, DWM)器件实现可重构的两输入全功能数字逻辑门。2018年,Rezaei等人[10]提出通过改变电路中RRAM的电阻值来调整多态门的功能。同年,Macha等人[11]提出利用纳米金属线间的确定性串扰实现多态门。2022年,Macha等人[12]提出了一种基于串扰 (CrossTalk,CT) 计算的新型多态电路设计方法。2023年,Karempudi等人[13]提出基于电光效应的多态逻辑门,可以用于高速可重构计算电路中。

铁电场效应晶体管(Ferroelectric Field-Effect Transistor, FeFET)是一种被广泛研究的兼具存储和计算功能的新型器件,文献[14]提出一种基于FeFET的新型存储器单元设计,该设计可以在不同的操作模式下实现高性能的存储和计算功能。FeFET近些年也常被当作神经网络的突触用于存内计算中。例如文献[15]就提出一种基于FeFET的1T1R阵列的模拟内存计算方法,用于边缘人工智能应用。文献[16]提出了铁电电容的动态紧凑模型。铁电材料具有独特的铁电性质,可以在外加电场作用下改变其晶格结构和电荷分布状态,从而实现电阻、电容等电学特性的可控调节。此外铁电材料的极化强度和介电常数也会受到温度的影响。当温度高于某一临界温度时,晶体的铁电性会消失。因此有学者提出可以将FeFET作为电路的基本单元来设计多态门,但目前还没有通用的设计方法以及较丰富的具体设计实例。因此本文将FeFET这一新器件用于多态电路的实现中,并基于文献[16]提出的模型发展出一套基于免疫算法设计的完整的FeFET多态门的算法和流程。

2 背景知识

2.1 铁电场效应晶体管FeFET

FeFET的基本结构和传统的MOSFET类似,包括源极、漏极、栅极等部分。其栅极处覆盖了一层铁电材料薄膜,可以通过调节铁电材料的极化方向来改变栅极处的电势分布,从而控制电流的流动。它具有低功耗、非易失性、快速响应、高密度、可重复写入、抗辐射性等优点。FeFET的结构与MOSFET很相似,也可以用于逻辑计算。在其栅端施加不同幅值或宽度的脉冲电压可以实现对FeFET电导的调节。这一特性与多态电路的器件对于电压的依赖性这一底层原理较为契合,因此本文选择FeFET这一新器件作为多态电路的基本单元进行研究。

2.2 免疫算法

免疫算法是一种基于人类免疫系统原理的计算方法,其核心思想是通过模拟人类免疫系统中抗体、克隆、选择和进化等基本机制来进行计算,具有自适应性、多样性、局部搜索能力强以及适应于多种问题的特点。它是一种全局优化算法,主要用于求解复杂的多目标优化问题,例如文献[17]提出基于免疫算法的多目标优化方法,该方法能够有效地处理具有许多决策变量和目标函数的复杂问题。

数字逻辑电路的传统设计方法在多态电路的设计上会受到限制。首先,多态电路和传统数字电路对一些参数的考量不同,例如温度的变化在传统数字电路设计中通常会被忽略,而在多态电路的设计中,温度可能会是一个重要的控制信号。其次,多态电路内部器件单元间的拓扑结构和单元尺寸参数与传统数字电路中规律性的参数有很大区别,通常很难靠人工设计,因此需要采取其他设计方法生成多态电路。由于多态电路的设计可以在没有设计规则的情况下进行,只需要对生成的电路进行评估和排序,若电路满足需求即可视作设计成功。这种特性使得多态电路生成的问题非常适合进化算法。遗传算法是进化算法中常用的一种,算法的基本思想与进化算法一致,常用来解决实际问题的最优解问题,以往的多态门通常是由遗传算法得到的。免疫算法和遗传算法都是基于生物学的启发式优化算法,它相较于遗传算法具有处理多峰优化问题更为有效、抗噪声能力更强、搜索速度更快以及可以更好地处理离散问题等优势。由于FeFET之前并没有应用于多态电路的设计中,缺乏一些先验条件,为了避免算法陷入局部最优从而无法得到我们想要的多态门,我们选择免疫算法这样一种全局寻优能力更强的算法作为FeFET多态门的设计算法。

3 适用于FeFET多态门设计的免疫算法

3.1 设计目标和编码方式

在使用免疫算法解决实际问题之前,需要确定算法的设计目标。针对多态门设计这个实际问题,算法的设计目标即为设计出满足要求的数字逻辑功能的电路结构,如AND/OR多态门或XOR/NOR多态门等。此外,还可以考虑包括电路中使用的器件和工艺、结构中包含的器件数量等其他要求。然后,需要将实际问题中的信息与免疫算法能够处理的字符串对应起来,这个对应的过程称为编码。在免疫算法中,选择适当的编码方式非常重要,可以更方便地表示实际问题的信息。

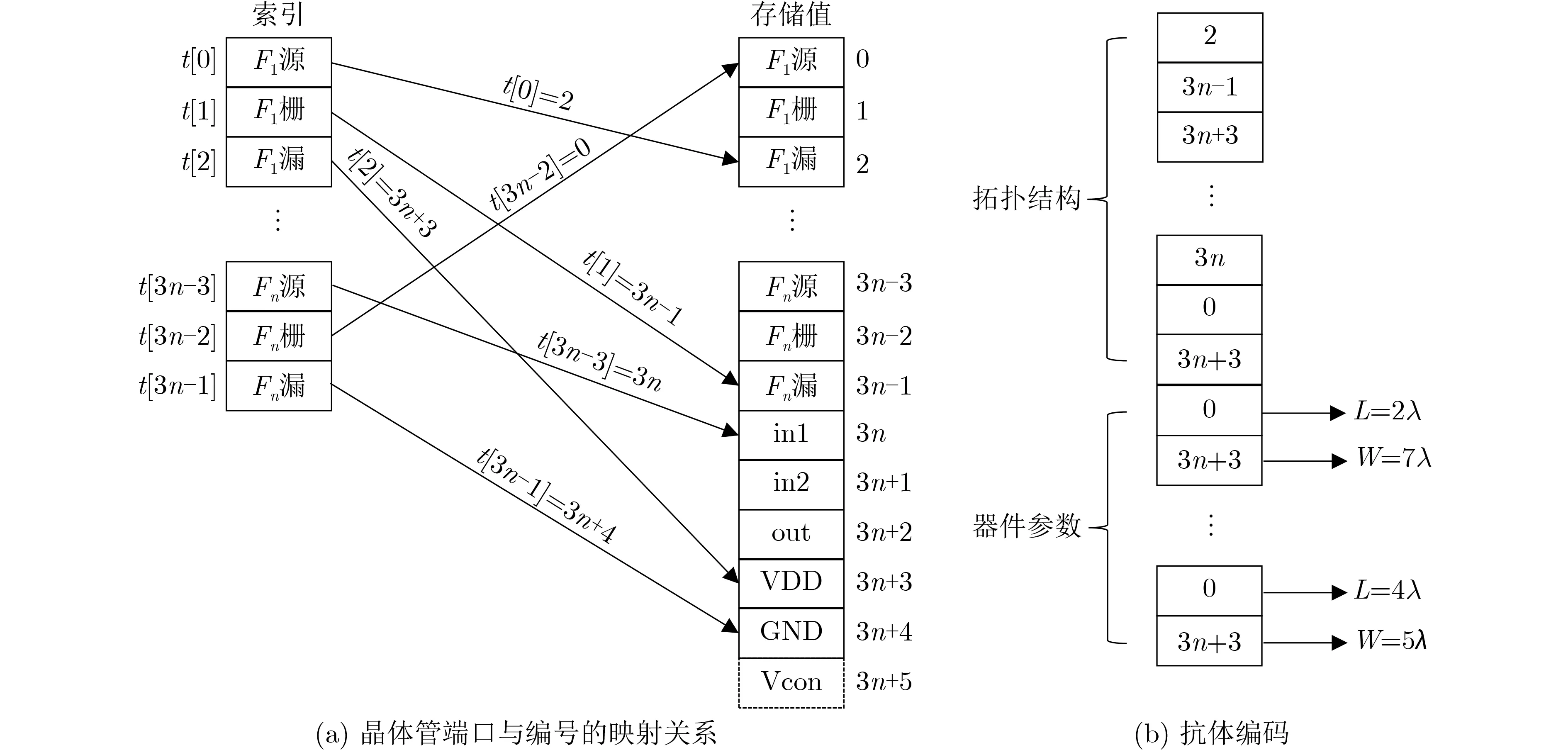

为了设计FeFET多态门,每个电路结构应当被编码以包含源极、漏极和栅极的连接关系以及沟道的长度和宽度,这些信息可以分为电路拓扑结构和器件参数两个方面。本文采用浮点编码方式进行FeFET多态门的编码。在这种编码方式下,对于一个完整的电路拓扑结构,每个端口都会与另一个或多个端口连接。如图1(a)所示,为了简化表示,将每个端口编号,并使用数组来存储端口之间的连接关系。具体地,对于所有FeFET器件的源极、漏极、栅极以及输入端、输出端、电源端、接地端和控制电压端(如果是外部控制条件下的多态门),依次进行编号,并建立一个数组,其大小为Fe-FET器件数量的3倍。通过数组的索引值和存储值的对应关系,可以表示电路中端口与端口之间的连接关系,例如,数组的索引1位置上存储的数字为12,这代表编号1对应的端口连接到编号12对应的端口上。这样,电路拓扑结构中各个端口的连接关系就被编码完成了。为了提高效率,方便表达,本文对于器件参数部分为每个晶体管的沟道宽度、长度指定特定的取值范围,使这些参数只能选取有限的分立取值,即特定工艺条件下最小尺寸的整数倍。如图1(b)所示,建立这些分立取值与有限整数集合间的一一映射关系,可实现尺寸基因的整数编码。最后将电路拓扑结构和器件参数编码的字符串连在一起便是完整的抗体编码。

图1 FeFET多态门编码方式

3.2 初始群体生成方式

免疫算法的初始群体生成是其成功应用的重要因素之一,通常有两种主要的初始群体生成方式。第1种是随机生成法,即通过完全随机的方式生成一组字符串作为初始群体。这种方式不需要对初始群体施加太多的限制条件,也无需获取先验结果,但是由于具有一定的随机性,可能会导致需要进化很多代才能出现满足设计要求的个体。另一种是通过一些先验结果来设置初始群体生成的限制条件,从而获得较小的解空间来搜索得到初始群体。这种方式得到的初始群体能够更好地满足设计目标的要求,从而提高算法的收敛性,但是也可能导致算法运行过程中易于陷入局部最优。对于FeFET多态门设计,由于缺乏先验条件,目前采用随机生成法作为初始群体的生成方式。但是,在实验基础逐渐积累的情况下,可以通过一些先验结果来对初始群体的生成方式进行改进,提高算法的收敛性和效率。

3.3 亲和度函数

亲和度(affinity)是免疫细胞与抗原之间相互作用的强度,可以用来衡量个体(如电路结构)与目标之间的匹配程度。在免疫算法中,通过亲和度函数来计算个体与设计目标之间的匹配程度。在FeFET多态门设计中,通过不同控制条件下的输入输出真值表来表示控制条件与数字逻辑功能之间的对应关系,并使用亲和度评价生成数字电路结构,以实现在不同控制条件下具有不同数字逻辑功能的电路结构。数字电路的契合程度可以通过其满足预期数字逻辑功能的程度来表示。对于一个n输入的数字逻辑门,每个数字逻辑功能包含2n个输入输出组合。为了满足设计目标中的m个数字逻辑功能,算法生成的多态门需要在m个不同的控制条件下,都有2n个输入输出组合与数字逻辑功能的真值表对应。因此,亲和度函数被设置与待选个体的真值表与设计目标的真值表在不同控制条件下的汉明距离之和相关联。亲和度函数如式(1)所示,数值越大代表个体与预期设计目标之间的契合程度越高

其中,fi为设计目标在控制条件为i时的真值表,为此待选个体在控制条件为i时的真值表。

3.4 计算抗体浓度和激励度

抗体浓度(density)是一个解与集合中其他所有的解当中距离比较近(或者说比较相似)的解的个数,再除以集合中解的总数,如式(2)所示

其中,N为种群规模,S(abi,abj)表示抗体间的相似度,可由式(3)表示

其中,a bi是 种群中的第i个 抗体,δs为相似度阈值,aff′(abi,abj)是 抗体i和 抗体j的亲和度,要注意区分这里的亲和度是抗体与抗体之间的,而前面的亲和度是抗原与抗体之间的。本文使用浮点数编码的方式,因此可通过抗体向量之间的欧氏距离来计算抗体间的亲和度,公式如式(4)所示

其 中, a bi,k和a bj,k分 别 为 抗 体i的 第k位 和 抗 体j的第k位;L为抗体编码长度。

抗体激励度是对抗体质量的最终评价结果,需要综合考虑抗体亲和度和抗体浓度。亲和度值大、浓度低的抗体会得到较大的激励度。公式如式(5)所示

其中, a,b 为常数,可以根据实际需要进行调整。一个解的激励度越大,那么就越优先选。

3.5 免疫操作

免疫处理包括免疫选择、克隆、变异和克隆抑制。具体内容如下:

(1) 免疫选择会根据抗体的激励度确定选择哪些抗体进入克隆选择操作,本文通过激励度函数值对抗体进行排序,然后根据排序结果选择一定比例的抗体进行克隆操作。

(2) 克隆操作会根据免疫选择的排序选择优秀的抗体复制一定次数,产生一批新的抗体。克隆的过程中,需要设置复制因子,即每个优秀抗体被复制的次数。核心思想是基于优秀抗体的多次复制,以提高种群中优秀抗体的数量,并通过后续的进化过程来进一步优化解的质量。

(3) 变异操作对克隆得到的抗体进行变异以产生新的解,从而增加种群的多样性和搜索范围。对于FeFET多态门设计,由于抗体中同时包含电路拓扑结构和电路参数两部分信息,因此分别对电路拓扑结构部分的染色体和电路参数部分的染色体进行变异操作,以避免染色体不同部分的数据发生混淆。我们在抗体中随机选择某一段并进行随机修改以生成新的个体,然后将生成的电路拓扑结构部分的染色体与电路参数部分的染色体整合即得到新个体的染色体串。

(4) 克隆抑制用于对经过变异后的克隆体进行再选择。将克隆操作的源抗体与克隆体经变异算子作用后得到的临时抗体群共同组成一个集合,抑制亲和度高的抗体,保留亲和度低的抗体进入新的抗体种群。由于克隆变异操作的源抗体是种群中的优质抗体,而克隆抑制操作的临时抗体集合中又包含了父代的源抗体,因此在免疫操作中隐含了最优个体保留机制。

3.6 种群刷新和电路结构检测

种群刷新用于对免疫操作后新得到的抗体种群进行刷新。对于实际的多态电路问题,为了保证生成的每个电路拓扑结构都是完整且合理的数字逻辑门,本文对新生成的电路的拓扑结构进行特殊端口、路径完整性和连接合理性3方面的检测以进行种群刷新。具体来说,需要检测输入端、输出端、电源端和接地端这些特殊端口是否连接到电路中的器件上,以保证每个特殊端口都连接到电路中;检测电路中的器件的每一个端口是否连接到电路中的其他端口上,以保证不存在悬空节点和连接不合理的情况;检测每个电路器件的所有端口是否同时连接到同一个端口上,以及是否全部连接到特殊端口上,以确保每个电路器件都正常连接到电路中。通过这些检测条件可以保证每个新生成的电路结构都是完整且合理的数字逻辑门,从而提高算法的效率和准确性。

3.7 用于多态电路设计的免疫算法流程

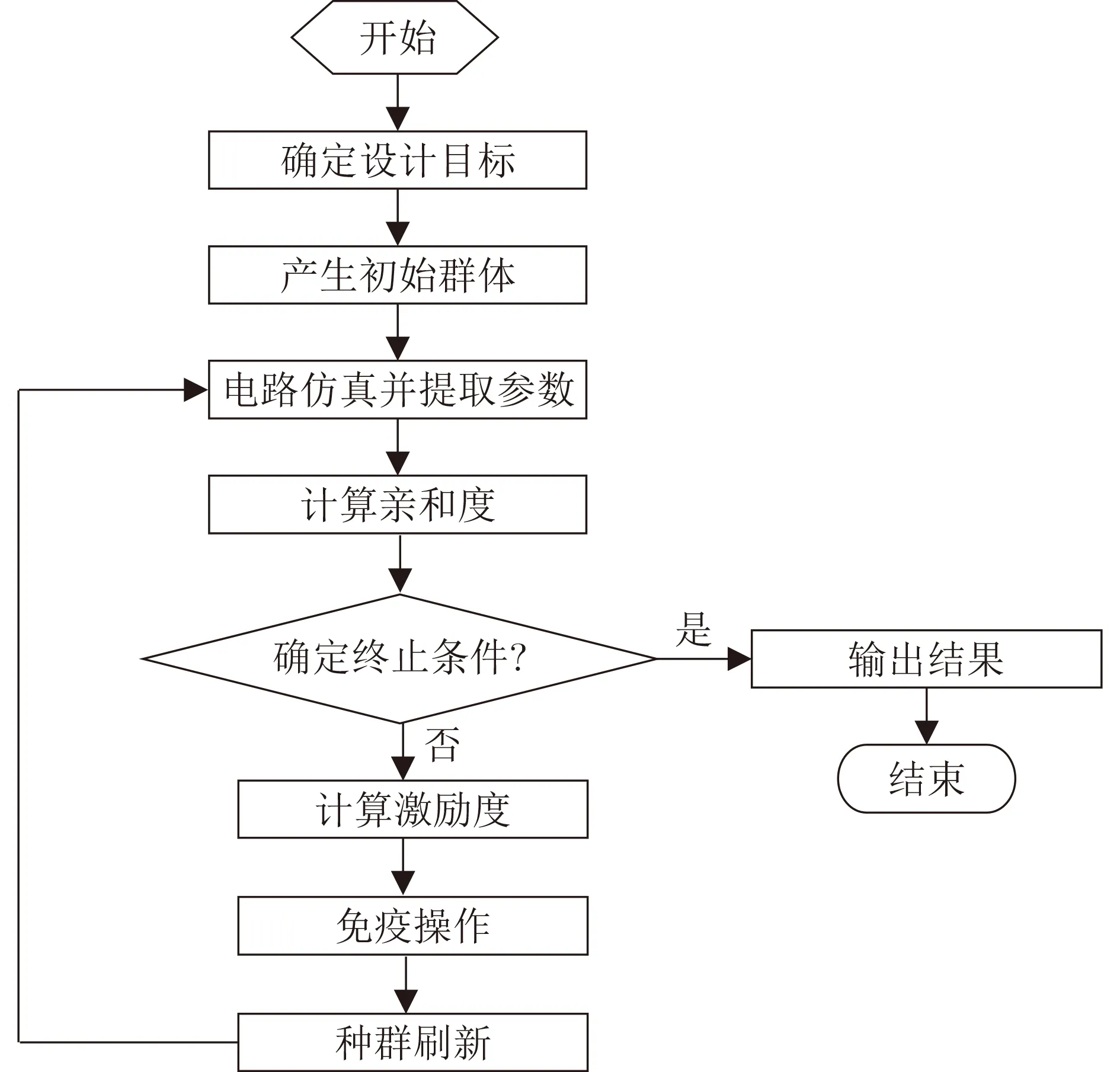

基于以上改进,使用C++语言和Hspice仿真工具实现了可以用于设计FeFET多态门的免疫算法。算法的基本流程如图2所示。与一般的免疫算法流程相比,区别主要在于加入了电路模拟仿真和仿真数据提取过程,该过程利用Hspice仿真工具操作完成,其余步骤均为C++语言运行。

图2 适用于FeFET多态门设计的免疫算法流程

基于以上实现的FeFET多态门设计算法的伪代码如算法1所示。算法的主要运行步骤如下:

算法1 用于FeFET多态门设计的免疫算法

(1) 设置每个父代生成子代的数量、群体数量最大值、进化代数的最大值、预期目标在不同控制条件下的输入输出真值表、较宽松的亲和度阈值、相似度阈值、变异率、克隆个数等算法初始参数。设置预期的FeFET器件个数和实现功能切换的控制条件等多态门初始参数。

(2) 将这些数字逻辑门的拓扑结构和电路参数进行编码,生成初始群体的抗体作为第1代父代。

(3) 在不同控制条件下,通过Hspice软件对当前父代的所有待选电路网表进行仿真。通过Hspice的仿真结果提取每个电路网表在不同控制条件下的输出电压值,并判断得到输入输出真值表。

(4) 计算当前群体中的每个个体的亲和度。

(5) 计算抗体浓度和激励度。

(6) 进行免疫处理,包括免疫选择、克隆、变异和克隆抑制,之后生成新一代抗体。

(7) 通过电路结构检测的方式进行种群刷新。

(8) 判断是否达到算法停止条件。若已达到,则结束算法,并保留当前幸存个体集合作为输出结果;若仍未达到,则重复步骤(3)~(8),直到达到算法停止条件。

4 FeFET多态门设计实例

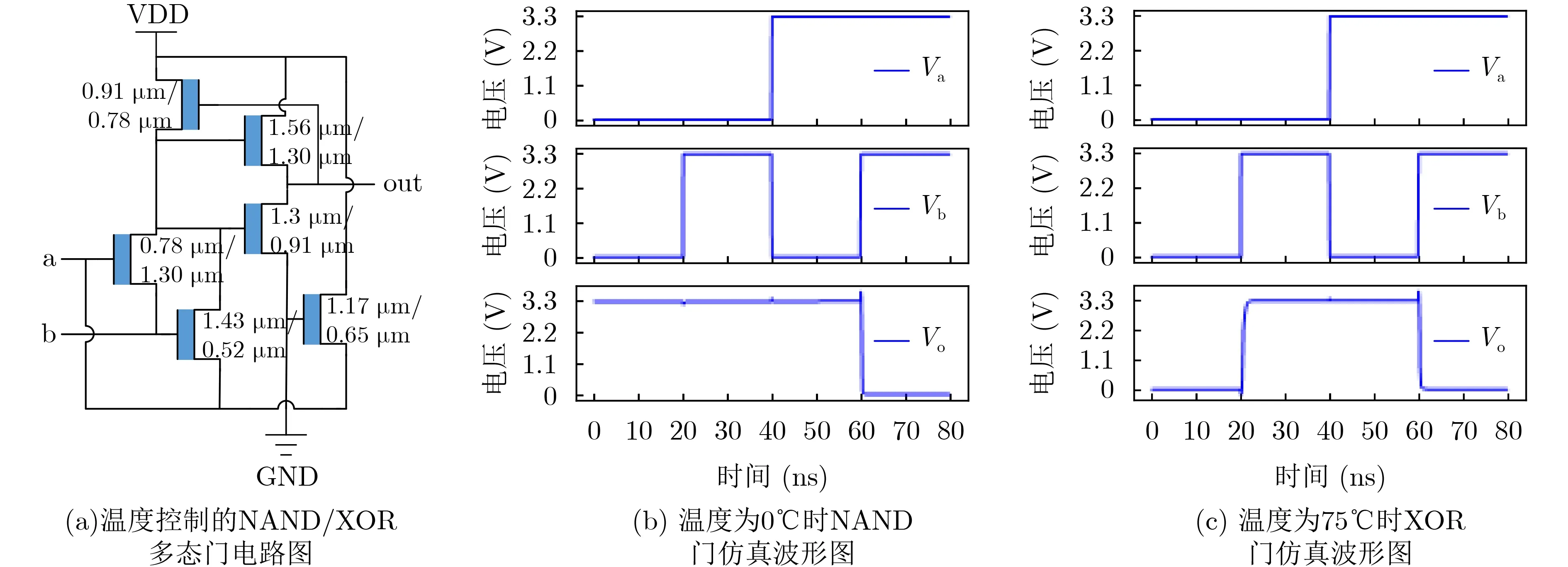

在0.13 μm CMOS工艺和铁电电容模型下,以生成NAND/XOR门为例说明改进后的免疫算法的具体实验过程。该算法旨在生成一个FeFET多态门,该门能够在不同的温度下切换其实现的功能,包括NAND逻辑和XOR逻辑。在实验中,使用了一个包含6个FeFET器件的随机门电路结构作为初始父代。本文设置了每代群体的个体数量最大值为10 000。在幸存个体数量Num_sur少于20个时,为每个父代生成500个子代;在Num_sur多于20个时,每个父代均摊生成floor(10 000/Num_sur)(floor()表示向下取整)个子代。本文将免疫算法的最大进化代数设为10,将免疫算法的终止条件设置为两个方面:当进化代数达到最大值10,或者待选电路能够在两个环境下实现NAND逻辑功能和XOR逻辑功能时,算法结束运行。首先通过编码初始父代的拓扑结构和尺寸信息得到初始父代的抗体群。对群体中的所有抗体进行解码,得到每个抗体对应的电路的拓扑结构和尺寸信息,并生成对应的Hspice仿真软件的仿真文件(.sp文件)。调用Hspice仿真软件,利用Hspice仿真软件的sweep语句,在一定的范围内扫描控制条件的值,对每个电路进行仿真,并获取存储输出结果的.lis文件。当控制条件设定为温度时,设置扫描范围为–25~150°C,间隔为25°C。由于输出文件中只能获取输出端的具体电压值,因此还需要利用C++语言读取结果文件,并将输出端的电压值与电源电压进行比较得到输出端的逻辑值。结合输入端和输出端的逻辑值,分别得到每个电路在不同控制条件下的真值表。将每个电路的全部真值表与预期目标的真值表对比,计算出每个待选电路结构与预期目标之间的汉明距离,继而得到每个待选抗体的亲和度值。然后计算抗体浓度和激励度,对群体中的抗体进行免疫操作得到新的抗体群。之后对新生成的抗体群进行电路结构检测,这样就得到了下一代的抗体群。接着继续重复进行以上过程,直到算法运行结束。我们这里使用的硬件平台参数为:CPU型号:Intel Core i5-9500,频率:3.00 GHz,内存:16 GB。在这个硬件平台下对于种群中的1个个体1次迭代的时长约为0.48 s。当设置种群规模为10 000时,平均迭代次数为9.2次,总运行时长为44 160 s。图3为生成的温度控制的NAND/XOR门,此多态门分别在温度为0°C和75°C下实现NAND和XOR逻辑功能。

图3 温度控制的NAND/XOR多态门(0/75°C)的电路图和仿真波形图

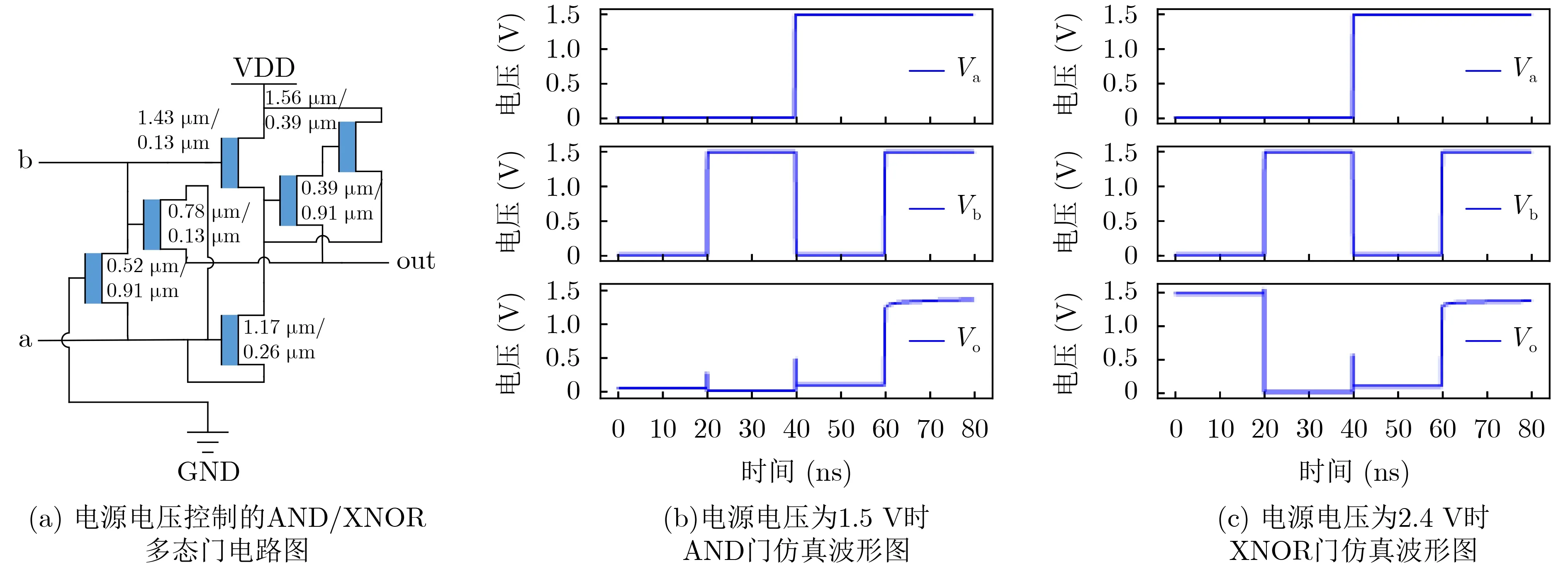

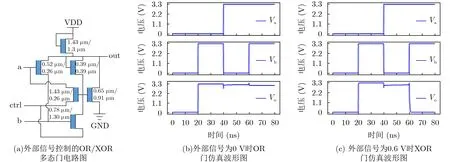

同理,设置控制条件为电源电压,利用Hspice仿真软件在1.2 ~3.3 V电压范围内以0.3 V为间隔扫描。利用FeFET多态门设计算法运行得到AND/XNOR门如图4所示,此多态门分别在电源电压为1.5 V和2.1 V电压下实现AND逻辑功能和XNOR逻辑功能。设置控制条件为control端的电压值,利用Hspice仿真软件在0~3.3 V电压范围内以0.3 V为间隔扫描。运行得到OR/XOR门如图5所示,分别在外部信号端ctrl为0 V和0.6 V电压下实现OR逻辑功能和XOR逻辑功能。此外,本文的设计方法不仅可以生成两功能多态门,对于多功能(功能数大于3)多态门也同样适用。图6为温度控制的3功能FeFET多态门电路结构图和仿真波形图,分别在温度为–25°C, 75°C, 100°C下实现NOR, AND, XNOR逻辑功能。表1列出了利用该平台生成的部分多态门实例,包括了这些多态门的功能、控制条件和包含的器件数量等信息。

表1 利用免疫算法得到的FeFET多态门

图4 电源电压控制的AND/XNOR多态门(1.5 V/2.4 V)的电路图和仿真波形图

图5 外部信号控制的OR/XOR多态门(0 V/0.6 V)的电路图和仿真波形图

图6 温度控制的NOR/AND/XNOR多态门(–25°C/75°C/100°C)的电路图和仿真波形图

5 结论

FeFET作为新型器件被认为可用于多态电路的设计,但缺少通用及完整的设计流程和方法。本文提出基于免疫算法的多态门设计流程,利用C++语言和Hspice仿真工具构建了完整的FeFET多态门设计平台。本文详细说明了该设计平台的算法和设计流程,并运用该流程实现了温度、电源电压和外部信号控制的FeFET多态门的具体实例。这些实验结果表明了本文提出的设计平台的有效性,支持FeFET可作为新器件用于多态门的设计中。