基于铁电晶体管的存储与存算一体电路

2023-10-17李泰昕杨华中李学清

刘 勇 李泰昕 祝 希 杨华中 李学清

①(芯昇科技有限公司 北京 100032)

②(清华大学电子工程系,北京信息科学与技术国家研究中心 北京 100084)

1 引言

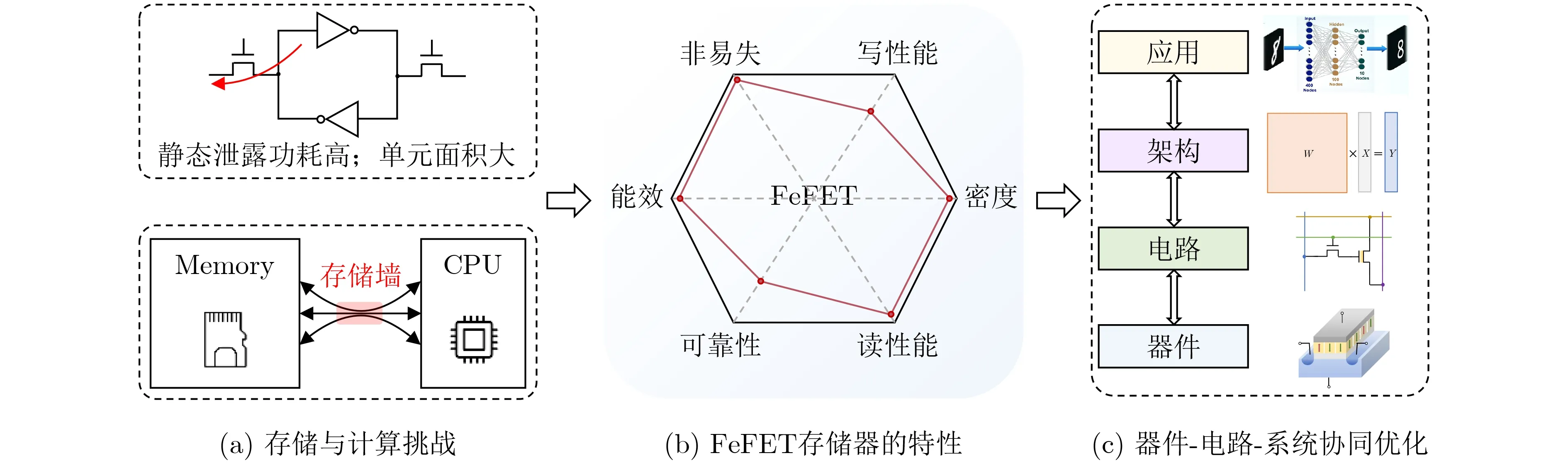

近年来,随着物联网、人工智能等技术的发展,以数据为中心的智能计算成为新的计算范式[1]。在智能计算时代中,数据密集型应用对片上存储与计算的能效、密度以及性能提出了重要挑战[2],例如在智能驾驶领域,算力需求为每秒运算2×1013~4×1014次,对系统的可靠性要求较高,且随着芯片工艺的不断演进,未来终端向着多样化、智能化、复杂化的方向发展[2]。然而,一方面,基于互补金属氧化物半导体(Complementary Metal Oxide Semiconductor, CMOS)工艺的静态随机存取存储器(Static Random-Access Memory, SRAM)具有较大的静态功耗和单元面积,限制了存储的能效与密度[3]。另一方面,传统的冯·诺伊曼 (Von Neumann)架构存储与计算分离,在处理密集数据时需要频繁数据搬移,极大限制了计算的性能与能效,即“存储墙”问题[1]。如图1(a)所示,这两个瓶颈阻碍了高能效、高性能的物联网边缘设备的发展。

图1 基于FeFET的存储与CiM电路的背景与挑战[12]

目前,CMOS工艺尺寸微缩正在不断减缓,这一趋势在存储器上尤为显著,例如台积电的N3E工艺下SRAM的单元面积相比5 nm工艺没有减小[4]。在这一背景下,阻变存储器 (Resistive Random-Access Memory, RRAM)[5,6]、自旋转移矩磁存储器(Spin-Transfer Torque Magnetic Random-Access Memory, STT-MRAM)[7,8]、相变存储器 (Phase Change Memory, PCM)[9]和铁电晶体管 (Ferroelectric Field Effect Transistor, FeFET)[10–12]等新型非易失存储器 (Nonvolatile Memory, NVM)为上述瓶颈问题的解决提供了新的设计空间。这些NVM能够消除SRAM的静态泄露功耗,提高存储密度;同时可以实现高并行度的存内计算 (Compute-in-Memory, CiM),显著减少数据搬移的消耗,突破“存储墙”瓶颈。

在新型NVM中,如图1(b)所示,FeFET具有极低的写功耗、快速的读取操作以及与CMOS兼容的高微缩能力等特点,这使基于FeFET的存储与CiM电路在密度和能效上的优势尤为突出。与此同时,FeFET仍存在工艺成熟度、可靠性和寿命上的不足[12]。因此,基于FeFET的存储与CiM电路需要跨层次的协同设计与优化,从而利用FeFET的新型存储特性实现更高能效的片上存储和CiM架构,提高FeFET在存储与CiM应用中的可靠性,以高效的存储与智能的计算支持数据密集型应用在边缘端的部署。

本文其余部分的组织结构如下:第2节回顾了FeFET器件的发展历程;第3节主要介绍FeFET器件的基本背景,包括FeFET的结构、基本操作、建模以及同其他存储阵列的对比分析;第4节阐述近期基于FeFET的存储器在电路结构创新和访存机制优化上的主要进展;第5节介绍FeFET在CiM中的应用,特别是在非易失计算、存内逻辑计算(Logic in Memory, LiM)、矩阵向量乘法 (Matrix Vector Multiplication, MVM)以及内容寻址存储器(Content Addressable Memory, CAM)4类不同应用中的设计与优化;第6节展望基于FeFET的存储与CiM电路的前景与挑战;第7节对本文进行总结。

2 铁电晶体管器件发展历程

图2展示了FeFET器件的发展历程。1920年,Valasek[13]首次发现铁电性的存在。此后,贝尔实验室在1957年首次提出FeFET的概念并注册专利[14]。1963年,Moll和Tarui[15]报道了首个FeFET器件,使用了三甘氨酸硫酸盐 (TGS)材料实现了25%的电阻变化。自20世纪70年代以来,层状铁电钙钛矿薄膜材料的发现大幅改善了铁电材料的控制能力和存储稳定性[16],而薄膜生长技术的进步则降低了FeFET的工艺制造难度[17],从而极大促进了FeFET器件的发展。1974年,Wu[18]首次报道了金属-铁电-半导体 (Metal-Ferroelectric-Semiconductor, MFS)结构的FeFET器件,实现了同平面硅工艺相兼容。

图2 FeFET器件的发展历程及最新进展[11-30]

此后,铁电器件的相关研究大量涌现,其中铁电随机存取存储器 (Ferroelectric Random-Access Memory, FeRAM)因其较好的存储稳定性和较低的工艺难度受到了广泛关注。1988年,Ramtron公司首次基于锆钛酸铅材料 (PZT)和后道集成工艺 (Back-End-of-the-Line, BEOL)制造了FeRAM芯片,并在1993年推出了首个商用的FeRAM产品[19]。然而,此时FeFET的发展却较为有限。钙钛矿铁电体在前端工艺中与硅热力学不相容,导致FeFET工艺集成困难;其较大的去极化场导致保持时间有限;且基于钙钛矿的FeFET无法微缩至130 nm以下的工艺节点。这些因素共同限制了FeFET的发展和落地[12,19]。

2011年,Böscke等人[20]首次发现HfO2薄膜的铁电性,这一发现对FeFET的发展具有里程碑意义。HfO2于2007年由英特尔公司引入到CMOS制造工艺中,被广泛用作高介电常数金属栅极(High-K Metal Gate, HKMG)MOSFET的栅极电介质,因此,基于HfO2的FeFET具有CMOS兼容的微缩能力,且工艺集成难度大大下降。此外,基于HfO2的FeFET同样具有稳定的长期保持特性和更大的存储窗口 (Memory Window, MW)[12]。这些HfO2所带来的优异特性大大促进了FeFET器件及其电路、应用的研究和发展。

如图2所示,对更高性能FeFET的器件研究正在不断推进。Dünkel等人[21]在2017年首次报道了基于22 nm FDSOI (Fully Depleted Silicon on Insulator)工艺的FeFET,实现了10 ns的写入速度和105次循环的耐久性,展示了其微缩能力和应用前景。最新的研究显示,FeFET的写入速度能够低于5 ns[22],开关比高达107以上[23],保持时间超过10年[24],工作寿命超过1012次循环[25]。在多值存储能力上,已有研究报道了具有8 V MW[26]以及能够存储10个稳定状态[27]的FeFET器件。除此之外,一些学者尝试探索不同结构的FeFET,例如3D垂直FeFET[11]、纳米线FeFET[28]、鳍式FeFET[29]以及全环栅FeFET[30]等。

3 铁电晶体管器件背景

为帮助读者更好地理解FeFET器件,本节介绍了FeFET的结构和基本操作,回顾了FeFET器件建模的相关工作,并讨论了FeFET同SRAM、嵌入式动态随机存取存储器 (embedded Dynamic Random-Access Memory, eDRAM)、嵌入式闪存(Embedded Flash, eFlash)和其他新型NVM的特性对比。

3.1 铁电晶体管结构和基本操作

图3(b)展示了被广泛研究的金属-铁电-绝缘层-半导体 (Metal-Ferroelectric-Insulator-Semiconductor, MFIS)FeFET结构,该结构在晶体管的栅极堆叠中嵌入铁电材料作为铁电层,如图3(a)所示,在施加电场时铁电层的极化状态同电场强度呈滞回特性,其极化状态在移除电场后仍能够保持不变。

图3 FeFET的结构和特性

FeFET的工作原理在于铁电层可以通过极化电荷对沟道施加场效应,从而控制晶体管的阈值电压。对于N型FeFET,当施加正栅源电压 (VW)时,铁电层中的铁电畴将向正极化状态翻转,自漏极和源极吸引电子到沟道,导致电导率增加、器件的阈值电压减小,此时FeFET为低阻状态 (Low-Resistance State, LRS)。类似地,施加负栅源电压将使铁电畴翻转到负极化状态,由衬底提供的空穴增加,使阈值电压增加,此时FeFET为高阻状态(High-Resistance State, HRS)。如图3(c)所示,这一写入过程具有滞回特性,且可以通过调整写入脉冲的幅度、宽度和次数实现FeFET的多值存储。由于写入操作中漏极与源极的电压可以相同(例如均设为0 V),FeFET实际上具有容性的写入负载,写操作功耗极低。

读取FeFET的本质是检测器件的阈值电压,一般通过测量特定读取电压 (VR)下晶体管的漏源电流 (IDS)来实现。当栅源电压 (VGS)被设定为合适的VR时,如图3(c)所示,打开和关闭的晶体管将分别流过较大和极小的电流,可以利用灵敏放大器(Sense Amplifier, SA)感测IDS,读出存储的数据。

3.2 器件建模

为实现对基于FeFET的电路更高效的设计与分析,一些工作对FeFET建立了电路模型以描述其器件特性。文献[31]提出了Landau-Khalatnikov(LK) FeFET模型,首次实现了FeFET的SPICE建模。然而,LK模型将铁电层近似为仅含有单个铁电畴,无法描述历史状态的影响和部分极化的特性。2018年,Ni等人[32]提出了基于多畴Preisach理论的FeFET建模。该模型引入了多个独立铁电畴的物理描述,能够准确刻画FeFET的MW随写入脉冲幅度、宽度和历史状态的变化,以及部分极化翻转对应的中间状态。文献[33]则基于Monte Carlo框架进一步提出了一种全面、统一的FeFET模型,能够捕获所有FeFET的基本行为,包括器件性能随尺寸微缩的变化、极化翻转的统计随机性、历史累积效应和多值存储特性。为更好地指导存储器的设计,文献[10]在Monte Carlo模型的基础上加入了对源极和漏极浮空的支持。这些FeFET模型为后续的器件和电路设计提供了指导和支撑,极大促进了基于FeFET的电路与应用的发展。

3.3 与其他存储阵列的特性对比

表1总结了不同存储器件的关键参数和性能指标对比。其中,SRAM和eDRAM具有极为优秀的读写性能,被广泛用作片上缓存。其可靠性和耐久性很好 (>1016次循环),但静态泄露功耗和刷新功耗极高,同时具有较大的单元面积 (≥40 F2)[34,35]。eFlash则是目前使用最为广泛的NVM,具有很高的开关比,但其写入电压很高 (10 V左右)、写入时间较长(ms量级左右),同时寿命较短 (104~105次循环)[36]。

表1 不同存储阵列的关键参数和性能指标对比

在这些成熟的存储器之外,新型NVM的发展带来了新的机遇。它们兼具较快的读写速度、较高的密度和非易失特性,能够满足数据密集型应用的需求。其中,RRAM, STT-MRAM和PCM均为阻性器件,在写入时会产生较大的直流电流,写入功耗较高 (一般在pJ量级以上),且开关比较小[5–9,37];FeRAM则与eDRAM具有类似的读破坏性[38];相比之下,FeFET具有显著优于其他NVM的极低写入功耗(~10 fJ),写入速度适中 (<10 ns),但可靠性和耐久性较差,且尚未实现量产[1,21,25]。GF 22 nm工艺的FeFET阵列中的测试结果显示,在3.5 V,10 ns的写入脉冲下,FeFET在超过105次循环后MW接近于0 V[21];这与器件级测试结果 (>1012次循环[25])相差较大,可见FeFET阵列级的工艺成熟度仍然不高。

4 基于铁电晶体管的存储器设计

作为新型NVM器件,FeFET三端器件的特性和同晶体管类似的操作模式为存储器电路结构的创新与优化提供了更大的设计空间,独特的读写特性、容性负载和多值存储特性则可以用于实现和优化新型访存机制。此后的叙述中如无特殊说明,均将FeFET的HRS视为存储状态“0”,LRS视为存储状态“1”。

4.1 铁电存储器电路结构创新

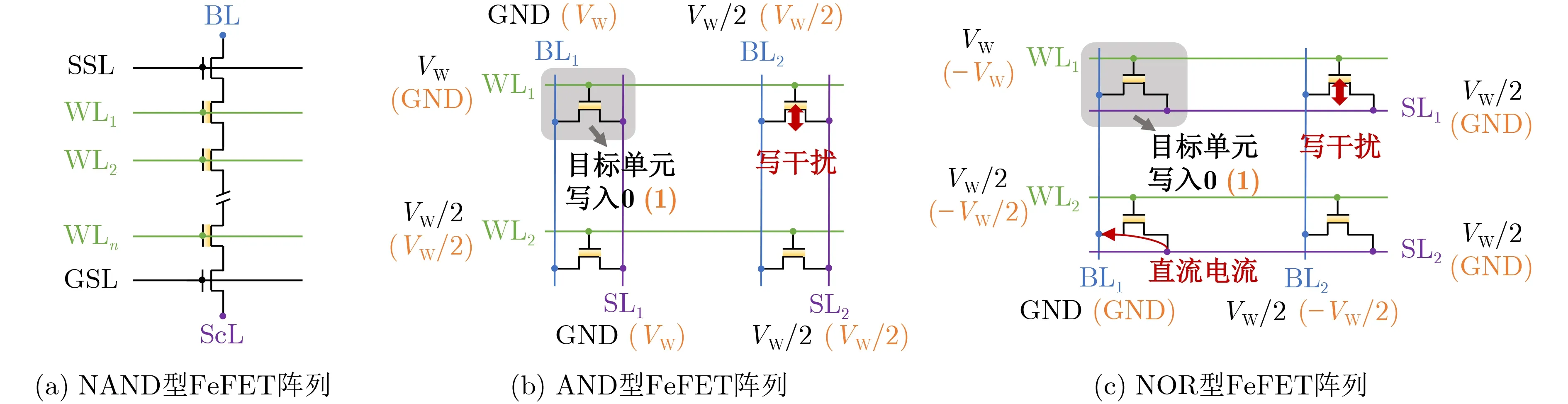

4.1.1 1T AND铁电存储器阵列

1T/C的FeFET存储阵列由于密度最高而广受关注。文献[39]在2001年首次探索了FeFET在3种1T/C典型结构中的应用,包括NAND型、AND型和NOR型。如图4(a)所示,由于位线同单元的接触更少,NAND型阵列结构的单元面积最小,但Fe-FET却不完全适用。这主要是因为NAND型阵列在读取时需要令未被访问的晶体管导通,此时所需的VGS较大,在器件本身MW偏小时容易产生严重的读干扰。

图4 FeFET在3种1T/C典型存储阵列结构中的应用[39]

在1T AND型阵列中,FeFET的源极、漏极与平行的BL,SL相连,栅极与垂直的WL相连。图4(b)展示了1T AND FeFET阵列的VW/2偏置写入策略。由于AND型阵列中同一行共享WL,且写入不同状态的WL电压不同,因此需要首先将整行写到LRS,再对特定单元写入HRS。

4.1.2 1T NOR铁电存储器阵列

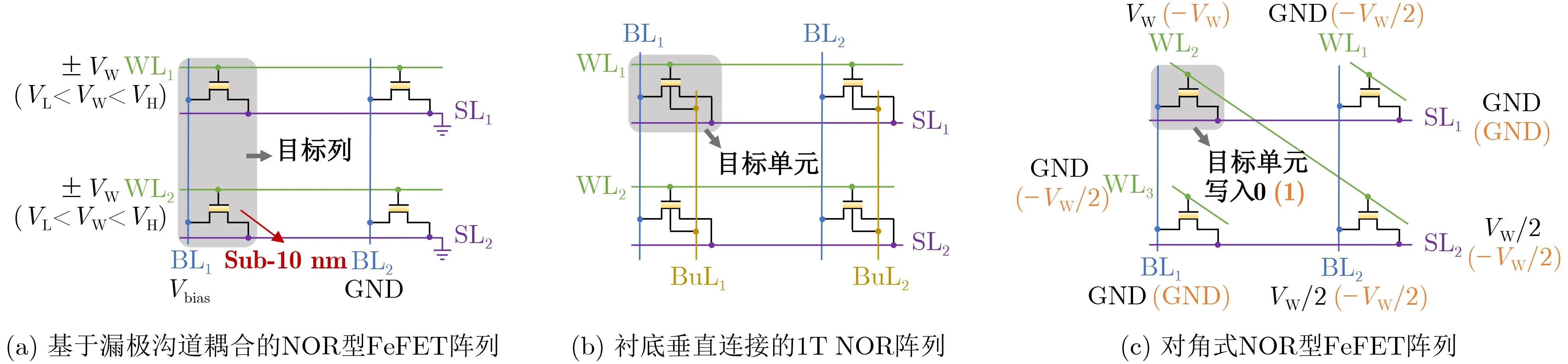

传统1T NOR FeFET阵列如图4(c)所示。在写入过程中,目标单元和半选择单元的FeFET在具有VGS偏置的情况下,源极和漏极电压可能不相同,产生很大的直流电流和功耗。由于共享WL和SL, 1T NOR FeFET阵列同样需要两步写入。为了提高写入性能,Sharma等人[40]在2018年提出了一种新的写入策略,如图5(a)所示。在栅长为5 nm的FeFET器件中,该工作发现漏源电压 (VDS)的增加将使其MW和VW减小,这被称为漏极沟道耦合效应。因此,可以通过施加不同的VDS并精确控制VW来写入特定单元。该策略能够实现单步写入,但漏极沟道耦合效应仅在栅长低于10 nm时较为明显,因此适用性很差。

图5 不同改进的NOR型FeFET阵列的写入操作[10,39-41]

面对能效挑战,文献[41]提出了名为C-AND的阵列结构和写入策略,其中同一列FeFET的衬底被连接到纵向的BuL上,如图5(b)所示。由于所有晶体管的源极和漏极始终接地,C-AND消除了源漏电流,显著提高了能量效率。然而,该策略无法写入LRS[42],这是因为FeFET导通时沟道的电位与源极、漏极一致 (0 V),铁电层两侧的实际电压差仅为VW/2,不足以实现极化状态的翻转。在此基础上,文献[42]提出将漏极和源极置于浮空状态,从而在提高能效的同时正确写入LRS。然而,由于该策略写入HRS时要求衬底接入负电位,衬底提供空穴的能力不足,会引入写入速度的下降和不对称性。

进一步地,Xiao等人[10]提出了整块擦除再编程的写入策略和对角式1T NOR阵列结构。在整块擦除再编程的写入策略中,对整个阵列首先写入LRS,再对特定单元写入HRS,从而避免出现直流电流。但特别值得注意的一点是,这一说法并不准确。该策略虽然不能对特定单元写入LRS (否则同一行单元的VGS均等于VW),但能够对特定行写入LRS而不影响其他存储单元的状态,因此只需整行擦除再编程即可。图5(c)展示了对角式的1T NOR阵列,通过将WL对角线放置使被选择单元的源极和漏极保持电压相同。该阵列能够同时实现较低的写功耗和较高的写速度,但其面积增加到了传统1T NOR阵列的3.5倍。

4.1.3 2T/C和3T/C铁电存储器阵列

由于同一行FeFET的栅极相互连接,1T/C FeFET存储器无法避免读写干扰。为进一步提升可靠性,George等人[43]在2016年最早提出了栅极选通的2T/C结构,如图6(a)所示。该单元增加了一个额外的MOSFET (T1)与FeFET (M1)的栅极相连,从而避免了读写干扰的影响,同时可以实现整行数据的单步写入。基于LK FeFET模型,该工作进一步讨论和优化了FeFET器件参数。如图6(b)所示,铁电层厚度 (TFE)最为关键,会直接影响Fe-FET的滞回曲线,TFE大于1.9 nm时FeFET才具备滞回特性。随着TFE的增大,MW和保持时间提高,可靠性增强;但同时滞回曲线变宽,VW提升,写入的速度和能效下降。此外,器件尺寸对Fe-FET的影响主要在于电流驱动能力,进而影响读取的速度和功耗。该工作选用的是宽度和长度分别为65 nm和45 nm的FeFET器件。测试结果表明,这一设计的写入功耗比FeRAM下降了67.9%。但同时,该单元需要引入负写入电压,实际电源电压高达2VW,导致系统唤醒时能耗较高。

图6 2T/C和3T/C的FeFET存储单元[43,44]

为了避免负电压的引入, Li等人[44]提出了一种源极选通的2T/C结构和3T/C结构。如图6(c)所示,在源极选通的2T/C结构中,FeFET (M1)与MOSFET (T1)串联连接,采用与此前1T FeFET阵列相似的两步写入操作,但T1的加入消除了写干扰;同时采用了电压域读取操作,消除了读取时的直流电流,从而具有更高的能效。3T/C的单元电路结构如图6(d)所示,其读写操作与源极选通的2T/C单元类似。同栅极选通的2T/C结构相比,这两种单元电路结构将写入能效和速度分别提高了52%和44%;同时对电源电压的要求更低,在系统唤醒时需要的能量更少。表2总结了上述各种结构的FeFET存储阵列特性对比。

表2 不同结构的FeFET存储阵列特性对比

4.2 铁电存储器访存机制优化

4.2.1 1T AND铁电存储器阵列的不同写入策略

Ni等人[45]探讨了1T AND FeFET阵列在不同写入策略下的写干扰问题。在VW/2偏置策略中,仅半选择单元受到VW/2的写干扰电压;而在VW/3偏置下,未被选择的互连线配置为VW/3或2VW/3,此时所有单元均受到VW/3的写干扰电压。测试表明,写干扰对于FeFET阈值电压的影响主要体现在极化翻转和电荷捕获两种机制上。在VW/2偏置下,正干扰电压使HRS FeFET极化翻转进入LRS,导致读取该单元时出错;而在VW/3偏置下,负干扰电压和电荷捕获机制导致LRS FeFET的阈值电压进一步降低,关闭时泄露电流增加,因而读取同一列HRS单元时出错。为提高存储阵列的可靠性,可以降低缺陷密度来抑制电荷捕获效应。此外,优化参考电流的选取和采用高增益、低输入偏移的SA同样能够减少读错误。

4.2.2 基于FeFET的对称存储器

对称存储器可以从行、列两个维度读取和写入数据,从而加速矩阵计算和数据库访问等应用。然而,基于SRAM和RRAM的对称存储器密度低、能耗大,FeFET灵活的3端结构和极低写入功耗恰好可以解决上述问题。由此,文献[46]最早提出了基于FeFET的4T/C和5T/C的两种对称存储器单元电路。如图7(a)所示,在4T/C单元中,FeFET (M1)的栅极、源极和漏极分别与MOSFET (T1, T2和T3)连接。打开T1, T2和T3,将WBL设为合适的VR后,对RWL或SL施加Vbias即可按行或按列读取。然而,由于写入时WBL被同一列的单元共享,该设计不能在单个周期内实现整列的写入。5T/C单元在此基础上进一步改进,增加了一个同T2对称的MOSFET (T4),可以打开T1, T3和T4并对WWL2施加电压从而实现按列写入,如图7(b)所示。然而,4T/C和5T/C的单元面积仍然较大,存储密度较为受限。

为进一步提高密度,Wu等人[47]提出了3T/C的FeFET对称存储器,如图7(c)所示。相较于此前的5T/C设计,该电路舍弃了与FeFET漏极和源极相连的两个晶体管,能够同时实现按行和按列读写操作,具体操作与5T/C单元类似。结合对写入脉冲幅度与宽度的优化,3T/C设计在矩阵计算应用中访存次数比普通存储器减少了87%,实现了相较于5T/C单元1.67倍的密度提升和约20%的能效和速度提升。

4.2.3 MLC FeFET存储器的优化

MLC (Multi-Level Cell) FeFET的概念在2015年被首次提出[48],能够在每个单元中存储多个比特,显著提高存储密度。然而,一方面,MLC的写入一般需要编程-验证的操作以准确存储目标状态,这大大增加了写入的功耗和延时;另一方面,MLC不同状态的读取电流差异较小,为SA带来了额外负担。

针对这些挑战,文献[49]提出了3种优化方法以缓解上述问题。其一,考虑到不同应用对状态分布的不同需求,文献[49]提出在存储和CiM应用中分别采用线性和指数的映射方式,从而实现更高的精度和更低的外设功耗。其二,在FeFET的IDS过小以致原有的读取电压下SA难以感测时,自适应选取更高的读取电压以增大电流,将能够观测的状态数增加了58%。其三,基于对器件特性的认识,动态预测选择相应写入脉冲进行编程,再验证迭代,极大减少了单次写入的脉冲数量,能耗和延时分别降低了91%和25%。

5 铁电晶体管在存内计算中的应用

由于CiM在数据密集型应用中的巨大潜力,基于各类存储介质的CiM设计近年来不断涌现[50–55]。然而,基于SRAM的CiM往往需要修改单元结构以避免读写干扰,且单元面积大、成本高[56];基于DRAM的CiM则面临破坏性读取的问题[51]。相比之下,FeFET CiM不仅是非易失的,而且面积效率显著更高。与其他新型NVM和Flash构建的CiM相比,基于FeFET的CiM的能效和开关比更高,非常适合于搭建更大规模的阵列,且具有MLC存储能力和与CMOS兼容的高微缩能力。目前,FeFET CiM的主要应用有非易失计算,LiM, MVM和CAM 4类。本文中均将VDD视为状态“1”,GND视为状态“0”。

5.1 基于铁电晶体管的非易失计算

相较于其他存储介质,FeFET在结构上具有三端特性,能够同时作为非易失存储单元和控制单元,且具有容性写入负载,功耗较低。这些特性使其非常适合于实现更高密度和能效的非易失计算电路,包括替换逻辑电路中的部分MOSFET构建非易失逻辑电路[57],以及搭建非易失存储电路中的备份和恢复模块。

5.1.1 基于FeFET的非易失SRAM

非易失SRAM (Nonvolatile SRAM, nvSRAM)可以将SRAM的状态备份到内在的NVM中,并在必要时将其恢复到SRAM中。文献[58]最早提出了基于FeFET的nvSRAM设计,如图8(a)所示。备份时,Vrstr接地,Vbkp在第1个阶段设为VDD,在第2个阶段接地,向FeFET写入SRAM的状态。在恢复操作中,需要打开T0和T1,将Vbkp配置为VDD/2。当SRAM电源电压逐步增加到VDD时,由于两个FeFET的阈值电压不同,Q和QN分别浮空或接地,将放电至GND或保持VDD,实现数据恢复。与7T-1R RRAM nvSRAM相比,10T FeFET nvSRAM的备份和恢复操作不消耗静态电流,能效提升597倍。

图8 基于FeFET的nvSRAM和nvDFF[58-62]

在上述工作的基础上,文献[59]进一步改进并提出了8T FeFET nvSRAM设计,将备份/恢复的FeFET和MOSFET数量减半,如图8(b)所示。需要恢复数据时,首先将ScL, VCTRL和VBK分别设为VDD, VDD和VDD/2,再将一个反相器的电源电压升高到VDD。若M1处于LRS,则QN通过ScL被充至VDD, Q由于反相器的作用而处于GND;反之QN保持GND, Q则被抬高到VDD。当Q和QN稳定后,再将SRAM的电源电压升高到VDD即可完成数据的恢复。与7T-1R RRAM nvSRAM相比,该8T FeFET nvSRAM能效提升了363倍,而面积仅为10T FeFET nvSRAM的89%。

5.1.2 基于FeFET的非易失触发器

非易失触发器 (Nonvolatile D Flip-Flop, nvDFF)能够在系统断电时保存流水线、状态机以及寄存器堆中的关键信息。文献[60]最早提出了如图8(c)所示的基于FeFET的nvDFF。将Bkp置于高电平即可实现数据备份,其恢复操作则与10T nvSRAM类似。与此前基于其他新型NVM的nvDFF相比,该设计实现了277~1 739倍的备份/恢复能效提升。文献[61]则进一步去除了备份恢复电路中由Bkp和Bkp+Rst所控制的访问晶体管,利用器件-电路的协同设计使FeFET的极化状态能够在nvDFF正常工作时保持不变。相较于文献[60]中的设计,该nvDFF将额外晶体管数量由8个减少到4个,显著提高了nvDFF的密度。

文献[62]提出将FeFET嵌入到锁存器电路中,进而使用非易失锁存器构建nvDFF,如图8(d)所示。其中,从锁存器的状态将持续施加相应电压到FeFET栅极上,当时钟周期足够长时,nvDFF的状态变化会引起FeFET极化状态变化,从而备份数据。该设计消除了外部的控制信号,且仅需要两个额外的晶体管实现备份/恢复功能,面积效率很高,但频繁的极化翻转和较长的时钟周期带来了更高的延时和功耗。

5.2 基于铁电晶体管的存内逻辑计算

LiM是指利用存储阵列本身以及特定的外设或单元电路结构,实现二值或多值的逻辑计算。Fe-FET兼具存储与控制功能的特性,以及显著的低功耗和高开关比优势,使其非常适合LiM单元和架构的实现。2018年,Reis等人[56]首次提出了一种基于FeFET的LiM架构,其采用的存储阵列是图6(d)中的3T/C FeFET阵列。对于(N)OR的计算,可以首先对RBL预充一定电压,再同时读取参与计算的两行单元。当任一行的单元为LRS时,RBL将被逐渐放电至低电平,从而实现NOR的功能。对于(N)AND的计算,则同时读取参与计算的两行单元,并将参考电流设在IDS到2IDS之间,两个单元均为LRS时才输出“1”,如图9(a)所示。更复杂的逻辑计算如XOR等需要通过外设中额外的逻辑电路实现。相较于传统架构和基于STT-MRAM的LiM,该架构分别实现了2.5倍和1.97倍的加速,以及1.7倍和1.5倍的能耗减少。然而,其SA设计需要同时加入电压模式感测、电流模式感测和组合逻辑电路,这引入了较大的面积和功耗。

图9 LiM实现逻辑计算的原理、全动态FeFET LiM架构及其不同读取操作[63]

为避免直流电流,同时降低常见的逻辑计算后直接写回操作的延时和功耗,Tang等人[63]提出了基于FeFET的具有无需SA的直接写回策略和全动态访问特性的LiM架构,如图9(b)所示。为实现全动态访问,该感测接口采用开关电容和锁存器型电压模式的SA,同时应用电压模式的读取方法。图9(c)和(d)以2T/C FeFET为例展示了其读取操作。特别地,电压模式读取可以通过预充SL使BL充电,或将SL接地、预充BL使BL放电两种方式实现。利用这两种相反的读取策略、BL的部分放电以及BL放电策略同写入不同数据时BL电压的对应关系,相较于已有基于新型NVM的工作,该架构实现了在高级加密标准 (Advanced Encryption Standard, AES)中3.0~58倍的性能提升和3.2~78倍的能效改善。

5.3 基于铁电晶体管的存内矩阵向量乘法计算

MVM是神经网络应用中的主要操作,其基本运算为乘累加 (Multiply-Accumulate, MAC),具有数据密集但运算简单的性质,因而CiM能够提供很高的能效和加速比。如图10(a)所示,现有MVM的存内计算一般采用交错阵列 (Crossbar Array)和电流域的计算方法实现。与其他器件相比,FeFET可以通过如图10(b)所示的增量脉冲写入实现高线性度、大动态范围的权重存储,从而实现更高比特精度的MVM计算。2017年,Jerry等人[64]提出了如图10(c)所示的1T-1FeFET单元,其中晶体管具有限流功能。该工作实现了5 bit的权重存储,在MNIST数据集上1 M图像在线学习的精度高达90%,且速度相较于RRAM CiM快103~106倍。在上述结构的基础上,文献[65]优化了模数转换器 (Analog-to-Digital Converter, ADC)的电流感测阈值,文献[66]则将MOSFET替换为阻值超过1 MΩ且变化更小的TiN/SiO2隧道结电阻以降低互连线的IR压降,缓解器件偏差的可靠性问题。二者的能量效率均达到每秒每瓦特运算1.37×1016次。

图10 基于FeFET的MVM CiM架构、原理及单元[64]

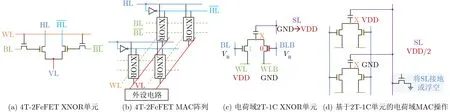

为了进一步提高神经网络应用部署的效率,一些边缘场景下可以将输入激活值和权重量化到1 bit,即二值神经网络,此时的MAC转换为XNOR逻辑。2018年,Chen等人[67]首次利用FeFET实现了二值神经网络的CiM架构,通过如图11(a)和(b)所示的XNOR单元及阵列执行计算,并进一步优化了数据的映射方式,取得相较于RRAM交错阵列395倍的写入能效提升和3.1倍的读取能效提升。然而,该电流域计算方法面临FeFET器件偏差引起的严重精度损失。为缓解这一问题,文献[68]提出了电荷域的FeFET CiM单元电路,其中两个FeFET存储互补的数据,输入值以互补的形式由WL和WLB输入,如图11(c)所示。图11(d)展示了阵列的MAC操作,当该列有N个单元,其中M个单元输出为‘1’时,电荷分配机制将使SL电压为VDD×M/N,从而实现XNOR结果的累和。由于采用电荷重分配的方案,该设计引起的充放电功耗很小,相较于基于SRAM的电荷域CiM功耗降低1.9倍,同时实现了低于0.25%的最大偏差。

图11 基于FeFET的4T-2FeFET和2T-1C XNOR单元及阵列[67,68]

在实际阵列实现上,Fraunhofer IPMS课题组[69]在2022年首次报告了具有MAC功能的28 nm Fe-FET交错阵列,阵列规模为8×8,能够实现单比特的MAC计算,且输出的线性度较好。2023年,文献[70]进一步提出并验证了28 nm MLC FeFET的2 bit MAC阵列,通过控制读取脉冲在不同阶段的幅度和宽度改变不同状态FeFET导通的时间,从而在时间域上实现高可靠性的累和。所报告的阵列规模达到32×32,在MNIST和CIFAR-10数据集上的准确率分别达到96.6%和91.5%,能效每秒每瓦特运算次数达8.854×1011次。

5.4 基于铁电晶体管的内容寻址存储器

CAM是一类特殊的存储器,能够在阵列中并行地搜索输入的数据,输出各行的匹配结果,三态内容寻址存储器 (Ternary Content Addressable Memory, TCAM)额外支持忽略向量中的特定比特(“X”)。FeFET的独特特性为高密度、高能效的CAM和TCAM设计提供了空间。2017年,Yin等人[71]首次提出了4T-2FeFET TCAM单元电路,如图12(a)所示。为写入“1”(“0”),需要向FeFET写入互补的数据,“X”的写入则需要使两个FeFET均写入HRS。在执行搜索操作时,首先将ML预充到一定电压,数据由SL和SL互补输入,若读取时发生失配,则存在下拉支路使ML电压下降,否则ML保持为高电压。

图12 基于FeFET的不同TCAM单元[71-75]

2019年,Yin等人[72]进一步提出了如图12(b)所示的2FeFET TCAM设计,极大提高了阵列密度和能效。文献[73]则利用2FeFET的多值TCAM(Multi-Level TCAM, ML-TCAM)阵列,在小样本学习等应用中取得了显著的加速效果。然而,FeFET的可靠性问题导致电流域的计算并不精确,极大限制了该设计在应用中的精度。为解决这一问题,文献[74]引入电荷域计算的思想,提出了与文献[68]类似的2FeFET-1C CAM单元和图12(c)中的2T-2Fe-FET-1C TCAM单元,以重分配后的ML电压作为该行的输出。电容的引入牺牲了一定密度,但显著提高了FeFET ML-TCAM阵列的可缩放性和在应用中的计算精度。

除此之外,George等人[75]首次从可重构性的角度展开了对FeFET TCAM的探索,提出了兼具TCAM和存储器功能的2T-2FeFET单元,如图12(d)所示。其TCAM的操作模式与此前的工作类似,存储器操作模式则需要先将M2写为低阻态,再读取M1以读出数据。该结构为存储阵列的灵活配置提供了很大的设计空间。一些后续工作探索了MLC FeFET[76]和其他结构FeFET[77]的应用,以及多比特FeFET TCAM的设计[78]。表3总结了传统SRAM TCAM和基于FeFET的TCAM的主要指标。

表3 传统SRAM TCAM和基于FeFET的TCAM主要指标对比

6 前景与挑战

作为后摩尔时代新型NVM的代表,基于Fe-FET的存储与CiM电路突破了传统CMOS存储器和冯·诺伊曼架构的瓶颈,为数据密集型应用在边缘端的存储与计算提供了高能效、高密度、高性能的解决方案。随着器件-电路-系统的跨层次协同优化的不断发展,FeFET存储器和FeFET CiM在性能、能效和密度上均不断进步,使FeFET逐渐成为低功耗、高密度的智能物联网场景中最具潜力的存储器件之一。

然而, FeFET同样引入了一些新的挑战。(1)目前FeFET的工艺成熟性不高,器件偏差很大,导致阵列可缩放性和计算精度不足。(2) FeFET的器件寿命有限,基于FeFET的电路无法频繁执行写入操作。(3) FeFET存在寄生电荷捕获效应,会导致阈值电压发生偏移和写操作后MW的严重减小。因此,FeFET在写操作后需要间隔几百毫秒才能稳定读取,这大大限制了FeFET在实际应用中的性能。(4) FeFET受读干扰的影响严重,可能会在若干次读取后丢失数据。(5) MLC FeFET在尺寸微缩时面临稳定状态数量的大幅度减少,以及状态映射的线性度下降问题。上述问题要求器件工艺的发展与器件-电路-系统跨层次协同的进一步优化,而FeFET在商业产品中的应用仍然需要学界和产业界的共同努力和持续投入。

7 结束语

数据密集型应用的兴起对存储与计算提出了更高的要求,FeFET则为解决传统CMOS存储器和存储墙的瓶颈提供了新的机遇。本文回顾了FeFET的发展历程,概述了其器件的结构、特性和基本操作,介绍了FeFET的建模以及同其他存储器的特性对比。在此基础上,本文重点讨论了FeFET存储器在电路结构和访存机制上的探索和优化,以及FeFET在非易失计算,LiM, MVM和CAM 4类CiM应用中的发展。最后,本文总结了FeFET的前景与主要挑战。结合对新型存储特性的探索以及跨层次的协同优化,基于FeFET的存储与CiM电路将在边缘端数据密集型应用的存储与计算具有广阔的前景和极高的潜力。