ARMv7架构的中断控制结构及实验设计

2022-04-06章复嘉

章复嘉, 林 菲

(杭州电子科技大学国家级计算机实验教学示范中心,杭州 310018)

0 引 言

“卡脖子”事件不仅反应出我国基础研究薄弱,特别是底层硬件知识产权的匮乏和自主研发实力的薄弱,更深层次反映出了几十年来国内高校计算机专业人才培养方向上的偏差[1-3]。

国家教指委专家在分析计算技术发展特点的基础上,介绍了系统能力培养的内涵和需求,针对我国高等教育现状和系统能力培养中存在的问题,阐述国家教指委关于系统能力培养和课程体系设置的思路[4]。

针对计算机组成原理课程的系统化教学研究中,国内双一流高校或985高校起到了领军作用。文献[5-6]中提出了面向系统能力培养的计算机专业课程体系,开发了支持MIPS32指令集的硬件计算机系统THINPAD和远程FPGA实验系统。袁春风等[7]深入研究了北美名校相关课程体系,分析计算机组成与其他课程关联关系[8]和研究生入学统考所反应出的计算机专业高等教育存在的问题[9-10],构建面向系统能力培养的计算机组成课程实验体系[11-12],从“计算机组成与设计”课程改革出发,重新梳理系统核心课程,新建计算机系统设计综合实验课程。文献[13-15]中以数字逻辑设计、计算机组成、操作系统、编译技术等课程为主线建立系统化的课程体系,使用EDA技术设计了两个级别分别包含低、中、高3个阶段的实践教学方案。文献[16-17]中对软、硬件实践类课程进行研究和整合,开发了Minisys系统并开设以大型工程项目为背景的“计算机系统综合课程设计”实践课程。

每年我国地方高校培养的本科生人数远多于双一流高校和985高校,地方高校因师资、资金、生源等原因,完全照搬上述双一流和985高校的方案来实施教学难度较大。地方高校自行开发适合于自身人才培养定位的系统能力培养方案具有重大、深远意义。

大众化教育背景下的地方院校定位是培养应用型人才,教学要求体现在:①以简单的方式讲清楚“最基本”的原理;②注重实践环节的实施,以实践教学促进理论学习。

本文提出的基于32 bit的ARMv7CPU结构的中断优先级控制实验方案,是“计算机组成原理”课程进行系统化教学改革后新开设的实验,以EDA技术结合远程FPGA实验的方式,弥补原先课程中缺少的中断内容,同时衔接了先修课“数字电路设计”、后继课“操作系统”和“嵌入式系统原理”。

1 ARMv7模型机中断优先级控制实验电路设计

预设ARMv7模型机支持1个irq中断源和1个fiq中断源。如图1所示,图中红色部分是fiq中断源和CPSR[6]控制信号;绿色部分是irq中断源和CPSR[7]控制信号;紫色部分是中断优先级判断部件,其余部分有CPU控制单元和模拟中断向量表功能的缓冲器和开关以及程序计数器PC。

图1 fiq和irq中断控制电路及地址转移电路

1.1 中断请求电路

(1)INT_fiq和INT_irq。INT_irq和INT_fiq是irq和fiq中断请求的引脚信号线,高电平有效。注意:实际上ARMCPU芯片引脚是可重定义的,而且对定义的fiq和irq引脚,都是低电平有效。实验中把INT_irq和INT_fiq引脚设计为高电平有效。

当fiq和irq中断都是开中断状态,即CPSR[7:6]=2’b00时,irq的外设中断源和fiq的外设中断源,同时申请了中断,则图1中②和④D触发器的Q端同时输出1。此时,非门输出0,导致INT_irq=0,而INT_fiq仍然是1,体现出fiq的优先级别比irq高。

(2)EX_fiq和EX_irq。fiq和irq各有对应的外部硬件设备,分别发起irq中断请求EX_irq,和fiq中断请求EX_fiq。在D触发器③输出Q=1时,当EX_irq从0变1时,D触发器④的Q端将输出1,也就是通知CPU,外设发起了一次irq中断请求。同样,在D触发器①输出Q=1时,当EX_fiq从0变1时,D触发器②的Q端将输出1,也就是通知CPU,外设发起了一次fiq中断请求。

(3)CPSR[7:6]。D触发器①在时钟端下跳沿置数,当CPSR[6]从1变0时,D端高电平传送到Q端,Q端为1。此时D触发器②的Q端是否输出1,从而传送给CPU一个irq中断请求信号,这完全取决于D触发器②的时钟端信号EX_fiq。所以,CPSR[6]从1变0就达到了fiq开中断的目的。

1.2 中断响应电路

(1)INTA_fiq和INTA_irq。INTA_irq是irq中断的响应信号,同时也是2个D触发器③④的清零信号。同样,INTA_fiq是fiq中断的响应信号,同时也是2个D触发器①②的清零信号。当CPU响应fiq中断时,CPU发出中断响应信号,即INTA_fiq=1。此时,两个D触发器①②的Q端都被清零,但是D触发器③④不清零。同时,INTA_fiq信号经过或门,打开中断向量缓冲器的三态门,使中断向量缓冲器输出中断向量开关的值。

(2)中断向量开关。中断向量开关并非ARM所有,而是为fiq和irq中断控制实验专门设计的,为实验中手动设置中断服务程序入口地址提供途径。

(3)中断向量缓冲器。中断向量开关和中断向量缓冲器的设计,代替了中断向量表的功能。本实验的2个硬件中断源对应的中断向量都由此而来。注意,在fiq抢占irq中断实验过程中,不要把fiq的中断向量和irq的中断向量设成同一地址。应分辨CPU对fiq和irq的中断响应时间,为两者分别设置不同的中断向量。

2 中断隐指令设计

当CPU响应中断时,执行ARMv7模型机的隐指令如下。

第1个clk周期。判断fiq或irq的中断引脚有否中断申请?是否开中断?即(Int_irq==1)&&(CPSR[7]==0))||((Int_fiq==1)&&(CPSR[6]==0),若表达式等于1表示应该响应该fiq/irq中断,则应保存断点PC值,因此PC→F;

第2个clk周期。应将F中的PC值保存到LR_fiq/LR_irq中,但目前CPSR中的工作模式还不是fiq/irq模式,需要通过控制信号Change_M,强制将工作模式转换成fiq/irq模式,才能完成本clk周期的操作。即,if(Int_fiq==1)&&(CPSR[6]==0)then{F→LR_fiq,CPSR→SPSR_fiq}else{F→LR_irq,CPSR→SPSR_irq}。

第3个clk周期。将保存原工作模式下的SP值到主堆栈指针MSP或进程堆栈指针PSP中,将中断服务程序入口地址置入PC,通过CPSR转换工作模式,如果响应fiq中断,那么关fiq和irq中断;如果响应irq中断,那么关irq中断。发出中断响应信号INTA_fiq/INTA_irq,打开中断缓冲器,将中断向量送往PC_s数据选择器。本clk周期的操作可描述为:

中断向量→PC,SP→MSP/PSP

第4个clk周期。执行MSP→SP_irq/SP_fiq。上一个clk周期下跳沿的时候,CPSR被写入新值,系统切换到irq/fiq工作模式,本clk周期,不需要强制模式,就可以把MSP的值写入SP_irq/SP_fiq。

在ARMv7模型机fiq和irq共存的中断系统里,中断隐指令需要4个clk周期。在每一条机器指令结束,准备转去取下一条指令之前,判断是否响应fiq/irq中断请求。只有当响应fiq/irq请求时,才执行以上的中断隐指令,否则转去取下一条指令。中断服务程序使用的也是指令系统中的指令,当中断隐指令执行完毕,取下一条指令的时候,取出来的就是中断服务程序里的第1条指令。

3 测试程序设计

基于fiq和irq中断控制系统,设计一个主程序,运行在用户模式下,设计2个中断服务程序,功能是输出循环次数。2个中断服务程序分别是fiq和irq中断服务程序,它们在内存中所处的地址段不同。中断服务程序中第1条指令的地址便是中断向量,用开关输入中断向量的时候,请注意时机。

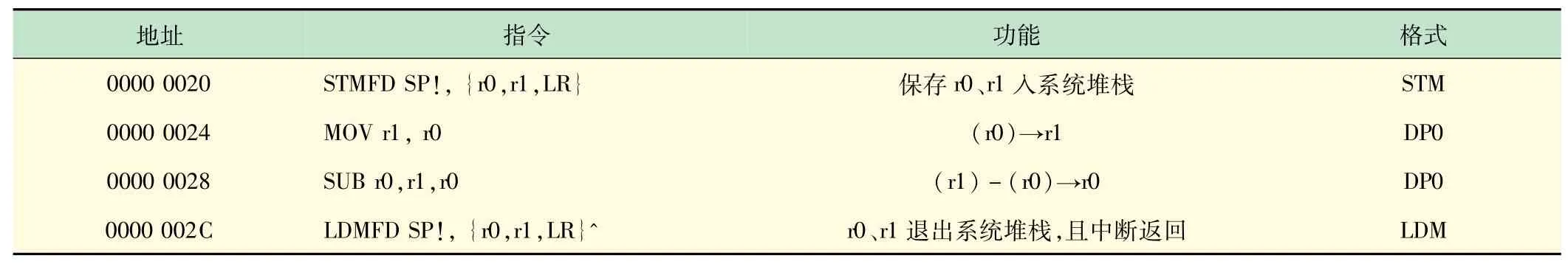

系统复位Rst以后,寄存器清零、所有分模式程序状态寄存器SPSR清零,中断请求信号INT_irq和INT_fiq清零,中断响应信号INTA_irq和INTA_fiq清零,外设中断请求信号EX_irq和EX_fiq清零,CPSR初始值为0x0000_0010,MSP初始值为0x0000_0040,PSP初始值为0,数据选择器选择信号初始值为0x0000_00C0,所有控制信号处于无效状态。系统总是从地址0开始执行。主程序和中断服务程序见表1~3。

表2 irq中断服务程序

表3 fiq中断服务程序

用ARMv7汇编器模拟器CPULator ARMv7 System Simulator对本实验测试程序进行汇编。BCC L2和BL1这两条指令的二进制码的立即数字段imm24,需要分别手动计算。其他指令采用CPULator ARMv7 System Simulator生成的二进制码。得到主程序和两个中断服务程序对应的指令机器码如下:

将以上指令码填入到和指令存储器模块ROM_B相关联的*.coe文件中,也可以调用*.coe的生成软件来完成。

在和数据存储器模块RAM_B相关联的*.coe文件中,可以不赋初值,也可以填入一些数据当作初值。本实验中,数据存储器的作用是实现堆栈。

执行指令存储器和数据存储器的Regenerate Core操作,更新指令存储器和数据存储器的初始化操作。

4 教学实施

4.1 教学方案改革

原有教学方案中,仅在理论课上安排2学时讲解中断知识点,没有配套的实验,教学效果欠佳。

教改的方案是:设计一个中断移植虚拟仿真实验项目,通过课后作业的形式,让学生在线自学、在线考试,完成中断基本知识的学习。以线上线下混合式SPOC的方式完成本文设计的中断优先级控制实验,课内实验改为3学时。

4.2 教学实施方式

近年来高校采用翻转教学法实施教学的课程越来越多,计算机硬件类实验课也在积极探索采用先进的教学方法提升教学效果。使用FPGA实验平台完成硬件实验教学成为计算机硬件课程实践教学的主流趋势。

教学实施中采用自研制的RSIE-SPOC硬件实验课翻转教学方法[18],借助自制可交互式FPGA实验板卡和7×24 h开放的远程实验云平台,实施中断实验教学。课前学生在网络教学平台上观看实验讲解短视频,按要求自行设计和编程,在远程FPGA平台上调试程序。课上老师验收实验并解答问题,课后学生修正实验方案、改进程序,撰写实验报告。

网络教学平台提供的学习资料主要有ARMv7虚拟仿真软件、Verilog HDL自动判题系统、实验表格和实验讲解短视频等。远程FPGA实验板卡布局、远程实验云平台网页和实验教学流程如图2~4所示。

图2 100片远程FPGA实验板卡布局

4.3 实施效果

自2019年上线试用以来,ARMv7中断优先级控制实验已完成2轮教学试用。学生满意度分别为82.3%和95.2%,后继操作系统课程老师评价学生对中断的掌握程度大幅度提高,课程衔接顺利。

从2021年开始,依托虚拟仿真实验项目网页,ARMv7中断优先级控制实验正式投入教学使用。

图3 远程实验云平台界面

图4 基于RSIE-SPOC方法的中断实验教学方案

5 结 语

基于ARMv7CPU结构的中断优先级控制实验设计,是地方高校探索系统化教学的一个实例。实践证明,该实验教学促进了学生对中断理论知识的理解,特别在课程衔接上获得了较好的教学效果。为更好地促进课程衔接,本文的后续工作需要设计异常处理机制和实验教学方案。