基于多FPGA的高速尺寸测量系统设计

2014-07-02潘晋孝

陈 杰,潘晋孝,刘 宾,陈 平,2

(1.中北大学电子测试技术国家重点实验室,山西太原030051; 2.中国科学院自动化研究所,北京100190)

基于多FPGA的高速尺寸测量系统设计

陈 杰1,潘晋孝1,刘 宾1,陈 平1,2

(1.中北大学电子测试技术国家重点实验室,山西太原030051; 2.中国科学院自动化研究所,北京100190)

针对传统尺寸测量系统处理速度慢、测量精度低等问题,设计了一种基于多FPGA技术和高灵敏度线阵CCD图像采集单元的高速尺寸测量系统。该系统采用延迟锁相环技术实现时钟同步,调用FPGA内部存储器IP核,并引入乒乓操作的异步FIFO设计对数据进行缓存,再由接口电路传输至上位机,实现对多参数物体测量。各子模块功能均在Xilinx FPGA的编译环境ISE中进行综合,使用MODELSIM工具进行时序仿真。实验结果表明,该系统可以满足高精度、高速实时测量的要求。

尺寸测量;多FPGA;延迟锁相环;时钟同步;线阵CCD;乒乓操作

随着自动化制造系统在各行各业的广泛应用,测量技术向着高精度化、高速度化和智能化方向发展,传统测量技术已经无法满足现代制造技术的要求[1]。目前大多数厂家进行工件测量,通常是人工测量,并手工记录数据,这样不仅误差大、效率低,而且在环境比较恶劣的情况下,例如高温铸造的工件,人工测量根本无法实现。

针对上述问题,本文提出了一种快速、准确的非接触式测量方法以适应生产检测的需求。近年来,对于多FPGA系统的硬件开发技术已经应用到很多方面,例如大数运算[2]以及航天计算处理[3],与以往的单FPGA系统相比,系统的处理速度、灵活性明显增强。而机器视觉技术由于可以实现对物体的非接触式测量,伴随数字图像技术得到快速发展[4],本文将多FPGA技术和机器视觉技术相结合,设计一种基于多FPGA的测量系统,该系统首先通过CCD采集物体尺寸信息,用多块FPGA去控制和保存图像信息,最终达到快速高精度测量。该方法简单易行,提高了测试精度和准确性,而且上位机直观显示在很大程度上方便多参数物体的数据管理。

1 系统总体设计

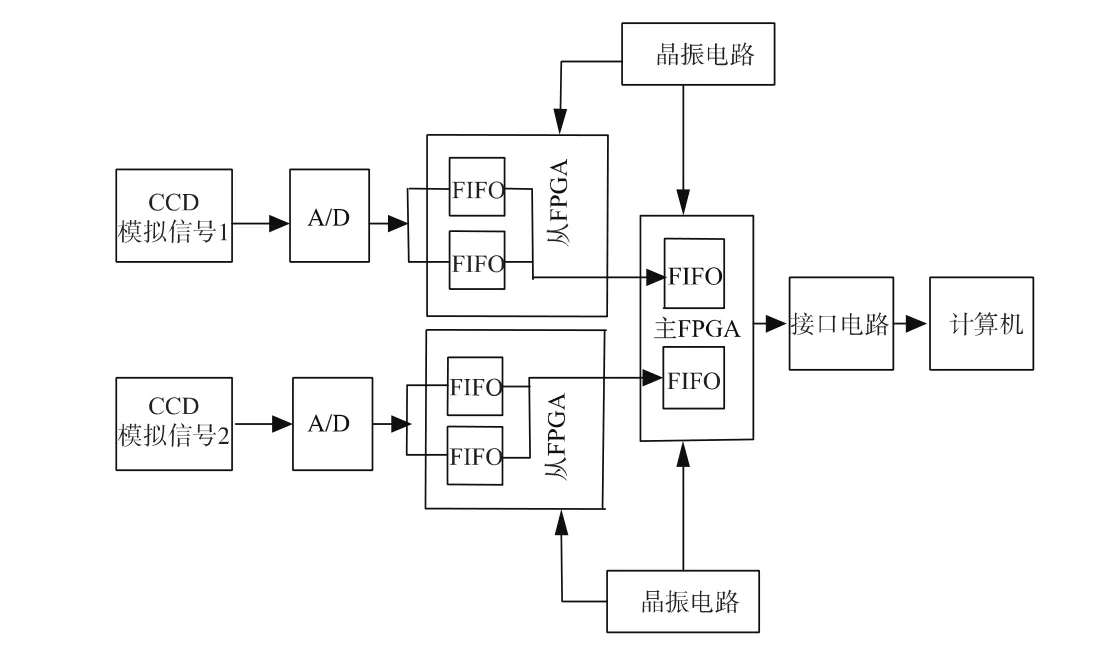

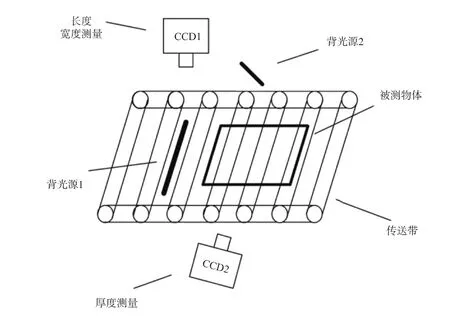

高速尺寸测量系统的软硬件电路由信号采集电路、存储电路、多块FPGA的时钟电路和上位机组成。信号采集电路主要是CCD采集图像信息输出,并经过A/D量化成数字信号;存储电路主要是调用FPGA芯片内部存储器IP核,采用乒乓操作进行数据缓存;时钟电路主要解决多块FPGA通信过程中同步问题;上位机主要是将测量结果直观显示出来。系统框图和机械结构示意图分别如图1和图2所示。

当被测物体放置在传送带上时,启动开始按钮,传送带开始以恒定速度转动,在从FPGA的时钟信号驱动下,CCD开始采集图像信息并输出模拟信号,经A/D转换成数字信号,再由从FPGA以乒乓操作的写方式将数字信号存储在两块FPGA内部的RAM中,然后再以读方式将数据写在主FPGA内部的RAM中,最终通过接口电路将图像信息传输至上位机,保存数据并实时显示测量结果。

图1 系统框图

图2 机械结构示意图

2 系统软硬件设计

2.1 图像采集单元

为了实现采集高分辨率、高速图像的要求,系统采用了东芝公司的高速CCD芯片,型号为TCD1304AP。它是一种双沟道线阵CCD,包括3 648个像敏单元,驱动时钟频率为0.8~4.0 MHz,并带有电子快门和采样保持电路。TCD1304AP比普通CCD芯片多了一个光积分控制栅,它是由驱动脉冲ICG控制,只有ICG为高电平时,积分栅才能使感光像元阵列产生的光电流在积分栅形成的存储阵列中积累,所以通过控制ICG即可控制曝光时间。

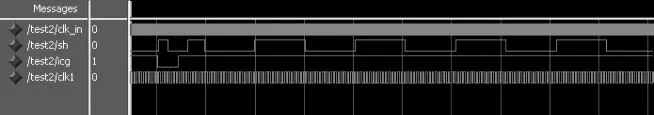

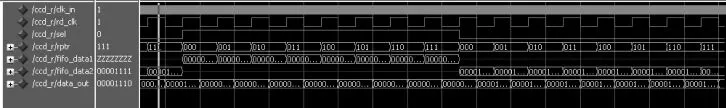

当复位脉冲信号ICG的下降沿到来时,同时帧转移信号SH产生上升沿,并持续一段时间,且ICG低电平时间要长,需保证SH信号的下降沿落在ICG的低电平上,当ICG信号的上升沿来临时,触发电极开始输出模拟信号,一次图像信息采集完成。系统设置的驱动时钟频率为2 MHz。MODELSIM时序仿真图如图3所示。

图3 CCD时序仿真图(截图)

2.2 多FPGA系统时钟同步设计

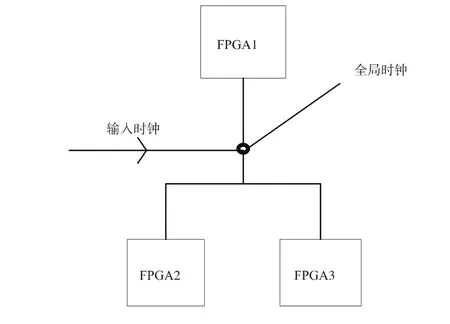

在多FPGA系统中,不同时钟域的时钟信号延迟会造成时钟偏差,进而制约着系统的整体性能。在FPGA内部,时钟偏差一般通过时钟树来解决,但一些多块FPGA系统设计的文献[5]中,也有用外部时钟树来解决时钟偏差的问题。图4所示为以3片FPGA时钟为例的同步方案,该方法选择合适的时钟原点,来减少各个FPGA的时钟偏差,这种方法虽结构简单,但在寻找时钟原点上有一定的难度,且由一个时钟源对多FPGA提供时钟时,会导致时钟质量下降。

图4 3片FPGA同步方案

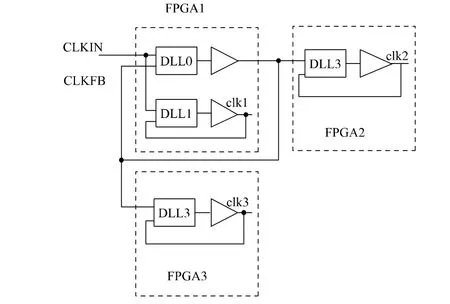

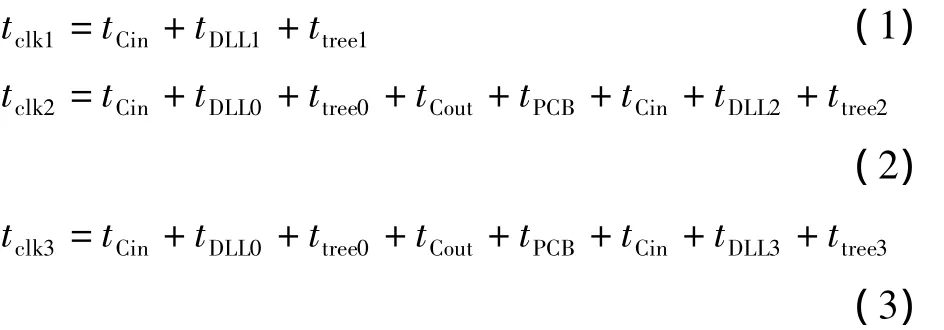

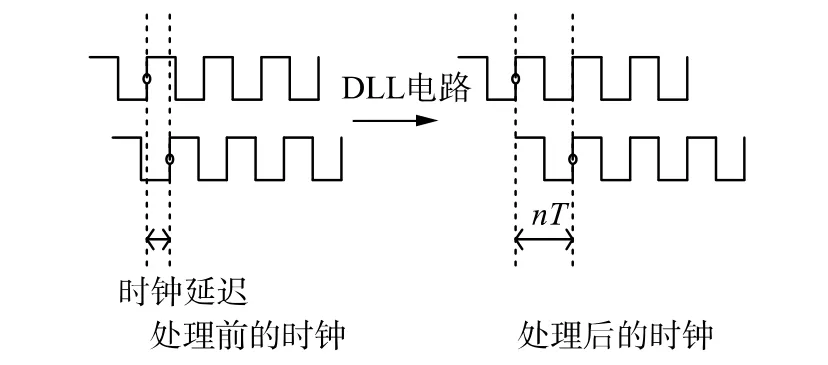

对此,利用数字延迟锁相环(DLL)的延迟锁定特性,对多FPGA系统的时钟延迟进行补偿,可以减少多FPGA之间的时钟偏差。基于DLL的多FPGA的系统同步方案如图5所示。

图5 基于DLL的时钟同步方案

该方案中晶振产生的时钟信号首先进入FPGA1的延迟锁相环DLL0,输出时钟,然后通过I/O口传给FP-GA2,FPGA3的时钟输入端和自身反馈输入端。FPGA1,FPGA2,FPGA3的全局时钟分别由clk1,clk2,clk3提供。时钟信号clk1,clk2,clk3之间的时钟延迟即为时钟偏差。分别计算clk1,clk2,clk3相对于时钟输入的偏差tclk1,tclk2和tclk3。公式为

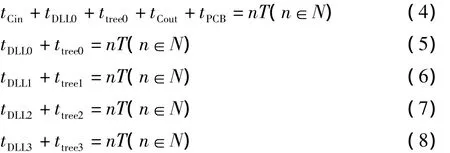

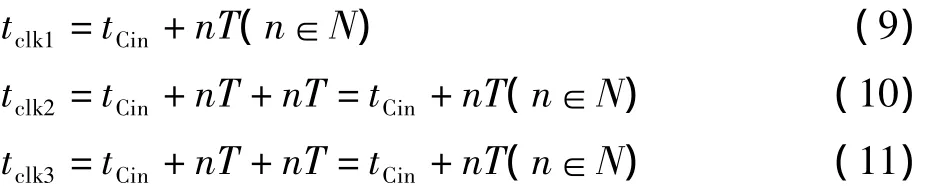

式中:tCin为输入时钟管脚到DLL的时钟延时;tCout为DLL到时钟输出管脚延时;tPCB为板级时钟布线延时;ttree时钟树上的延时。根据DLL时钟延时锁定原理[6]:由延迟模块提供所需得延迟时间,使DLL的反馈输入时钟相位与参考时钟的相位一致,实现同步。可知

化简可得

由以上可知,FPGA1,FPGA2和FPGA3的时钟相对于时钟输入来说时钟偏差是相等的,如图6所示。分析延迟锁相环结构可知,DLL1,DLL2和DLL3分别为各自FPGA的时钟补偿电路,DLL将时钟输入clk、输出时钟I/O、电路板上的时钟反馈线路放入时钟反馈回路,从而补偿由以上因素造成的时钟偏差。

图6 延迟锁相的实现

3 信号存储模块设计

为实现高速测量的目的,存储器的容量应以足够大,10 kHz采样频率,8 bit A/D量化,采集时间为2 s,加上采集单路信号和数据信号计算处理空间,所需要的存储容量至少160 kbyte以上,进行2通道数据采集至少要320 kbyte以上。传统的数据采集系统多采用Flash芯片作为存储介质[7],芯片容量少、价格高,且读写操作不能同时进行;写操作时,读操作进行等待,直到写满时才能开始读,读操作时,写操作等待,直到读空才能开始写,这些问题都会影响数据传输速度。利用乒乓操作的优势,可以实现高速存储的目的。

乒乓操作是一种处理高速数据流的技巧,巧妙地运用乒乓操作可以达到低速模块处理高速数据流的效果。不使用外部存储器,直接调用FPGA内部FIFO IP核作为存储器来完成大数据的数据流存储,这样有利于提高系统整体性能,节约系统资源。乒乓FIFO操作框图如图7所示。

图7 乒乓FIFO操作框图

多参数的数据流存储流程描述如下:CCD采集到的图像信息经A/D量化后,首先进入双路选择模块,系统通过异步比较模块判断FIFO核中的空满标志,从而控制每块FIFO的写指针和写使能;然后将数据流分配到2个数据缓存区,当FPGA识别到第1块FIFO为空时数据开始存储,为满时切换至第2块FIFO,这样依次循环进行写操作。同时当判断第1块FIFO为满时,数据开始读出,第1块FIFO为空且第2块FIFO为满时,读第2块FIFO中的数据,这样依次循环进行读操作。把2个FIFO模块当作一个整体,站在模块两端看数据,输入和输出数据流都是连续不断的,从而达到高速处理数据的目的。

根据上述思路设计深度为16 bit,宽度为8 bit的异步FIFO,用 VHDL语言对各个模块进行编写,并在MODELSIM工具进行时序仿真,其读写时序图分别如图8、图9所示。

图8 写FIFO时序仿真(截图)

图9 读FIFO时序仿真(截图)

4 系统测试结果

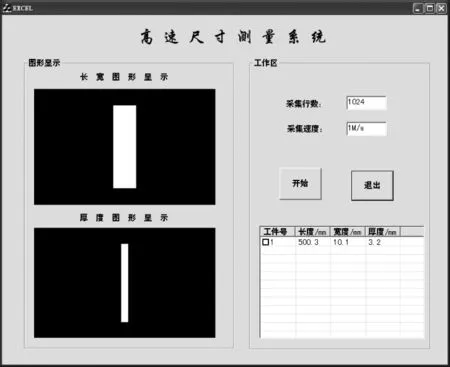

为了验证所设计的测量系统的正确性和可行性,进行了实际的采集、存储,并使用VC编写上位机界面并显示测量数据。在实验过程中,对长500mm,宽10 mm,厚度为3 mm某工件物体进行测量,测量结果如图10所示。

图10 上位机实时显示结果(截图)

通过多次实验,选取几组测量数据如表1所示,数据结果表明该系统能够快速、精确地采集物体多参数信息,并能在上位机实时显示。同时,上位机显示结果表明,与实际的参数信息相比,测量结果的误差小于0.5 mm,实现高精度低成本的目标。

表1 测量数据 mm

5 结束语

本文设计了一种基于多FPGA的高速测量系统,能够完成对传送带上目标物体的长度、宽度、厚度的高速、精确测量,测量结果误差小于0.5 mm。基于多FPGA的测量系统具有集成度高、硬件设备体积小、测量速度快等特点,可广泛应用于各种工业测量领域。

[1]单桂军,胡伟.一种基于CCD的非接触尺寸测量系统[J].电视技术,2013,37(15):41-43.

[2] ALEXAND F.A variable long-precision arithmetic unit design for reconfigurable coprocessor architectures[J].Symposium on FPGAs for Custom Computing Machines,2010(2):216-255.

[3] GRAHAM P,CAFFREY M,WIRTHLIN M,et al.Reconfigurable computing in space:from current technology to reconfigurable systemson-chip[C]//Proc.Aerospace Conference.Utah:IEEE Press,2003: 2399-2410.

[4]聂琨,萧泽新.图像处理技术在微小冲压件尺寸测量中的应用[J].电视技术,2005,29(S1):156-158.

[5]张承畅.多FPGA系统关键问题及应用技术研究[D].重庆:重庆大学,2011.

[6]黄翔.基于高性能FPGA应用的DLL研究与设计实现[D].西安:西安电子科技大学,2009.

[7]李剑,姚金杰.无线振动传感器网络节点设计[J].仪表技术与传感器,2011(10):76-77.

陈 杰(1989—),硕士研究生,主研精密测量以及信息处理;

潘晋孝(1966—),教授,博士生导师,主研信号与信息处理、图像重建;

刘 宾(1976—),讲师,主研精密测量及光电信息处理;

陈 平(1983—),副教授,主研信号与信息处理、图像重建。

Design of High-speed Size M easurement System Based on M ulti-FPGA

CHEN Jie1,PAN Jinxiao1,LIU Bin1,CHEN Ping1,2

(1.State Key Laboratory for Electronic Testing Technology,North University of China,Taiyuan 030051,China; 2.Institute of Automation,Chinese Academy of Sciences,Beijing 100190,China)

Traditional sizemeasurement system has problems of slow processing speed and low precision.To solve these problems,a high-speed sizemeasurement system based onmulti-FPGA and high sensitivity linear CCD is designed.The system uses the delay locked loop(DLL)technology to achieve clock synchronization,the internalmemory IP core of FPGA and ping-pong operation of asynchronous FIFO to storage data.At last,the data is transmitted to the host and the result is shown in the computer.Each module’s function is integrated in ISE Xilinx FPGA compiler environment.Timing is simulation with MODELSIM.Experiment results show that the system meets the requirements of real-timemeasurement ofhighspeed and high accuracy.

sizemeasurement;multi-FPGA;DLL;clock synchronization;linear CCD;ping-pong operation

TN919

A

�� 薇

2014-04-24

【本文献信息】陈杰,潘晋孝,刘宾,等.基于多FPGA的高速尺寸测量系统设计[J].电视技术,2014,38(23).

国家自然科学基金项目(61301259)