高速率低功耗FIR数字滤波器实现

2014-07-02黄朝耿

徐 红,叶 丰,黄朝耿

(1.浙江工业大学信息工程学院,浙江杭州310023;2.杭州国芯科技股份有限公司,浙江杭州310012; 3.浙江财经大学信息学院,浙江杭州310018)

高速率低功耗FIR数字滤波器实现

徐 红1,叶 丰2,黄朝耿3

(1.浙江工业大学信息工程学院,浙江杭州310023;2.杭州国芯科技股份有限公司,浙江杭州310012; 3.浙江财经大学信息学院,浙江杭州310018)

利用硬件描述语言在ASIC上对FIR数字滤波器进行了设计和综合。利用子项空间技术有效地减少了多常系数乘法中加法器的个数,并通过限制加法器深度来进一步降低高速率约束条件下的实现难度。综合结果表明,该方法可以有效降低硬件的实现面积,适用于高吞吐率低功耗的数字系统设计。

FIR数字滤波器;多常数乘法;子项空间技术;加法器深度;ASIC

当前在信息处理与通信领域,通信电子产品的低功耗设计和高吞吐率设计已成为研究热点。数字滤波器是各类电子系统中重要的组成部分,从实现的网络结构上可分为有限冲激响应(FIR)滤波器和无限冲激响应(IIR)滤波器。FIR滤波器由于其线性相位、稳定、无自激振荡且系数敏感度低等优点,在通信、图像处理、数字电视等领域都有着广泛的应用[1-2]。FIR滤波器实质上是一系列包括加法、乘法和数据传输在内的运算,最终要用物理元器件来实现。当把设计好的数字滤波器由专用集成电路(Application Specific Integrated Circuit,ASIC)实现时,会对应一定的硬件消耗,ASIC通常用某个工艺和约束速率下的实现面积来衡量。在过去几十年,人们一直研究FIR滤波器低复杂度设计方法[3-8]。子项空间技术利用滤波器系数之间的子项共享,可以有效减少滤波器实现时加法器的个数。在高速率实现的约束条件下,本设计进一步通过限制加法器深度来降低综合难度,从而实现高速率低功耗系统设计。

1 多常数乘法及子项空间技术

1.1 多常数乘法

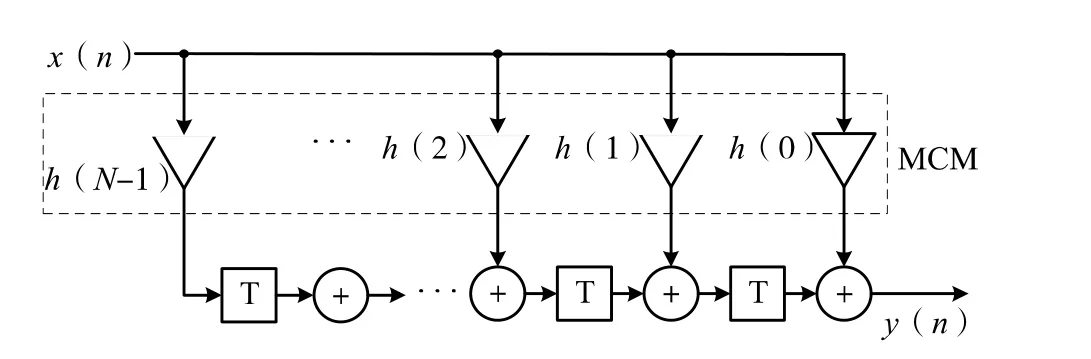

图1为FIR滤波器的直接型转置结构图。

图1 FIR滤波器的直接型转置结构

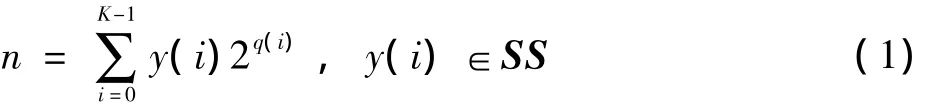

如图1所示,输入信号首先与滤波器的各个常系数相乘后被送入延时单元,这种操作通常被称为多常数乘法(Multiple Constants Multiplication,MCM)问题。常数乘法器可以通过无乘法技术来实现,即用移位寄存器和加法器代替乘法器。因此,加法器可以进一步分为常系数乘法模块加法器(Multiplier Block Adders,MBA)和延迟单元的结构加法器(Structural Adders,SA),见图2。需要指出的是,一旦给定滤波器阶数,延时单元和SA的数量相对固定(除非有些系数为0,SA会有所减少),因此,FIR滤波器实现复杂度主要决定于MBA的个数[3]。

1.2 子项空间及子项共享

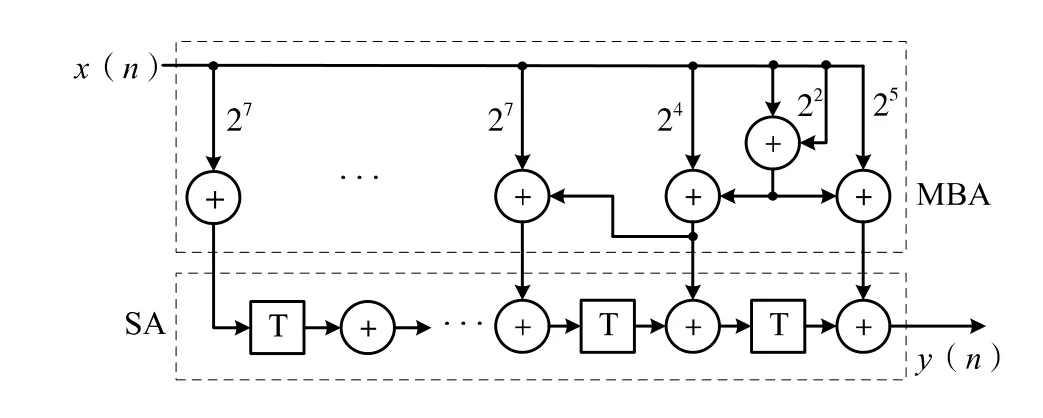

一个离散子项空间中的元素可以通过下式构建[3]

图2 常系数乘法模块加法器和结构加法器

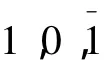

图3 单个系数乘法的实现

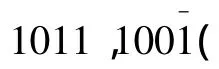

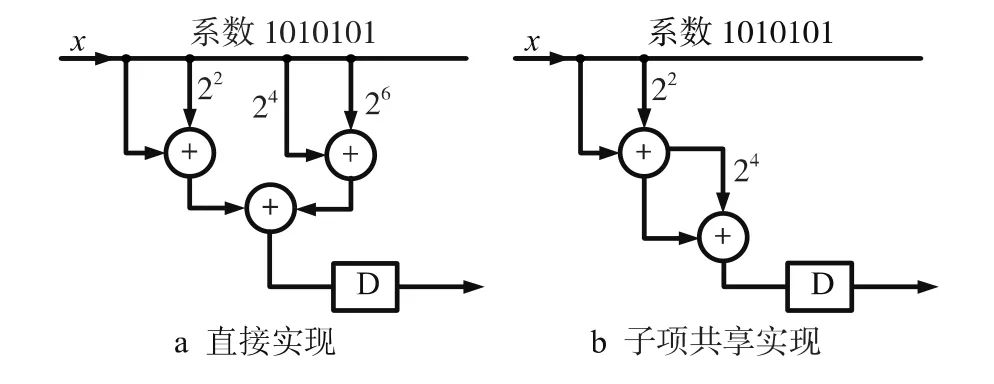

需要指出的是,单个系数内部或多个系数之间,若存在公共子项的加法器,均可实现共享,从而达到减少加法器个数的目的,下面举例说明:1)假设某一系数用二进制序列表示为1010101,当采用直接实现时,需要3个加法器,如图3a所示,若将公共子项101提取出来先实现,则最终仅需2个加法器,如图3b所示。2)假设两个系数用二进制序列表示分别为100101和10101,当两个系数独立实现时,每个系数都需要两个加法器,则总共需要4个加法器,如图4a所示,若将公共子项101提取出来先实现,每个系数只需要增加一个额外的加法器,则总共需要3个加法器,如图4b所示。因此,合理利用子项共享技术,将有效降低数字滤波器的硬件消耗[3]。

图4 两个系数乘法的实现

1.3 常系数乘法的加法器深度

一个系数的加法器深度是指实现该系数乘法最差路径(Critical Path)的加法器个数[9]。由图3和图4易知,其加法器深度都是2。由文献[9]可知,所有系数加法器深度的最大值(简称最大加法器深度)对整个设计的吞吐率和功耗都有很大影响,尤其在高速实现时这种影响尤为重要,因此在高速率低功耗系统设计时,不仅要求加法器个数少,而且要使最大加法器深度尽量小。

2 ASIC综合

综合是把设计转化为可制造器件的转移过程,该器件能执行预期的功能,ASIC是当前最常用的器件之一。半导体加工工艺地不断提高使得半导体芯片集成化程度越来越高,系统越来越复杂,因此,集成电路的设计方法也随之改变。由最初的手工设计阶段、计算机辅助设计阶段(Computer Aided Design)、计算机辅助工程阶段(Computer Aided Engineering),已经发展到目前的电子自动化设计阶段,即用硬件描述语言(Hardware Description Language)来进行设计。

硬件描述语言支持行为级(Behavioral Level)、寄存器传输级(Register Transfer Level,RTL)和门级(Gate Level)三个不同级别的设计,目前人们普遍使用寄存器传输级源代码(RTL Source Code)进行设计。设计师用RTL源代码描述了设计的时序电路和组合电路的功能,包括电路的寄存器结构和寄存器数目,电路的拓扑结构以及输入/输出接口和寄存器之间组合电路的逻辑功能和寄存器与寄存器之间组合电路的逻辑功能[10]。电路的逻辑功能如何由具体的电路来实现,则需要根据IC设计师对电路所加的约束,由综合工具产生,如Synopsys公司的Design Compiler(简称DC)。RTL源代码的功能验证完成后,用DC综合出门级电路。DC自20世纪80年代末问世以来,在EDA市场的综合领域,一直处于领导地位,几乎所有大的半导体厂商和集成电路设计公司都使用它设计ASIC,本文也在此平台下分析FIR滤波器实现时的面积消耗。

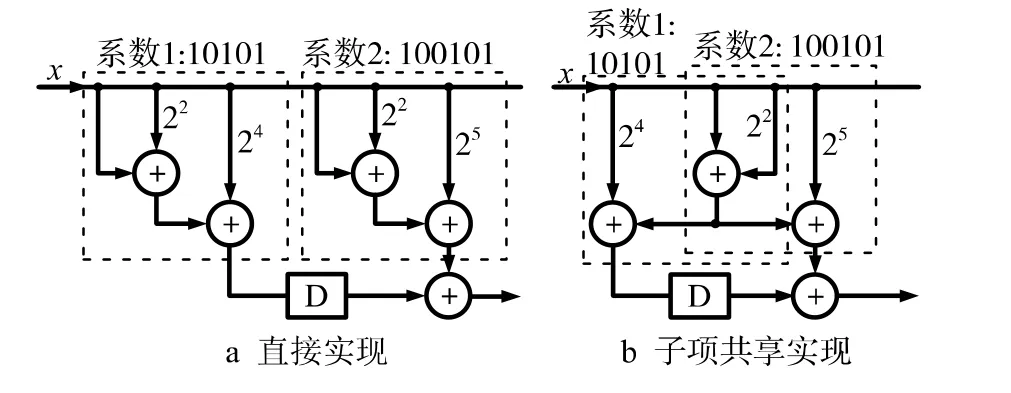

ASIC综合结果和设计约束(Design Constraint)有很大的关系,设计时提供约束(即时序等信息)指导综合工具,综合工具使用这些信息尝试产生满足时序要求的最小面积设计。DC软件在综合时使用内建的静态时序分析器把设计分解成多条时间路径,然后根据设计约束对这些路径进行优化。如果某条路径的时间延迟大于约束值,则该路径时间违规(Timing Violation),电路不能正常工作,无法达到设计目标。图5是综合结果的时序和面积折衷曲线[10]。由图5可见,设计结果或是面积大、延时短,或是面积小、延时长,或是面积和延时均适中。

图5 ASIC综合结果的时序和面积折衷曲线

3 基于子项共享的FIR滤波器实现

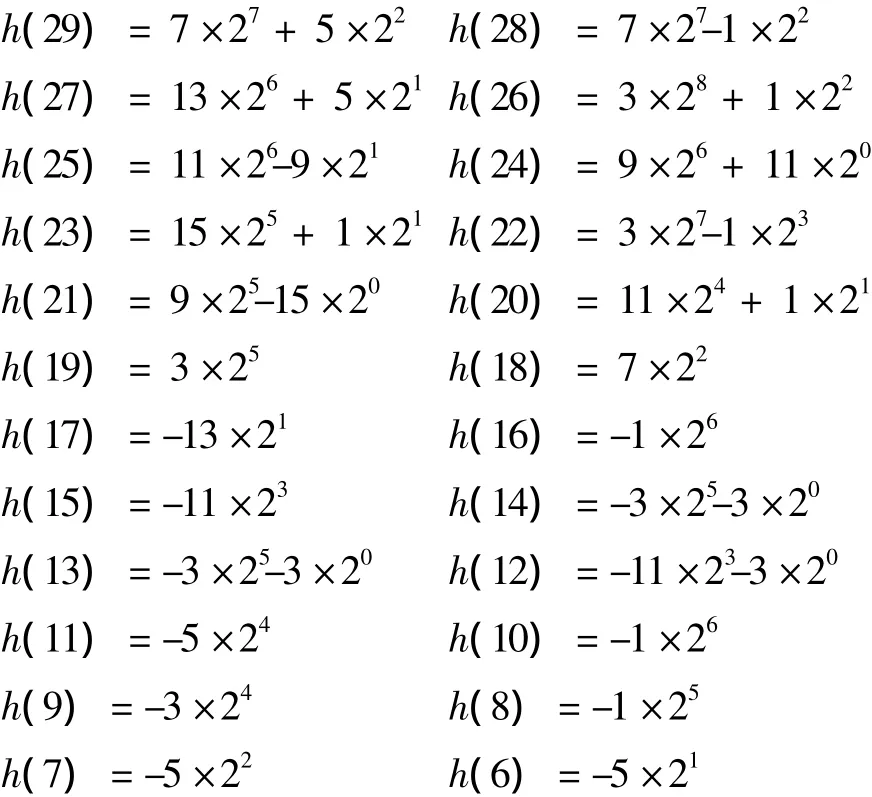

以文献[3]中的滤波器S2为例,说明基于子项共享的FIR滤波器实现方法。S2的阶数为60,基组为:{3,5,7,9,11,13,15},其阶数等于7(3=2+1;5=4+1;7= 8-1;9=8+1;11=8+3;13=4+9;15=16-1),基于子项基组优化得到的滤波器系数如下[3]:

上述系数中,h(n)=h(59-n),30≤n≤59,通带增益10 945.336 1,脉冲响应×8 192。

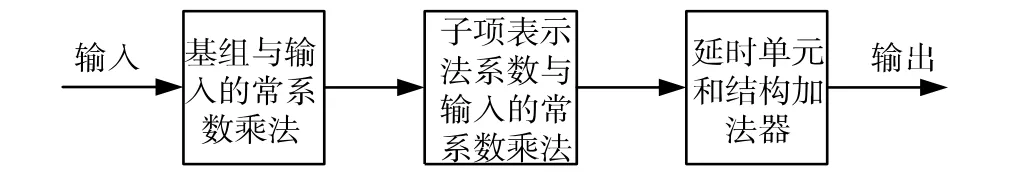

基于子项共享的程序结构框图如图6所示。

图6 程序结构框图

各模块需要的加法器个数如下:

1)“基组与输入的常系数乘法”模块需要7个加法器;

2)“子项表示法系数与输入的常系数乘法”模块参照表1需要13个加法器,但由于系数h(13)和h(14)相同,因此实际只需要12个加法器;

3)S2的阶数为60,且系数都不为0,因此需要59个结构加法器。

综上,MBA的数目为19,SA的数目为59,共需要78个加法器。本例最大加法器深度等于3,出现在用到基组“11”和“13”进行加法运算的子项系数上,例如产生h(20):1+2→3+8→11×24+1×21。子项共享实现可以有效减少加法器个数,但不能保证降低加法器深度,较大的加法器深度不利于系统的高速实现。

4 综合结果举例

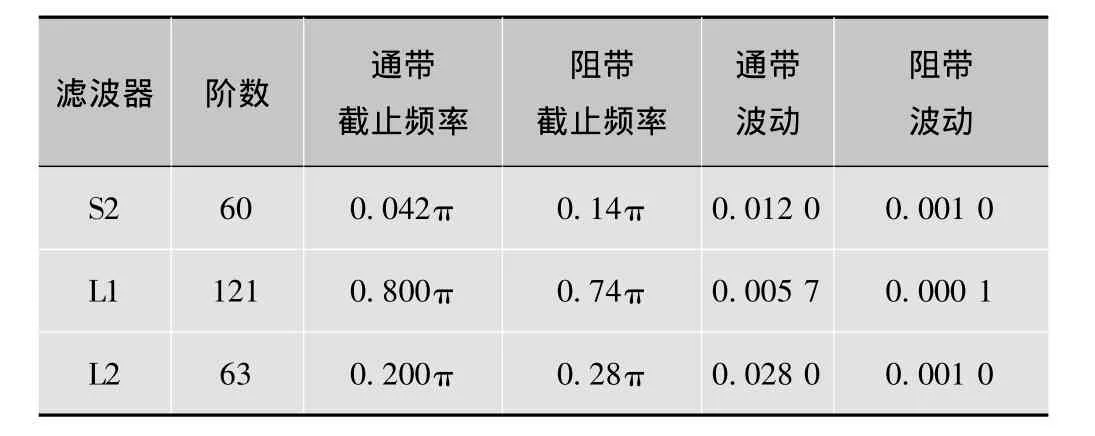

Verilog HDL是目前广泛使用的硬件描述语言,为IEEE标准,可以用不同的工具进行综合和验证,应用广泛。这里采用Verilog HDL进行FIR数字滤波器的RTL级描述,分别在不同的约束条件下用ASIC的综合工具DC来进行逻辑综合,从而得到对应的硬件资源消耗指标。本节将选取文献[3]中的3个例子分别在ASIC上进行综合比较。3个例子的性能指标如表1所示。

表1 滤波器性能参数

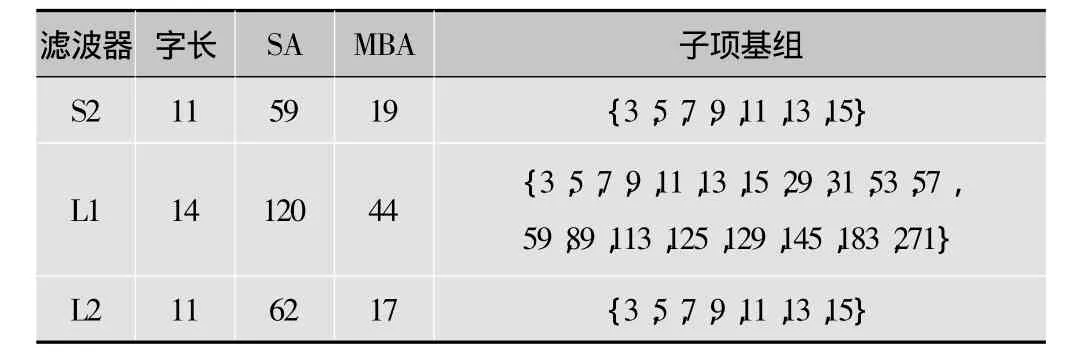

文献[3]中基于子项共享进行系数离散化得到的实现结果如表2所示。

表2 滤波器加法器个数及基组

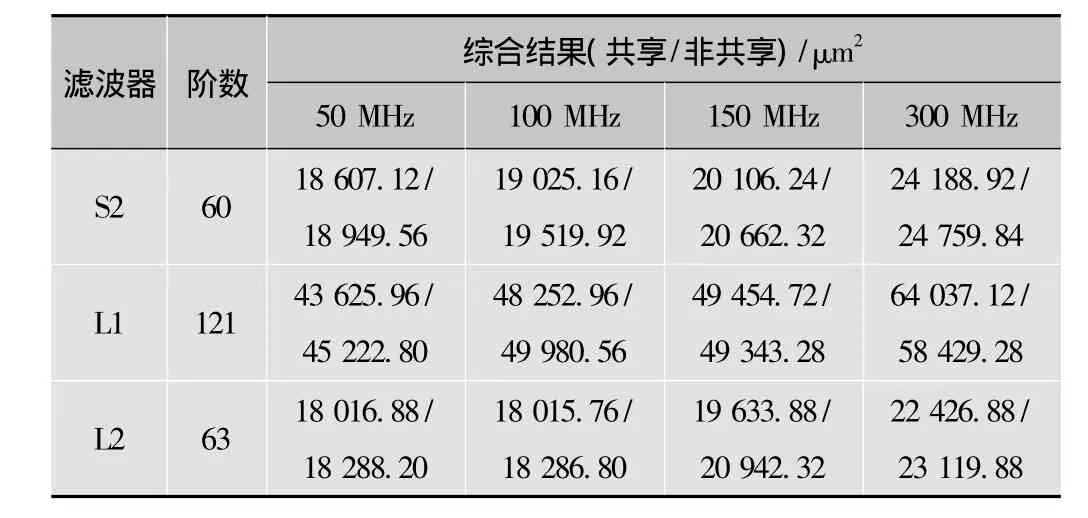

如前所述,ASIC硬件资源的消耗可以通过设置某个约束条件后综合的面积来衡量。本文选择55 nm的CMOS工艺进行综合,时序约束条件分别设置为50 MHz,100 MHz,150 MHz,300MHz。综合结果见表3。

表3 ASIC综合性能比较

从表3可以看出,基于子项共享的实现总体可以有效减少ASIC的面积消耗,节省成本和功耗。约束频率相对低时,优势明显。当约束条件分别为150MHz和300 MHz时,L1滤波器子项共享的结果大于非共享的情况,且当频率为300MHz时,共享实现的Timing Violation为-0.32 ns,即并没有达到设计要求。

5 高速率约束条件下的进一步优化

由图5可以看出,滤波器的面积和时延是矛盾的,即高速率是以牺牲功耗和面积为代价的。子项空间共享的方法能够降低加法器个数,但加法器深度不一定会降低,较高的加法器深度不但会增加功耗,而且使得高速率实现也变得困难。当约束速率较高时,实现难度比直接实现可能更高,从而使综合面积没有明显优势。因此,为了改善高速率约束条件下的综合结果,需要进一步降低加法器深度。

5.1 方法一:优化系数的产生方法

主要考虑两个方面:

1)产生基组,例如基组13=9+4=11+2,显然用“9+ 4”更好,对应的加法器深度小。

2)产生子项系数,例如前文中h(22)=376=3×27-1 ×23=11×25+3×23,显然用“3×27-1×23”更好,对应的加法器深度小。

由于系数已经确定,可被优化的个数有限,因此这种方法的效果不明显。若在系数设计阶段就考虑这一点,在优化加法器个数的同时优化加法器深度,综合效果会进一步提升,详见文献[9]。

另一实用且有效的方法是在组合逻辑中直接插入寄存器,从而在硬件上直接拆分组合逻辑,降低最大加法器深度,达到提高速率的目的。

5.2 方法二:拆分组合逻辑

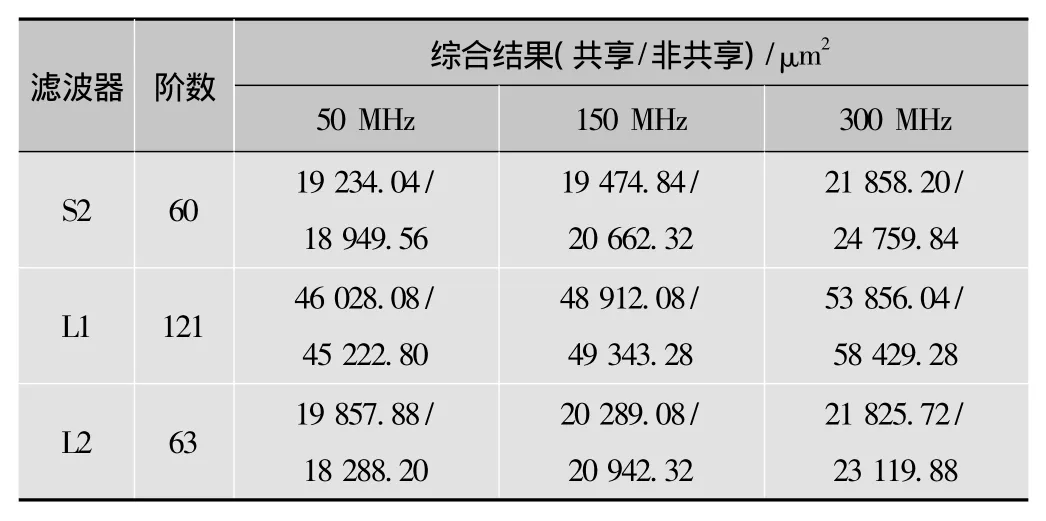

两个位置可以插入寄存器:1)“基组与输入的常系数乘法”模块后;2)“子项表示法系数与输入的常系数乘法”模块后。根据实际经验,若子项基较小,“子项表示法系数与输入的常系数乘法”模块后寄存就可以了,如果子项基较多且值较大,可以考虑在两个位置都寄存。加入寄存器虽然增加了一些硬件消耗,在低频时没有优势,但在高频时,却可以使ASIC综合时更容易达到要求,从而使整体面积有效减小,综合结果如表4所示。

表4 降低加法器深度后ASIC综合性能比较

6 总结

基于子项空间共享技术实现FIR数字滤波器可以有效减少加法器个数,利用ASIC进行硬件实现时有效地降低了实现面积和功耗。在高约束速率时可以进一步通过拆分组合逻辑来降低加法器深度,适用于高速率低功耗系统设计。

[1]张婧霞,沈三民,翟成瑞.基于FPGA乘法器的FIR滤波器系统设计[J].电视技术,2012,36(3):40-42.

[2]黄凤英,王俊,钱慧.基于模块局部可重构FIR滤波器设计[J].电视技术,2013,37(9):83-86.

[3]YU Y J,LIM Y C.Design of linear phase FIR filters in subexpression space usingmixed integer linear programming[J].IEEE Trans.Circuits Syst.I,2007,54(10):2330-2338.

[4]YU Y J,LIM Y C.Optimization of linear phase FIR filters in dynamically expanding subexpression space[J].Circuit Syst.Signal Process,2010(29):65-80.

[5]SHID,YU Y J.Design of linear phase FIR filterswith high probability of achieving minimum number of adders[J].IEEE Trans.Circuits Syst.I,2011,58(1):126-136.

[6]POTKONJAK M,SHRIVASTAM B,CHANDRAKASAN A P.Multiple constantmultiplication:Efficientand versatile framework and algorithms for exploring common subexpression elimination[J] .IEEE Trans.Comput.Aided Des,1996(15):151-161.

[7]XU F,CHANG C H,JONG C C.Design of low-complexity FIR filters based on signed-powers-of-two coefficientswith reusable common subexpressions[J].IEEE Trans.Comput.Aided Des,2007(26):1898-1907.

[8]WANG Y,ROY K.CSDC:A new complexity reduction technique for multiplierless implementation of FIR filters[J].IEEE Trans.Circuits Sysm.I,2005,52(9):1845-1853.

[9]YU Y J,LIM Y C.Optimization of FIR filters in subexpression space with constrained adder depth[C]//Proc.6th International Symposium on Image and Signal Processing and Analysis(ISPA).Salzburg:IEEE Press,2009:766-769.

[10]虞希清.专用集成电路设计实用教程[M].2版.杭州:浙江大学出版社,2013.

Im plementation of High-speed and Low-power Consum ption FIR Digital Filters

XU Hong1,YE Feng2,HUANG Chaogeng3

(1.College of Information Engineering,Zhejiang University of Technology,Hangzhou 310023,China;2.Hangzhou Nationalchip Science&Technology Co.,Ltd.,Hangzhou 310012,China;3.School of Information,Zhejiang University of Finance&Economics,Hangzhou 310018,China)

In this paper,a hardware technique for implementing FIR filters on ASIC is proposed.The coefficientmultipliers are realized with shifters and adders.The subexpression space technology is adopted,which can effectively reduce the number of adders in the filter.In order to reduce the complexity of implementation,the adder depth is limited under the high rate constraints.The results of hardware synthesis show that the proposedmethod can efficiently save area consumption,which can be used to design the high throughput digital systems.

FIR digital filter design;multiple constantsmultiplication;subexpression space technology;adder depth;ASIC

TN713

A

�� 薇

2014-05-12

【本文献信息】徐红,叶丰,黄朝耿.高速率低功耗FIR数字滤波器实现[J].电视技术,2014,38(23).

浙江省自然科学基金项目(LQ14F030008)

徐 红,(1978—),女,博士研究生,讲师,主研数字滤波器设计、FPGA及ASIC开发技术;

叶 丰,(1975—),杭州国芯科技股份有限公司技术总监,主要从事数字电视技术、集成电路设计。