LVDS(低压差分信号)测试技术研究

2011-07-02柴海峰朱卫良章慧彬武乾文

柴海峰,朱卫良,章慧彬,武乾文

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

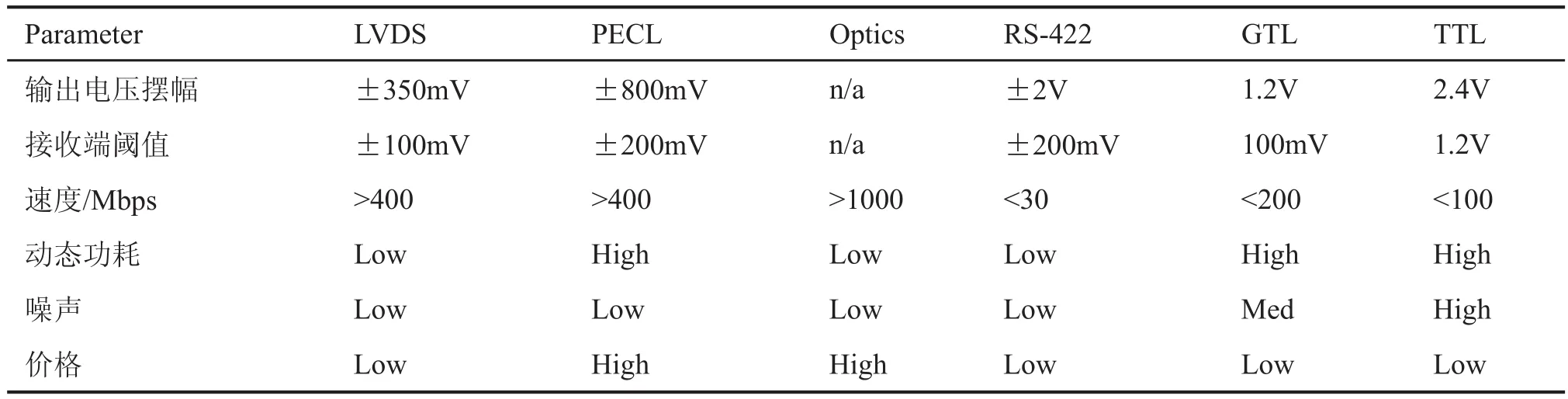

高速数据总线常用的器件有ECL、BTL、GTL等,但这些电路共同的弱点就是功耗大,而且电磁辐射也较强。National Semiconductor公司推出了CMOS工艺的低电压差分信号器件(Low Voltage Differencial Signal, LVDS),LVDS 与其他常见信号参数对照表见表1。LVDS(Low Voltage Differential Signaling)即低压差分信号传输,是一种满足当今高性能数据传输应用的新型技术。LVDS 技术拥有330mV 的低压差分信号 (250mV min and 450mV max)和快速过渡时间,它允许单个信道传输速率达到每秒数百兆比特。

图1 LVDS器件的工作原理图

LVDS简化的收发模型包括驱动器、接收器和连接器,见图1。LVDS接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过了100Ω的匹配电阻,并在接收端产生大约350mV的电压。当驱动器翻转时,流经电阻的电流方向改变,产生有效的逻辑“1”和“0”状态。

LVDS具有输出电压摆幅低、传输速率高的特点。LVDS技术已经在通信网络中得到普及,广泛用于笔记本电脑、办公室成像、工业视觉、测试与测量、医疗和汽车等领域。其测试技术涉及测试PCB设计、抖动信号及分析、误码率、眼图测试等。

表1 常见信号参数对照表

2 信号完整性设计

为了真实测量LVDS信号的指标,在测试板设计中应从高速单板设计和差分信号理论考虑,保证信号的完整性。

在较低数据速率时,驱动器和接收机一般是导致信号完整性问题的主要因素。以往人们通常把印刷电路板、连接器、电缆和过孔当成是简单的部件,稍加考虑或者无需考虑其他因素就可以很容易地把它们组成一个系统。现在,从逻辑电平0到逻辑电平1的数据上升时间已不到100ps,当这么高速的信号在传输线路上传输时会形成微波传输线效应,这些传输线效应对于信号的影响会更加复杂。

2.1 测试PCB设计

(1)至少使用4层PCB:LVDS信号层、地层、电源层、TTL信号层。

(2)使TTL信号和LVDS信号相互隔离,否则TTL可能会耦合到LVDS线上,最好将TTL和LVDS信号放在由电源/地层隔离的不同层上。

(3)使LVDS驱动器和接收器尽可能地靠近连接器的LVDS端。

(4)使用分布式的多个电容来旁路LVDS设备,表面贴电容靠近电源/地层引脚放置。

(5)电源层和地层应使用粗线,不要使用50Ω布线规则。

(6)保持PCB地线层返回路径宽而短。

2.2 差分线

(1)使用与传输媒质的差分阻抗和终端电阻相匹配的受控阻抗线,并且使差分线对离开芯片后立刻尽可能地相互靠近,这样能够减少反射并能确保耦合到的噪声为共模噪声。

(2)使差分线对的长度相互匹配以减少信号扭曲,防止因其信号的相位差而导致电磁辐射。

(3)尽量减少过孔和其他会因其线路不连续性的因素。

(4)在差分线对内,两条线之间的距离应尽可能短,以保持接收器的共模抑制能力。

2.3 终端

(1)使用终端电阻实现差分传输线的最大匹配,阻值一般在90Ω~130Ω之间,系统也需要此终端电阻来产生正常的差分电压。

(1)使用精度为1%~2%的表面贴电阻跨接在差分线上,必要时使用两个阻值各为50Ω的电阻,并在中间通过一个电容接地,以滤去共模噪声[1]。

3 抖动

抖动可以定义为数字信号在重要时间点上偏离理想时间位置的短期变化。高速信号产生问题的原因很多时候都是由于抖动造成的,LVDS信号出问题很多都是由于时钟的抖动。高速时钟信号中抖动的成因是很复杂的,总的抖动成分TJ中包含了确定性抖动DJ和随机抖动RJ,而DJ和RJ又分别是由很多因素构成。因此LVDS的测试中应包含各抖动分量的测量项目。

确定性抖动DJ来源于系统,例如串扰、码间干扰和电源的馈通,它是有界的,因此可以用峰峰值来描述。随机抖动RJ来源于各种物理干扰源,如热噪声、散粒噪声和光介质中的散射,描述随机抖动的经典方法是其概率密度函数,其一般具有高斯分布特性。高斯函数的上下边界在无限远处,因此总的抖动的随机分量是无界的。LVDS要准确测量DJ和RJ,需要借助于相应的抖动分析软件。

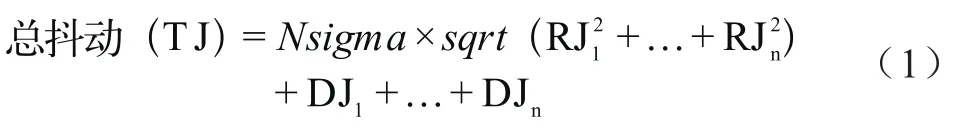

如果存在多个抖动,所有RJ源必须以rms形式相加,而DJ源必须以线性方式相加,所以总抖动计算如式(1):

由于LVDS的信号速率比较高,因此要对LVDS信号进行可靠的探测,对于示波器和探头的要求也非常高,通常测量要求使用2.5G~4G带宽的示波器,结合抖动分析软件。LVDS器件往往需要测试抗干扰能力,需要在输入信号上人为注入抖动,我们使用AWG结合SerialXpress软件产生抖动信号,该软件可以产生确定性抖动、随机抖动、噪声等信号的加载,并可以设定信号上升时间,非常适合用于LVDS等高速信号的测试。

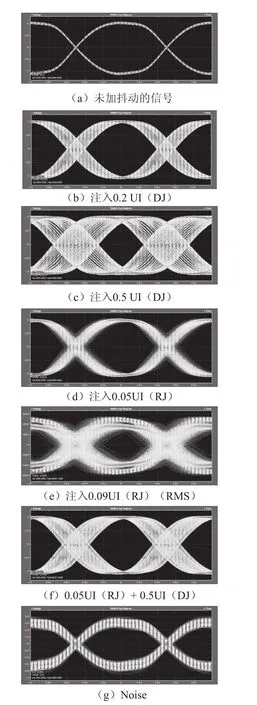

4 眼图

眼图是一种直观的评价系统信号质量的方法,眼图张开部分的宽度(眼宽)就是接收波形可以不受串扰影响而进行抽样的时间。眼睛在特定时刻的张开高度(眼高)决定了系统的噪声容限。图2为我们使用泰克公司AWG7082C作为信号源、MSO70404示波器进行眼图分析的结果。其中 ,图2(a)是未注入抖动的原始信号,图2(b)是注入0.2IUI确定性抖动的信号眼图,图2(c)是注入0.5UI确定性抖动的信号眼图,图2(d)是注入0.05UI随机抖动的信号眼图,图2(e)是注入0.09UI随机抖动的信号眼图,图2(f)是同时注入0.05UI随机抖动和0.5UI确定性抖动的信号眼图,图2(g)是信号注入噪声后的信号眼图。

5 误码率

图2 信号眼图

对于通信等应用,常常必须满足非常严格的误码率(BER)要求,例如10-12~10-15位中的错误要低于1位。总的抖动将决定错误的大小,因为总的抖动包括了随机抖动,目前能充分保障这样水平的误码率的成熟方法是发送大量的伪随机数据,而且以一种被称为误码率测试(BERT)的技术来验证每一位数据是否得到正确的传输。对于高的误码率情形进行BERT测试,将耗费大量的时间,因此对于日常应用来说不具有实用性。相反,工程师采用眼图、眼图掩模和浴缸曲线来对型号完整性是否恰当进行验证,从而推测出误码率。图3为一个利用浴缸曲线推测误码率的例子。其中总抖动Total Jitter和眼图张开度满足下面的关系:

图3 浴缸曲线

6 系统集成

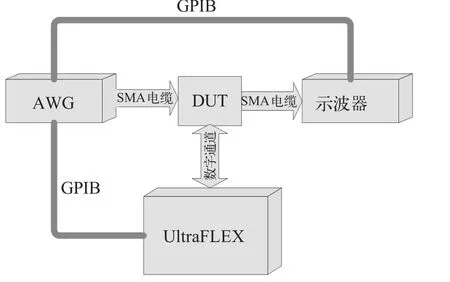

LVDS器件测试包含大量直流参数和时间参数测试,这部分参数一般使用大型测试系统测试,对于抖动、眼图等测试需要借助示波器、AWG等设备进行测试。我们使用UltraFlex大型测试系统和传统仪器结合的方案对LVDS器件能够进行全面的测试,系统组成如图4。AWG和示波器通过GPIB电缆与UltraFlex连接,通过UltraFLEX主控电脑编程控制测试过程。外部仪器可以当作系统内部资源直接使用,大大简化了测试时间和复杂度。

测试程序的编写是在UltraFLEX开发环境下编写的,使用VB语言,程序编写前需先安装VISA32的函数库。 VISA(Virtual Instrumentation Software Architecture)即虚拟仪器软件体系结构,虚拟仪器软件结构中的标准I/O接口软件称为VISA库,它驻留于计算机系统中执行仪器总线的主要功能,为计算机与仪器之间的软件层连接,实现对仪器的各种操作,用户可以在调用VISA函数库的基础上开发测量控制程序[2]。

图4 UltraFLEX与传统仪器结合的LVDS测试方案

7 小结

本文对LVDS测试中可能遇到的问题进行了深入分析,实际被测参数远不止文中介绍的这几种,但在上述信号完整性和信号处理的方法下,使用适当的资源,其他参数也都有方法可以进行测试。

[1] 陈伟.高速电路信号完整性[M].北京:电子工业出版社,2009.

[2] 顾大权.基于VISA和SCPI的多点数据测量系统[J].仪表技术,2011,(1):1-2, 6.