基于TMS570的SIL4级列控系统安全平台设计

2023-09-27裴志斌吕媛媛

裴志斌,吕媛媛

(北京全路通信信号研究设计院集团有限公司,北京 100070)

1 概述

轨道交通领域的列控系统是对列车运行状态进行控制的系统,其中的安全平台应该具备高安全性、高可靠性的特点,满足安全完整性等级SIL4 级功能要求。TMS570 是TI 公司Hercules 系列的安全微处理器,是TI 针对航空航天、轨道交通领域推出的新型安全微处理器。一般的微处理器不具备安全功能,需要用户通过软件实现,而TMS570 微处理器在硬件内部已做好安全防护,从而使CPU 部分的架构简洁化、性能最佳化,从而减少用户软件开销。本文基于TMS570 设计一个列控系统SIL4级安全平台。

2 TMS570 CPU安全自检设计

在EN 50129:2018 标准里,针对SIL4 级系统提出要求,对数字集成电路的单点故障防护应对CPU 进行初始化时的自检和运行中的周期自检。系统对安全CPU 的自检内容应包括:指令集(加减乘除、移位、等值、与或非等)、内部RAM、栈空间防护、内部ROM、寄存器(通用寄存器、专用寄存器含Flag Register、核外可检测寄存器)、Cache(尽量关掉,因缺少自检方法)和时钟偏移。

TMS570 CPU 可提供双核锁步CPU 架构、CPU 和存储器内置硬件自检BIST、内存保护单元(MPU)、Flash 和RAM 接口上的ECC 和片上时钟及电压监控等一些关键功能的安全特性,单CPU 芯片达到了IEC61508 标准中SIL3 级的相关要求。CPU 硬件内置的自检功能,使用户无需设计复杂的安全软件和花费安全代码费用,即可检测到潜在缺陷。

2.1 TMS570芯片架构

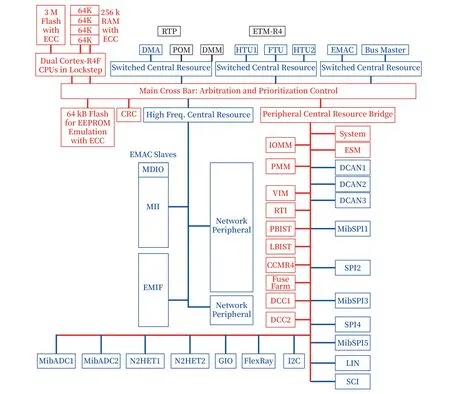

以TMS570 系列里的TMS570LS3137 为例,CPU 架构如图1 所示,从安全功能角度将CPU 分为3 部分。

图1 TMS570LS3137芯片结构Fig.1 TMS570LS3137 chip architecture

红色部分为安全岛层(Safe Island Layer):包含芯片内安全运行相关功能,如双CPU 锁步周期故障检测机制、RAM 的ECC 等,这些功能始终运行,用户无法关闭,拥有最高的硬件自检诊断覆盖率。

蓝色部分为混合层(Blended Layer):包含执行外部安全相关功能的外设。这部分功能仅在部分关键部位具备有限的硬件自检措施,如外围存储器上的奇偶校验、模拟和数字I/O 环回测试、AD 自检和校正等,自检主要通过用户软件实现。

黑色部分为离线层(Offline Layer):包含调试和测试相关功能。这部分功能不包含在硬件自检范围内。

2.2 异常处理

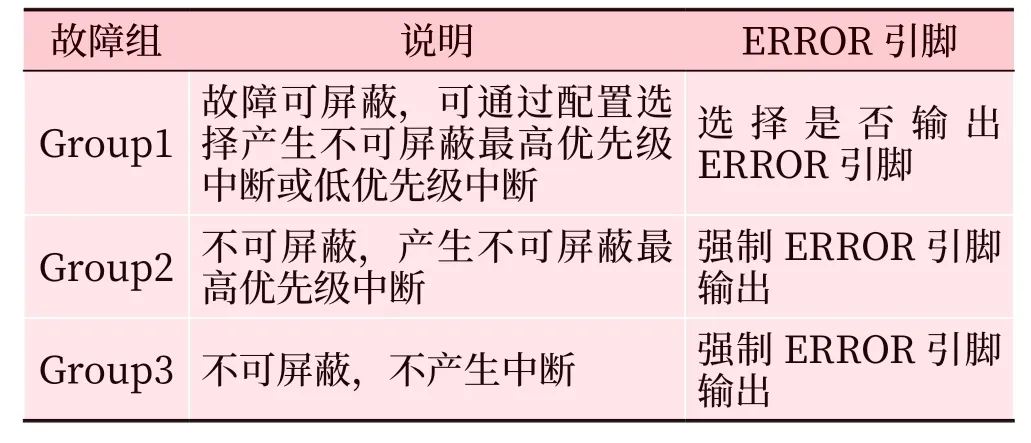

TMS570 架构中设计了一个错误信号模块(ESM-Error Signaling Module),来提供内部安全措施的故障指示集合。CPU 检测到故障后会通过ESM 模块触发中断处理,并通过MCU 的ERROR引脚向外输出信号。故障依据固定的严重等级分类,根据故障的分类产生相应的反应,ESM 对故障等级的管理如表1 所示。

表1 TMS570中ESM故障等级划分Tab.1 ESM fault levels classification in TMS570

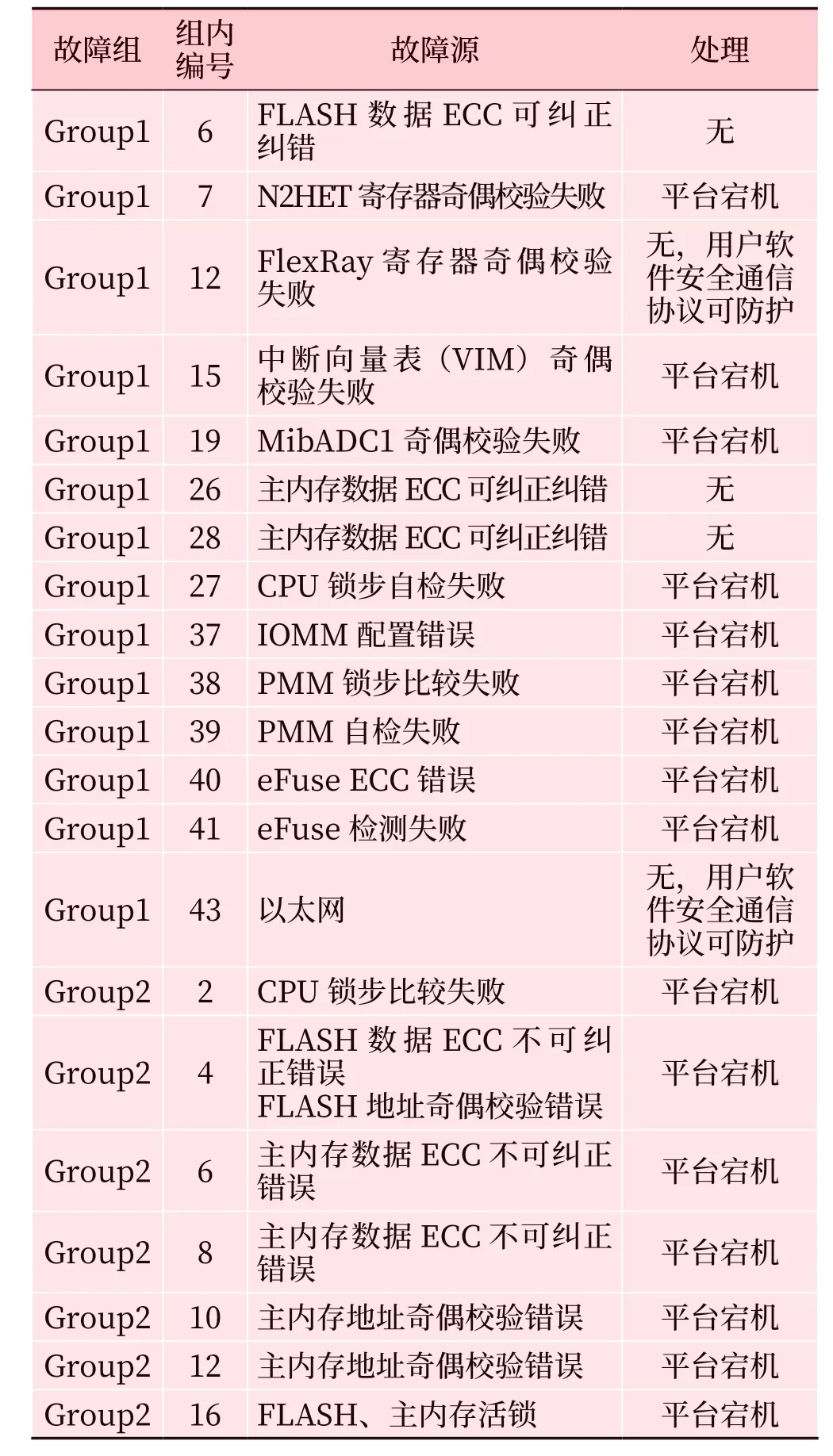

以TMS570LS3137 为例,芯片给出128 个故障通道对应的故障源。本平台中使用CPU 的AD、PWM、FLASH、以太网等资源,针对这些资源,设计了相关ESM 中断的处理,如表2 所示。

表2 本平台中ESM故障处理Tab.2 ESM fault handling in the platform

2.3 启用的自检项及处理方法

对于CPU 自检的具体方法,在EN/IEC61508-2中有明确的指引。EN50129:2018 由于考虑了铁路行业的专有特点,在失效模式与EN/IEC61508 保持一致的情况下,对防护措施/方法做了部分调整,以适应于更严苛的铁路运营安全需要。

根据EN50129 对SIL4 级系统的要求,结合本平台实际应用情况,启用的CPU 主要自检项及处理方法如下。

1)电源

TMS570 内置电压监测(VMON)独立于CPU 运行,用户无法配置和关闭。当CPU 内核和输入输出引脚电压超出指定范围,VMON 会将CPU 强制拉入安全状态。同时,使用TPS65381 作为外部电源管理芯片,属于TMS570 推荐配套的电源管理芯片,可实现安全看门狗功能。

MCU 中有两个电源管理模块采用锁步方式运行,当检测到锁步异常后通过ESM 触发中断。此功能时刻运行,无法关闭。为了检测电源管理模块的锁步机制运行是否正常,电源锁闭自检分两步:比较一致的测试和锁步故障植入测试。本自检只在启动时执行。

2)周期寄存器配置回读

用户软件运行中定期回读所有固定不变的寄存器配置,当发现寄存器数值出现变动,平台进行宕机处理。

3)重启

CPU 的nRST 和nPORRST 引脚自带毛刺滤波,防止错误重启,该功能属于强制项,无法关闭。

4)CPU

TMS570 使用双核锁步技术,双核相差两个CPU 时钟周期运行相同程序,最后通过比较器检测CPU 计算结果是否异常。双核锁步比较失败会通过ESM 触发不可屏蔽中断。强制功能时刻运行,无法关闭。CPU 锁步比较自检是通过故障植入检测CPU 比较器是否正常运行。本检测仅在启动时执行一次;CPU 逻辑自检(LBIST)通过硬件对两个CPU 的寄存器和指令执行结果进行检测,本检测在执行完成后会触发CPU 热启动,仅在启动时执行一次。

5)内存

TMS570 具备ECC 保护功能,在启动时配置执行。当内存检测到1 bit 可纠正错误后,会将修正后的数据存入错误寄存器,同时将修正后的数据回写入内存中,并从内存重新读取。当再一次检测到1 bit 可纠正错误后,CPU 进入活锁状态,触发ESM 中断,需要CPU 重启。此功能在启动后强制启用。同时,CPU 自带硬件内存自检电路(PBIST),可提供对SRAM 的高诊断覆盖率自检,所有片上RAM 都可以检测到,但这个自检会破坏内存中的原有数据,因此仅在启动时执行一次,自检失败后平台宕机。

3 二乘二取二SIL4级安全平台设计

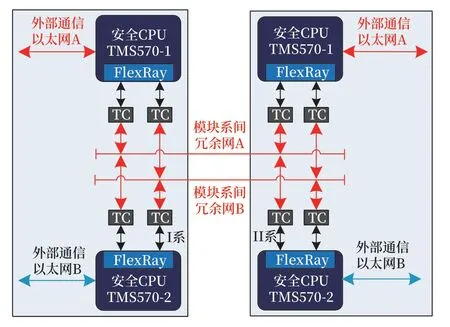

列控系统安全平台一般为三取二或二乘二取二架构。为实现高可靠性和高安全性,本文基于TMS570 搭建了一个二乘二取二的安全平台。TMS570 本身是通过认证的SIL3 级CPU,通过两个CPU 二取架构,配合CPU 自检措施,可以达到SIL4 级功能安全。同时,通过双系二乘架构,可以达到高可靠性的要求。

平台内部通信(系内双CPU 间以及双系间)采用TMS570 自带的Flexray 高速冗余总线,来实现时间同步和数据交互功能;外部通信采用TMS570自带的以太网,来实现和外部系统的大容量数据交互功能。平台架构如图2 所示。

图2 安全平台结构Fig.2 Security platform architecture

4 总结

目前,列控系统安全平台中CPU 安全功能多数由用户软件实现,具有代码繁琐,设计复杂等缺点。凭借集成的安全特性和可供选择的多种通信接口和控制外设,TMS570 为具有安全要求的高性能实时控制应用提供了理想解决方案。本文基于TMS570 设计了一种二乘二取二安全平台,用户只需通过配置和简单的故障处理即可实现安全防护措施,使用户可以将精力放在业务功能层面,为用户带来了极大便利。