180 nm 嵌入式闪存工艺中高压NMOS器件工艺加固技术

2022-12-14陈晓亮孙伟锋

陈晓亮 孙伟锋

(东南大学电子科学与工程学院,国家专用集成电路系统工程技术研究中心,南京 211189)

抗辐射嵌入式闪存工艺在航空航天领域应用广泛,其中高压NMOS 器件对总剂量辐射效应最敏感,对该器件进行加固是提高芯片抗辐射能力的关键之一.本文采用浅槽隔离(STI)场区离子注入工艺对180 nm 嵌入式闪存工艺中的高压NMOS 器件进行加固,实验结果表明该加固器件存在两个主要问题: 1)浅槽刻蚀后进行离子注入,后续热工艺较多,存在显著的杂质再分布效应,导致STI 侧壁离子浓度降低,经过1×105 rad (1 rad=10–2 Gy)(Si)辐照后,器件因漏电流增大而无法关断;2)加固离子注入降低了漏区PN 结击穿电压,不能满足实际应用需求.为解决上述问题,本文提出了一种新型部分沟道离子注入加固方案.该方案调整加固离子注入工艺至热预算较多的栅氧工艺之后,减弱了离子再分布效应.另外,仅在STI 边缘的沟道中部进行离子注入,不影响漏击穿电压.采用本方案对高压NMOS 器件进行总剂量工艺加固,不改变器件的条形栅设计,对器件电学参数影响较小,与通用工艺兼容性好.测试结果表明,器件经过1.5×105 rad (Si)总剂量辐照后,关态漏电流保持在10–12 A 左右,这比传统的STI 场区离子注入加固方案降低了5 个数量级.

1 引言

现代航天技术的发展需要抗辐射半导体器件和芯片技术的支撑,其中基于嵌入式闪存工艺的微控制器和现场可编程门阵列芯片应用广泛.研制这类芯片需要嵌入式闪存(embedded flash,eFlash)工艺.闪存单元的编程和擦除操作需要较高的电压,所以eFlash 工艺通常都提供工作电压为5 V的高压器件来处理这些高压信号.研究表明,二氧化硅中辐射产生电荷的累积量与电场强度相关[1,2].高压器件的氧化硅积累电荷量最大,并且其沟道掺杂浓度相对较低,在eFlash 工艺中对总剂量效应最敏感,是实施抗辐射加固的关键点之一[3−7].

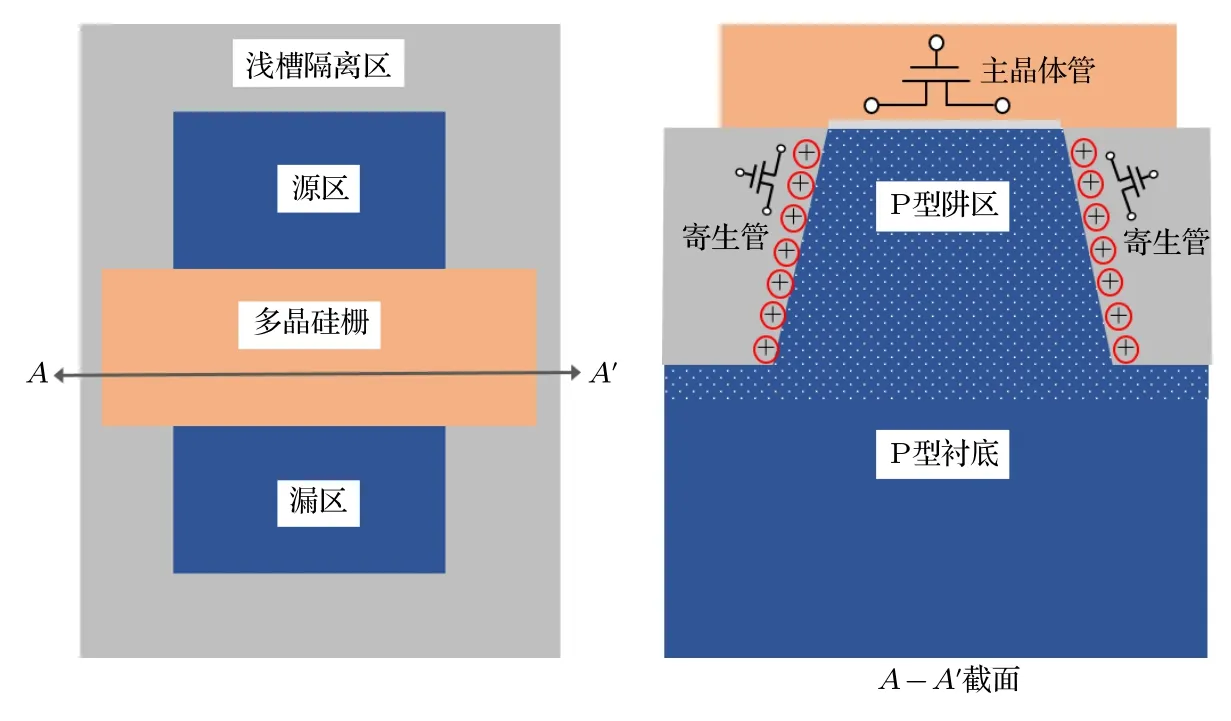

辐射对半导体器件的影响源于其在氧化硅中产生并积累电荷.如图1 所示,当栅极为高电势时,迁移率较高的电子在电场作用下迅速被栅极抽离,而空穴只能通过与氧化硅中的浅能级陷阱作用,缓慢向硅和二氧化硅界面移动.在此过程中,一部分空穴被氧化硅深能级陷阱俘获形成固定电荷,另一部分在氢键作用下在硅和二氧化硅界面形成界面态[8].深亚微米工艺中,栅氧化层厚度一般小于20 nm,总剂量效应产生的电荷易与通过衬底隧穿进入氧化硅的电子中和,对器件的影响基本可以忽略.浅槽隔离(shallow tench isolation,STI)氧化硅厚度通常大于300 nm,在辐照过程中正电荷大量积累在STI 边缘,这降低了N 沟道金属氧化物半导体场效应晶体管(N-channel MOSFET,NMOS)边缘形成的寄生晶体管的阈值电压,增大了NMOS器件关态漏电流,其原理如图2 所示[9−11].

图1 MOS 结构中辐照产生和积累电荷能带示意图[8]Fig.1.Band diagram of radiation induced charge generation and accumulation in MOS structure[8].

图2 辐射导致的STI 侧壁寄生NMOS 示意图Fig.2.Schematic of radiation induced parasitic NMOS at STI sidewall.

为保证芯片在辐照环境下应用的可靠性,需要对器件进行总剂量加固.NMOS 器件的总剂量加固方式有设计加固和工艺加固两种.设计加固通过改变版图设计减小边缘寄生器件的漏电,包括环形栅(或者无边缘栅)结构[12,13],体反向偏置结构[14],虚拟栅极结构[15]以及L 型栅极结构等[16].其中,环栅器件是常用的器件加固方法.采用环栅结构设计的Flash 高压器件,在1.5×105rad (1 rad=10–2Gy) (Si)总剂量辐照后,漏电流相比辐照前没有明显增大[17].尽管环栅器件可以抑制总剂量效应,但是其版图与通用设计不同,这使得环栅器件主要存在两个缺点.首先,环栅器件面积较大,降低了芯片的集成度.其次,设计过程中不能直接使用晶圆代工厂提供的工艺设计工具包、知识产权模块以及单元库等[18,19].这不仅提高了产品设计难度,也延长了产品的开发周期.工艺加固技术在通用工艺基础上对部分关键工艺进行优化以提高器件抗辐射能力.采用工艺加固技术,设计者使用通用的设计方案即可实现芯片抗辐射能力,缩短了开发周期,降低了产品研发难度.器件的工艺加固有两种技术路线.第一,通过在STI 填充材料中引入电子复合中心,减少其在总剂量辐射下产生的电荷总量.例如对STI 填充材料进行硅离子注入或使用富硅氧化硅作为填充材料,引入硅元素形成电子-空穴复合中心,通过减少辐照产生电荷的总量提高器件抗总剂量能力.该技术对栅氧化硅厚度有影响,存在一定的可靠性问题[20,21];第二,优化器件工艺达到减小边缘寄生器件漏电的目的,例如采用STI 场区离子注入技术[22]和超陡倒掺杂阱技术[23]提高STI 侧壁的掺杂离子浓度,增大边缘寄生器件的阈值电压.在这两种技术路线中,前者使用了不同的STI 填充材料,与通用工艺兼容性较差,对器件参数及可靠性也存在较大影响.后者只对边缘寄生器件本身进行工艺优化,兼容性较好,易于实现.

本文采用STI 场区离子注入技术对180 nm eFlash 工艺中的高压NMOS 器件进行总剂量工艺加固,研究了其总剂量特性,提出了该技术在应用中存在的问题.有针对性地提出了一种新型部分沟道离子注入解决方案,并对其进行验证.

2 传统工艺加固方案和测试分析

2.1 STI 注入加固技术和实验方案

本研究首先采用传统的STI 场区离子注入技术对180 nm eFlash 工艺中的5 V NMOS 器件进行加固.其原理是在STI 有源区边缘注入P 型离子,提高边缘寄生管的沟道掺杂浓度,器件版图如图3(a)所示.该技术在STI 浅槽刻蚀完成后,生长15 nm 厚的STI 线氧化层用以修复刻蚀造成的有源区损伤.接着通过光刻工艺定义整个NMOS区域为P 型加固离子注入窗口,PMOS 器件区域则被光刻胶掩蔽.在STI 隔离氧化硅填充之前进行场区加固离子注入,工艺示意如图3(b)所示.为减小对主NMOS 器件的影响,用氮化硅作为NMOS有源区的注入阻挡层,只对STI 侧壁和底部进行离子注入.

图3 传统的STI 场区离子注入加固技术示意图 (a)器件版图;(b)工艺示意图Fig.3.Schematic of traditional ion implantation technology on STI field region: (a) Layout of the device;(b) diagram of the process.

测试的器件宽长比W/L=10 µm/0.55 µm,栅氧厚度为16 nm.制作的样品加固注入实验条件如表1 所示.其中样品#1 为对照组,采用通用的eFlash 工艺,不进行离子注入加固;样品#2 和#3都采用场区离子注入加固技术,注入杂质为铟(In),其剂量分别为5×1013cm–2和8×1013cm–2,能量均为120 keV,后续与阱注入离子共同退火激活.除此以外,其他工艺流程与样品#1 完全相同.总剂量辐射实验采用60Coγ射线,剂量率固定为50 rad(Si)/s,辐照过程中器件为开态偏置(栅极电压为5 V,其余端口接地).对辐射实验前以及总剂量分别为5×104rad(Si),1×105rad(Si)和1.5×105rad(Si)时器件的VG-ID特性曲线进行测试,测试时漏端电压VD为5 V.

表1 STI 场区离子注入实验分片方案Table 1.Split condition of ion implantation for experiment.

2.2 总剂量实验测试结果与分析

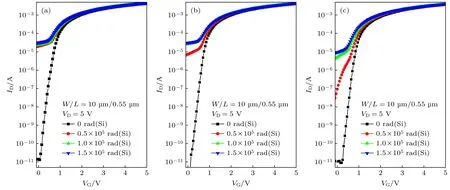

辐射实验前测试3 个样品的关态漏电流均为10–12A 左右.分别对样品#1,#2 和#3 进行总剂量辐照实验,辐照后的VG-ID特性曲线如图4 所示.图4(a)表明,未经STI 场区加固注入的样品#1经过5×104rad(Si)总剂量辐照后,关态漏电流急剧增大到超过10 µA,器件无法关断.再继续增大辐照总剂量,器件关态漏电流趋于饱和,说明边缘寄生管已处于强反型状态.如图4(b)和图4(c)所示,同样经过5×104rad(Si)总剂量辐照后,采用STI 场区离子注入加固的器件关态漏电流随加固注入离子剂量的增大而降低,样品#2 和#3 的漏电流分别比样品#1 低1 个数量级和2 个数量级.经过1×105rad(Si)和1.5×105rad(Si)总剂量辐照后也得到类似的趋势.实验结果表明,STI 场区离子注入加固技术能够提高器件的抗总剂量能力.辐照总剂量越低时,加固效果越显著.加固注入剂量越高,器件抗总剂量能力越强.

图4 的测试结果表明,虽然STI 场区离子注入工艺提高了器件抗总剂量能力,但是当辐射总剂量超过1×105rad(Si)后,器件的漏电仍然超过1µA,无法满足实际应用需求.这是因为STI 场区离子注入是在STI 刻蚀完成之后进行的,经过后续的退火和栅氧生长等热工艺过程,掺杂离子扩散造成STI 边缘沟道区域掺杂浓度不断下降,最终影响加固效果.相比逻辑工艺,eFlash 工艺中增大了16 nm 厚的高压器件栅氧化层工艺和9 nm 厚的存储单元隧穿氧化层工艺,其工艺时间较长,且温度均在900 ℃以上,这造成了STI 边缘离子的再分布效应.使用TCAD 软件对STI 边缘离子浓度进行了仿真分析,仿真结构如图5(a)所示.在相同STI 场区离子注入剂量下,对比逻辑工艺和eFlash工艺STI 边缘掺杂离子的分布情况.分别取距离表面10 nm,150 nm 及300 nm 处的离子浓度分布进行比较,如图5(b)所示.结果表明,在有源区结深范围内,eFlash 工艺的STI 边缘离子浓度低约1 个数量级,这影响了总剂量加固注入的效果.

图4 5 V NMOS 器件总剂量效应测试结果 (a) 无STI 场区离子注入;(b) 场区离子注入剂量5×1013 cm–2 ;(c) 场区离子注入剂量8×1013 cm–2Fig.4.Total ionizing dose test results of 5 V NMOS device: (a) Without STI field implantation;(b) STI filed implantation dose 5×1013 cm–2 ;(c) STI filed implantation dose 8×1013 cm–2.

图5 STI 边缘掺杂离子浓度仿真 (a) STI 结构中离子浓度分布图;(b) 不同工艺热预算下不同位置的离子浓度分布对比Fig.5.Simulation of doping concentration at STI edge region: (a) Ion distribution of STI structure;(b) doping profile comparison at various positions under different thermal budget.

2.3 加固工艺对漏击穿电压的影响

MOSFET 关断时,漏区的反偏PN 结将承受高电压.对NMOS 器件,漏端PN 结由重掺杂N 型漏区和轻掺杂P 型阱区组成,能够承受的最大电压为PN 结反向击穿电压.漏区PN 结可以近似为单边突变结,击穿电压VBD主要由轻掺杂一侧(P型阱区)的电离杂质浓度决定,由(1)式表示:

其中εSi为硅的介电常数,Em为硅材料能承受的最大电场,q为电子电量,N为轻掺杂一侧的电离杂质浓度.

由(1)式可知,阱区的掺杂浓度越低,器件漏击穿电压越高.180 nm eFlash 工艺中的5 V NMOS器件,P 型阱区掺杂剂量为1012cm–2,而STI 边缘的场区加固注入P 型离子剂量为1013cm–2.加固注入比阱区掺杂剂量高1 个数量级,如图6 所示,加固离子注入在漏端PN 结耗尽区STI 边缘形成易击穿区.

图6 STI 场区离子注入对漏击穿电压的影响示意图Fig.6.Schematic of the impact of ion implantation on drain breakdown voltage.

为了验证上面的理论分析,测试了不同STI场区加固注入剂量的器件的漏击穿电压.所测器件沟道宽度为10 µm,沟道长度分别为0.55 µm 和10 µm.测试时栅极、源极和体电压为0 V,漏端电压从0 V 开始以50 mV 为单位逐渐增大,定义漏电流为1 µA 时的漏端电压为击穿电压.图7 所示测试结果表明,两种沟道长度的器件漏击穿电压变化趋势是一致的.未经加固注入的器件漏击穿电压高于12 V,随着加固注入剂量的增大,器件漏击穿电压逐渐降低.当加固注入剂量达到1014cm–2时,漏击穿电压低于11 V,电路无法正常工作.

图7 STI 场区加固注入剂量对器件漏击穿电压的影响Fig.7.Impact of hardening implantation dose on drain breakdown voltage.

3 新型总剂量加固解决方案

3.1 新型部分沟道离子注入加固方案的提出

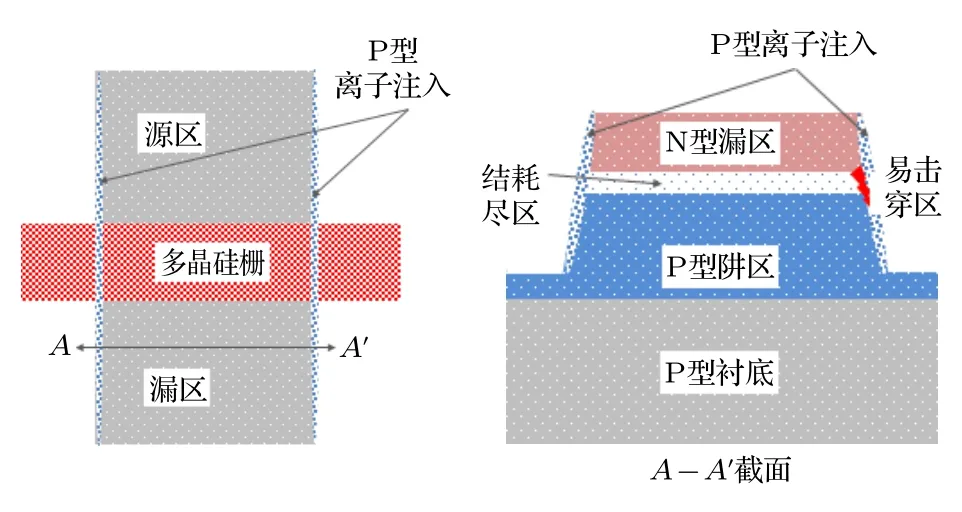

图4 表明,在经过总剂量5×104rad(Si)辐照后,边缘寄生器件为强反型状态,未加固器件漏电流已超过10 µA.为了避免加固注入对器件漏击穿电压的影响,提出如图8 所示的新型部分沟道离子注入加固方案.在该加固方案中,STI 边缘寄生管由3 个NMOS 管N1,N2和N3串联组成,其中只对N2管沟道进行加固注入.N2管沟道掺杂浓度最大,阈值电压最高,决定了边缘寄生管的漏电流.

与图3 所示的STI 场区离子注入加固方案相比,该方案主要有两方面的创新: 1)通过光刻工艺形成如图8 所示的加固注入窗口区,提高沟道中部的掺杂浓度,减小总剂量效应引起的漏电,该注入窗口不包含漏区,避免影响器件漏击穿电压;2)调整离子注入加固工艺至栅氧工艺之后,减小eFlash工艺热预算造成的离子再分布效应,提高了STI边缘离子浓度.在现有工艺能力下,加固注入窗口尺寸最小可做到0.25 µm×0.25 µm.在180 nm eFlash工艺中,5 V NMOS 器件最小沟道尺寸W/L=0.6 µm/0.55 µm,所以该技术方案可以满足高压NMOS 器件的加固注入需求.

图8 新型抗总剂量加固注入器件结构和能带图Fig.8.Device structure and band diagram with the new hardening ion implantation.

3.2 新型加固方案测试分析

采用上述新型部分沟道离子注入加固方案的测试器件宽长比为W/L=10 µm/0.55 µm,工作电压为5 V.器件的栅氧厚度为16 nm,多晶硅栅厚度为100 nm.在淀积多晶硅栅后进行光刻和加固离子注入,杂质为铟(In),未增加额外退火工艺.样品#4,#5 和#6 的注入剂量分别为2×1013cm–2,5×1013cm–2和8×1013cm–2,注入能量均为250 keV.对器件进行总剂量1×105rad(Si)和1.5×105rad(Si)辐照实验,并测试器件VG-ID特性,结果如图9所示.对比图9(b)和图4(b)表明,加固离子注入剂量为5×1013cm–2时,1.5×105rad(Si)总剂量辐射后,采用部分沟道注入加固方案的器件漏电流为10–10A 左右,比STI 场区离子注入加固方案低约5 个数量级.同时图9 也表明,器件抗总剂量能力随着加固离子注入剂量的增大而提高.注入剂量为 8×1013cm–2时,器件经过 1.5×105rad(Si)辐照后,保持漏电流在10–12A 左右的较低水平.采用新型部分沟道离子注入加固方案的器件抗总剂量能力得到显著提升.

图9 采用部分沟道离子注入器件总剂量效应 (a)加固注入剂量2×1013 cm–2;(b)加固注入剂5×1013 cm–2 ;(c)加固注入剂量8×1013 cm–2Fig.9.TID effect of the devices with partial channel hardened implantation: (a) Hardening implantation dose 2×1013 cm–2 ;(b) hardening implantation dose 5×1013 cm–2 ;(c) hardening implantation dose 8×1013 cm–2.

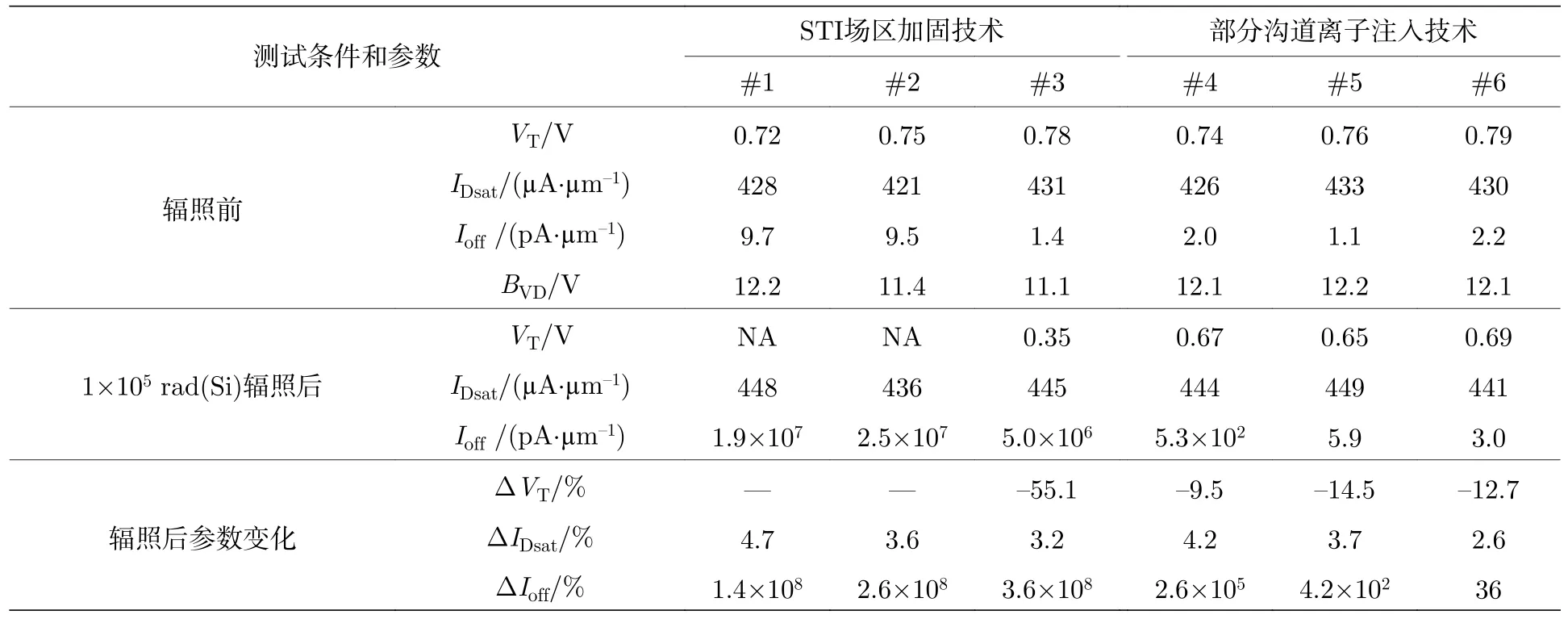

表2 总结了STI 场区离子注入加固技术和新型部分沟道离子注入加固技术的总剂量实验测试数据.结果表明,在辐照实验前器件的阈值电压(VT)随加固注入剂量的增大而略微增加,这是由于注入杂质不可避免的进入主器件沟道区造成的;所有样品的饱和电流(IDsat)在420—430 µA/µm,漏电流(Ioff)都在10 pA/µm 以下.采用STI 场区加固技术的器件漏击穿电压(BVD)受加固注入剂量影响较大,这在前文已经具体分析过.采用部分沟道离子注入技术的样品的漏击穿电压则稳定在12 V左右,不受加固注入剂量影响.经过1×105rad(Si)总剂量辐照后,样品#1 和#2 漏电流过大导致器件无法关断,样品#3 的阈值电压为0.35 V,比辐照前降低了55.1%,漏电流达到5 µA.采用部分沟道离子注入技术的样品#4—#6 辐照后阈值电压降低10%—15%,这是栅氧总剂量效应引起的平带电压漂移造成的,与加固注入剂量无关.加固注入剂量为超过5×1013cm–2时,辐照后仍保持漏电流在10 pA/µm 左右.表2 还表明,总剂量辐照对器件饱和电流的影响较小,无论是否采用离子加固注入,所有样品的饱和电流在辐照后都略微增大,幅度小于5%.

表2 两种注入加固方案测试结果对比Table 2. Comparison of two total ionizing dose hardening methodology.

4 结论

本文研究了180 nm eFlash 工艺中5 V NMOS器件的总剂量工艺加固技术.首先采用传统的STI场区离子注入技术进行5 V NMOS 总剂量加固,结果表明该方案主要存在两个问题: 1) eFlash 工艺较多的热预算造成STI 侧壁离子再分布,经过1×105rad(Si)总剂量辐照后器件漏电流大于1 µA,不能满足实际应用需求;2)加固离子注入提高了器件漏区衬底掺杂浓度,降低漏击穿电压,影响器件正常工作.为解决上述问题,本文提出了一种新型的部分沟道离子注入加固方案,主要有两方面的创新: 1)把加固离子注入工艺调整至栅氧工艺之后,减小掺杂离子再分布效应,提高STI 边缘有效离子浓度;2)通过光刻工艺,在STI边缘沟道中部形成矩形注入窗口,加固注入不影响源漏区离子分布.结果表明,在相同加固注入剂量下经过1.5×105rad(Si)总剂量辐照后,采用新型部分沟道离子注入技术的器件漏电流比STI 场区注入方案低5 个数量级以上,器件总剂量能力得到显著提升.有效解决了eFlash 工艺中高压NMOS 器件的抗总剂量能力与漏击穿电压之间的矛盾,同时也为其他工艺中高压NMOS 器件的抗辐射工艺加固提供参考.