多通道电离层探测系统数据传输设计

2022-10-15张启安杨国斌刘桐辛姜春华

张启安,杨国斌,刘桐辛,姜春华

(武汉大学 电子信息学院,湖北 武汉 430079)

0 引 言

针对电离层的探测,武汉大学电离层实验室自主研发了一套利用短波(High Frequency,HF)与超短波(Very High Frequency,VHF)实现电离层探测的多通道探测系统,该系统通过灵活配置硬件可以实现电离层斜返探测、闪电探测与流星探测。多通道探测系统使用本地探测的探测模式,利用上位机软件与USB 总线来改变探测系统的硬件配置,以适应不同的探测任务需求,同时USB 总线保证了数据的实时上传。对于不同的探测任务,不仅需要根据探测目标制定不同的雷达波形参数,还需要改变发射机功率与天线尺寸。本地探测的情况下,发射天线与接收天线共站,导致接收系统很容易受到发射机带来的干扰,随着功率与天线尺寸的增大,近场信号的耦合以及地杂波的影响会相应地增加,USB 总线的数据传输带越发困难。实际探测显示,当使用大功率的发射机进行探测时,USB 总线受到的干扰会导致大量数据上传失败。

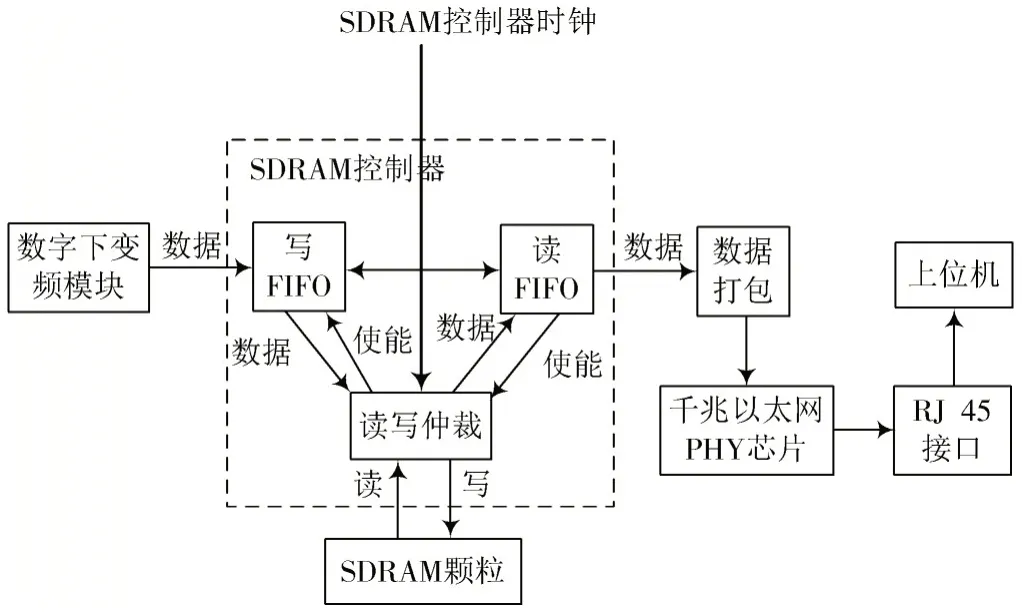

多通道探测数据具有带宽大、实时传输的特点。为了避免在收发共站的探测体制下出现传输失败的情况,本文设计了一种基于SDRAM 进行数据缓存的方案,并针对多通道阵列的大数据带宽,使用千兆以太网进行数据的传输,解决了多通道探测系统因为杂波干扰导致的数据上传失败问题。通过对SDRAM 内部逻辑的研究,本文方案使用FPGA 作为主要控制器,将SDRAM 与控制器包装成FIFO(First In First Out)接口,探测数据在经过数字下变频之后存入写FIFO 中,并在数据上传时读取SDRAM,将数据存入读FIFO 中等待被取出,千兆以太网的数据流传输使用网口芯片与FPGA 之间的逻辑接口实现。数据在FPGA 中进行打包,通过以太网传输至上位机。该设计具有稳定性好、传输速度快的特点。

1 硬件设计

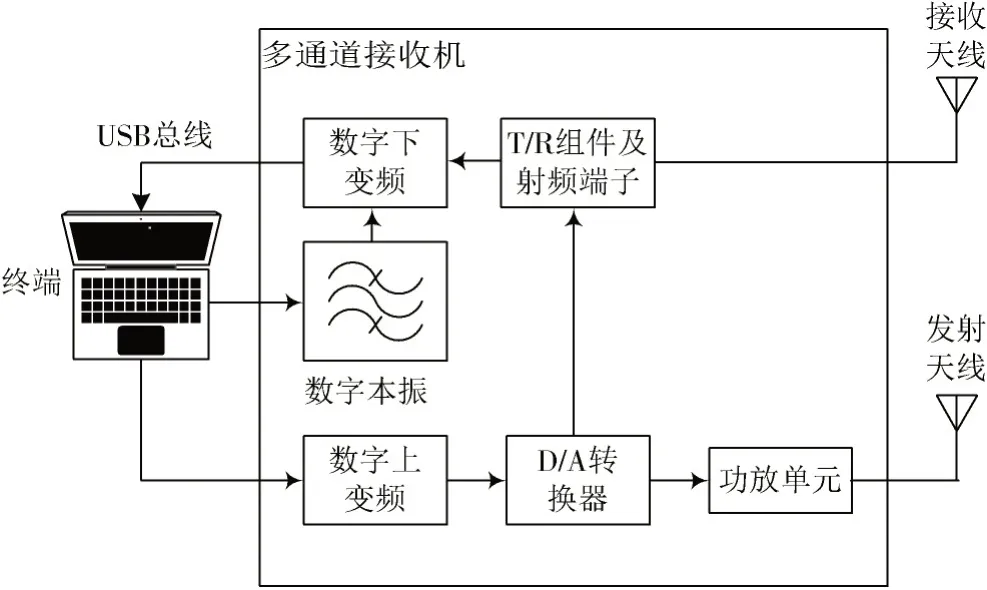

武汉大学多通道探测系统的探测任务包括电离层探测、闪电探测、流星余迹探测等。基于原有的多通道探测系统,武汉大学电离层实验室已经成功得到大量电离层探测数据。探测系统的基本结构如图1 所示,发射信号脉冲通过数字上变频或者直接数字信号生成器(DDS)产生,并通过发射机功放与射频天线发出。信号通过多通道天线阵列接收并在模拟端进行初步混频得到中频信号,之后通过A/D 转换器与数字下变频电路得到基带IQ 信号并使用USB 总线进行数据的上传。多通道探测系统采用本地收发的探测模式,发射天线与接收天线在同一场地,在这种探测模式下,发射天线与接收机之间无法有过大的距离,当波形发射时,为防止发射信号的能量泄漏到接收机射频端子而导致元器件损坏,探测系统使用射频开关屏蔽发射信号,并在信号脉冲发射结束之后,开放接收通道,对信号进行处理与上传。数据的处理与上传需要在下一次信号发射之前完成。

图1 多通道探测系统架构

通常在进行电离层观测时,需要连续发射频率递增的脉冲信号,完成电离层扫频探测。而在流星与闪电探测中,为了观测流星与闪电随时间的变化情况,也需要连续发射单频点信号,这对数据的及时上传速度提出了要求。为了使数据可以及时上传,武汉大学多通道电离层探测系统制定了合适的探测距离,并使用USB 2.0 总线作为数据上传总线。

多通道探测系统工作在HF 与VHF 频段,这部分频段的电波辐射较大,会影响到数据在总线上的正常传输。由于USB 总线的抗干扰能力较弱,受限于当前工程应用的场地、本地收发的探测模式以及实际探测中有限的屏蔽手段,在大功率的辐射背景下,如电离层斜返探测、流星探测、闪电探测等的情况下,USB 总线无法高速且准确地传输数据。在电离层垂直探测时,发射机功率较小,大部分数据可以被正常传输,但是进行流星与闪电探测时,随着发射机功率增大,近场耦合导致的干扰变得严重,导致USB 总线受到强烈干扰,数据上传错误率变大。在这种情况下,需要寻求数据缓存的方案,使传输链路在干扰减弱的情况下再进行数据的上传。

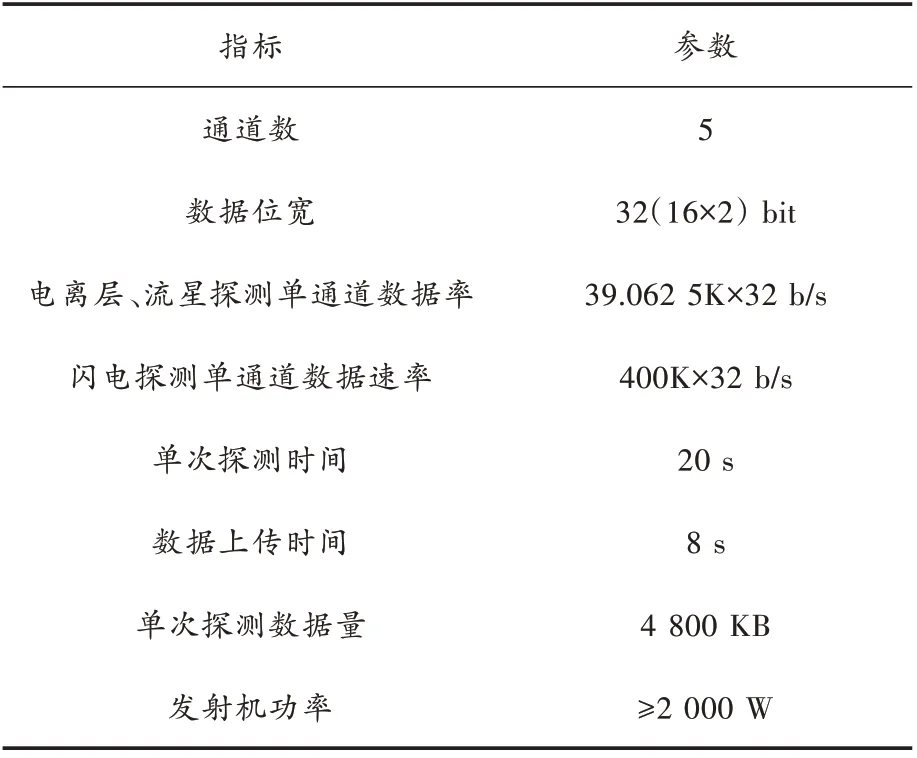

多通道探测系统使用16 位的A/D 转换器,并在数字下变频解调后得到16 位的基带IQ 数据,在电离层探测时,单个通道的数据即基带数据速率约为2 Mb/s,并考虑到I、Q 数据速率与5 个通道的数据带宽,总计高达13 Mb/s,多通道探测系统的数据指标如表1 所示。

表1 多通道探测系统数据指标

考虑到多通道探测的数据特点,这里使用动态存储设备芯片作为探测数据的缓存措施,其中同步动态随机存储器(Synchronous Dynamic Random-Access Memory,SDRAM)是一种大容量动态存储随机存储器,在计算机体系中通常作为CACHE 使用,非常适合作为数据的中间缓存器件,其中,动态指的是由于SDRAM 的存储结构是通过电容的充放电来实现数据的存储,所以需要定时对芯片进行刷新操作来保持数据不丢失。为满足多通道设备的实时传输,选择使用Hynix(海力士)公司的HY57V281620 系列SDRAM 作为本文的存储芯片,该SDRAM 支持16 位数据读写,拥有4 个bank,总容量达到134 217 728 bit,满足多通道探测一次的数据容量,HY57V281620A 最高支持100~200 MHz 的时钟速率,带宽超过1 Gb/s,大于多通道探测所需要的传输速率,满足探测所需要的数据存储需求。

同时,不同的探测目标有不同的尺度特征,通过改变硬件配置可改变探测的距离分辨率。在进行电离层探测时,设置距离分辨率在2 km 量级,而对流星或闪电进行探测时,需要增加距离分辨率到400 m 量级,数据带宽与距离分辨率成正比,数据带宽的增加为数据的上传带来了挑战。为了保证在探测结束后数据可以被实时上传到上位机,需要使用高效的数据总线。

考虑到多通道探测系统的大数据量与实际探测中数据传输的可靠性,本文使用千兆以太网实现多通道数据的高速传输,相对于USB 总线,以太网抗干扰能力较强,可靠性高。以太网支持远距离传输,其传输线路的长度可方便实现实际探测的现场部署。千兆以太网传输通过FPGA 实现数据包的打包,并通过RGMII 接口传输给以太网PHY 芯片,以太网PHY 芯片使用VITESSE公司的VSC8601以太网芯片,通过配置,支持10M/100M/1 000M 以太网协议。

数据的传输结构流程如图2 所示。当数据经过数字下变频之后,数据先通过SDRAM 进行缓存,使用Verilog 语言在FPGA 中设计出SDRAM 的控制器,并把SDRAM 与控制器包装成一个FIFO 的接口。在得到上位机探测结束的标志之后,数据将通过千兆以太网传输至上位机,根据以太网的协议,构建以太网的数据包并由上位机进行接收,上位机在经过CRC32(32 位循环冗余校验)之后得到正确的数据包,并取出数据。

图2 数据传输部分流程图

2 SDRAM 控制器的设计

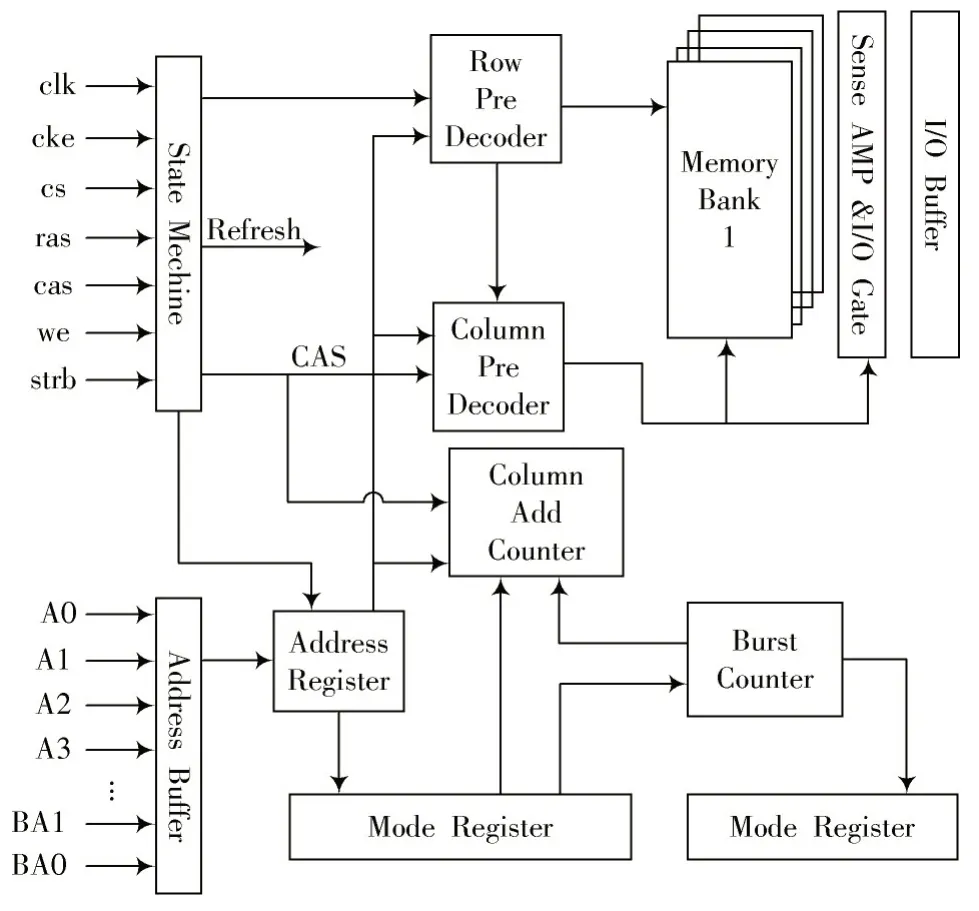

SDRAM 具有读写速度快、精度高、价格低廉的特点,图3 所示为典型的SDRAM 内部结构图。

图3 典型的SDRAM 内部结构

SDRAM 中的模式寄存器会寄存控制器对SDRAM发送的操作指令,包括读、写、刷新、预充电等操作,同时模式寄存器在SDRAM 上电之后会将SDRAM 的读写模式、突发操作长度等配置寄存下来。具体数据的存储空间通过地址线提供,其中BA1,BA0 指出具体存储的bank,其他的地址线标示具体数据存储空间的行列地址。16 位的双向数据总线用于16 位数据的存储与读出,同时SDRAM 支持突发读写与掩码操作,为特殊的数据编码提供便利。

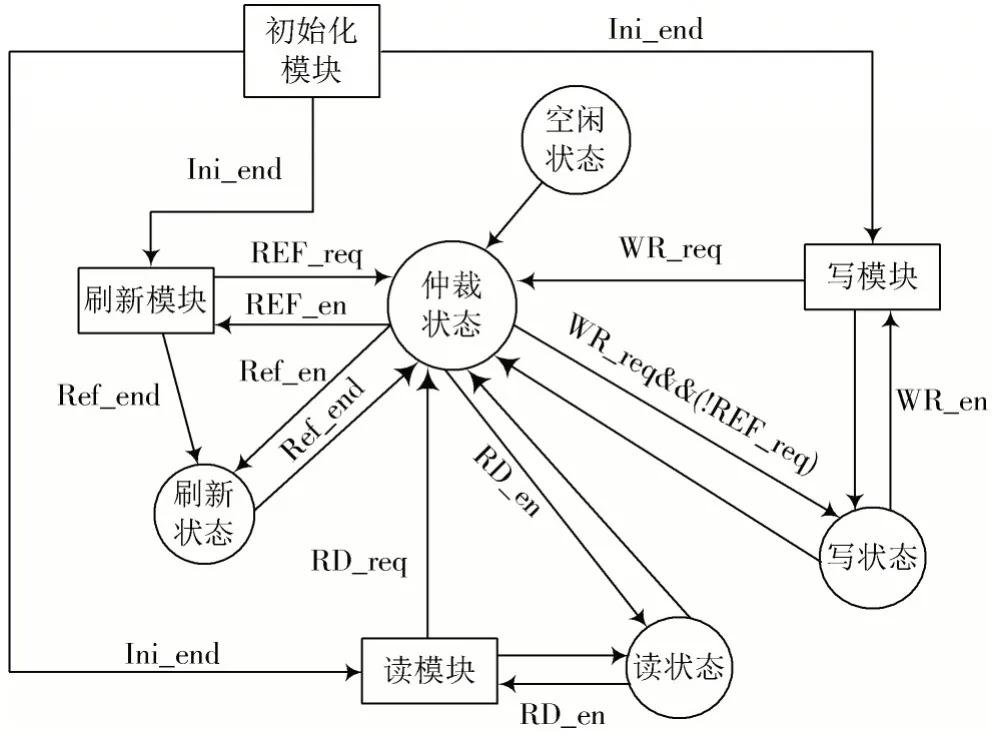

SDRAM 因其同步总线的机制与动态刷新操作,为控制程序的设计带来了难度。利用状态机与模块化设计来处理SDRAM 各个操作之间的关系比较合适,本文利用模块化设计将SDRAM 的各个操作进行模块划分,并将各个模块外挂在仲裁模块下。

该设计具有模块划分清晰、读写效率高的特点,同时也为维护与移植带来了便利。各个状态之间的流程如图4 所示,仲裁状态实现刷新操作与读、写操作之间的仲裁,其中刷新操作的优先级高于读写操作,写的优先级高于读操作的优先级。

图4 SDRAM 控制器状态机

SDRAM 在上电之初,需要对整个芯片进行初始化操作,根据标准的工业流程,SDRAM 上电之后需要至少200 μs 的无操作时间,之后在经过预充电和几个周期的刷新操作之后,通过写入模式寄存器来设置SDRAM 的读写模式、掩码、tRCD、突发长度等。初始化模块通过计数器实现各个操作的顺序执行。

根据芯片手册,在配置完SDRAM 的读写模式之后,需要等待一定长的时间后才可以对SDRAM 进行基本的操作。程序使用一个电平信号作为初始化结束的标志,并与总复位一起作为其他模块的复位信号。图4 中共有5 个模块,其中仲裁模块作为顶层模块没有直接画出,其他模块都挂在仲裁模块下(初始化模块,刷新模块,读、写模块),REF_MODULE 为刷新模块,在刷新模块中根据芯片手册提供的最大刷新周期与时钟频率设计一个计数器,并适当减少刷新请求的间隔,为仲裁时间提供余量。

当刷新时间到达预计时间,刷新模块向仲裁模块发送刷新请求REF_req,在得到刷新使能信号REF_en 时,开始执行刷新操作,此时,SDRAM 控制器通过向模式寄存器输入刷新指令并等待几个时钟周期(根据芯片手册要求)后,开始执行刷新操作,仲裁模块在仲裁状态下收到刷新请求信号REF_req 后,状态转移到刷新(REF)状态,并等待刷新结束信号REF_end,收到结束信号后,状态回到仲裁状态(SW)并等待读写请求。数据在数字下变频后通过异步FIFO 完成数据的跨时钟传输,SDRAM 的写入带宽需要大于数字下变频的基带速率。

以闪电探测为例,其基带速率为400K×32 b/s,这里使用100 MHz 的时钟驱动SDRAM 的控制器,使SDRAM的数据带宽远大于基带速率的带宽,这样设置使异步FIFO 的读端的速度远大于写端的速度,当FIFO 中的数据达到一定的大小后,就读取FIFO 中的数据并执行SDRAM 的写操作。

对SDRAM 进行写操作时需要先进行bank、行与列的指定;在初始化阶段配置SDRAM 的参数后可以指定突发写入的数据量,以减少SDRAM 指令线资源的被占用情况,增加相对带宽;在写完一行的数据之后,需要对新的一行进行预充电操作。介于这些考虑,设置一次性写入的数据量为SDRAM 一行的数据大小,单次突发写入4 个数据,并在写完一行或被打断后进行刷新操作。

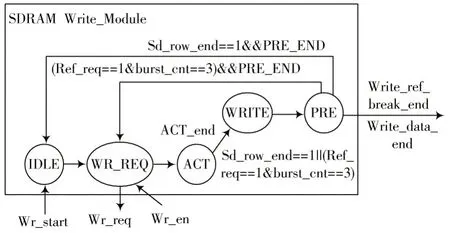

写模块状态机如图5 所示。

图5 写模块状态机

写模块中的FIFO 在达到一定数据量后状态从空闲状态跳转到写请求状态并向仲裁模块输出写请求信号,当仲裁状态机在仲裁状态且没有刷新请求时,就会处理请求并给出写能信号,并且进入写状态,写模块在收到写使能信号后向SDRAM 发送写入指令并开始突发写入数据。此时记录写入的行、列地址与数据量,同时写模块还有一个计数器去记录突发写入的个数,在完成一行数据的写入之后,状态跳转到预充电状态并在预充电结束后,向仲裁状态机发出写结束脉冲Write_data_end,这时仲裁状态机回到仲裁状态,写状态机跳回到空闲状态。刷新请求也作为该模块的一个输入,当处于写入状态的时候,收到了刷新请求,就需要打断写操作来保证及时的刷新数据,但是一次突发写不可以被打断,所以在收到刷新请求,并在收到一次突发写完成之后,就进入预充电状态,并在结束后发出Write_ref_break_end 信号。同样,仲裁状态机在收到该脉冲后回到仲裁状态。写状态机此时回到写请求状态拉高写请求,并保留此次的数据地址以便下次的读写,在刷新结束之后直接开始继续写入直到一行数据完成。

读模块与写模块的思路类似,只是处于最低优先级,所以读模块的使能在刷新与写请求为低的时候才能有效。

读模块的请求条件是:读FIFO 中的数据小于一定的数据量时,就向仲裁状态及时发送突发读请求,并在没有刷新和写操作时从SDRAM 读取数据。在实际运用中,为了保证数据的上传没有受到干扰,读与写操作实际上是分离的,这为实际的程序设计带来了便捷。

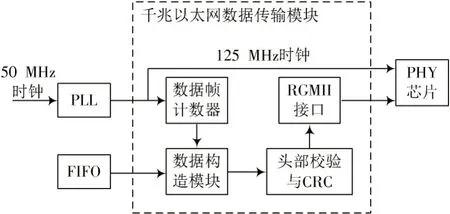

3 千兆以太网传输设计

为了保证高速数据的可靠传输,需要使用高速数据总线完成数据的上传,使用千兆以太网进行数据的传输。千兆以太网具有高效、高速、高性能的特点,通常用于大数据量的场合,比如视频传输等情况。本文设计中使用FPGA 与千兆以太网PHY 芯片实现数据传输的物理层连接。

考虑到多通道探测系统的数据格式,每个通道需要使用4 个字节来传输基带I、Q16 位的数据,每次脉冲携带300 个距离门信息,所以每次打包600 个数据,使用2 个数据包传输一次探测的数据。当收到数据读取的指令后(如某次探测结束,或者某一阶段探测结束,根据具体实验制定),就会从SDRAM 中读取数据,千兆以太网带宽小于SDRAM 的读取带宽,所以使用异步FIFO 进行数据位宽与时钟域的切换。

以太网的数据格式如图6 所示,根据以太网的格式,本文需要将数据包装成图6 所示格式后,才可以被上位机识别。

图6 以太网帧构造方式

以太网发送程序如图7 所示。

图7 以太网帧传输模块设计

为了实现底层数据的正确传输,在物理层会有由7个55 组成的前导同步码,并使用一个字节的帧起始界定符来表示一帧的开始,在以太网帧头中设置源地址与目的地址,并确定以太网的协议类型为UDP 协议,在IP首部与UDP 首部确定源IP 地址与目的IP 地址并计算首部校验和,之后是数据段,此时拉高FIFO 的读使能并将数据拼接进来,最后进入CRC32 校验模块并将生成的4 个字节的校验数据拼接到数据流的结尾。

由于只实现数据的上传,可以自主设置源地址并根据计算机的物理地址设置目的地址,并以此检验并添加头部和,最后通过两倍输出数据速率(Out Double Data Rate,ODDR)源语将数据转化为RGMII 接口的数据格式并通过连接PHY 芯片的TX 接口发出,其中以太网的时钟通过PLL 得到RGMII 的125 MHz 时钟。根据VSC8601 的芯片特性,设置输出时钟与数据相位差的合适值,通过使用Vivado 的时序约束工具将输出数据与时钟的相位差约束在合适位置。

4 实际结果

在本地探测的情况下,使用武汉大学多通道探测系统对电离层进行探测,结果如图8 所示。

图8 USB 总线受到干扰

探测系统使用2 kW 功率的发射机,当脉冲被发射后,此时USB 总线受到干扰,实验数据实时上传困难,在扫频达到约9 MHz 后数据上传失败,导致数据全部为0,在图中显示信噪比为0。对探测系统的传输链路进行改进之后,得到图9 的正常的电离层探测数据,可以看见,典型的电离层回波图在进行长时间探测后,系统可以稳定运行,没有出现数据传输失败的状况。在大功率发射的探测场景中,数据上传链路也可以稳定工作,验证了系统的可靠性与稳定性。

图9 改进后的多通道探测系统

5 结 论

本文针对多通道探测系统数据上传阶段,由于干扰导致数据传输困难的问题,设计了一种基于SDRAM 与千兆以太网的数据缓存与传输方案,并给出了具体程序设计思路。本文给出了具体实验结果,与之前的实验数据进行对比,得出该设计具有稳定可靠、易维护、数据传输速度快、抗干扰能力强的特点。