基于开关瞬态反馈的SiC MOSFET有源驱动电路

2022-09-14陈梓健苗轶如杨江涛

刘 平 陈梓健 苗轶如 杨江涛 李 伟

基于开关瞬态反馈的SiC MOSFET有源驱动电路

刘 平 陈梓健 苗轶如 杨江涛 李 伟

(湖南大学电气与信息工程学院 长沙 410006)

受内部寄生参数与结电容的影响,碳化硅(SiC)功率器件在高速开关过程中存在极大的电流电压过冲与高频开关振荡,严重影响了SiC基变换器的运行可靠性。因此,该文首先对SiC MOSFET开关特性进行深入分析,揭示栅极电流与电流电压过冲的数学关系;然后提出一种变栅极电流的新型有源驱动电路;通过对SiC MOSFET开关瞬态的漏极电流变化率dd/d、漏-源极电压变换率dds/d以及栅极电压gs的直接检测与反馈,在开关过程的电流和电压上升阶段对栅极电流进行主动调节,抑制电流电压过冲与振荡;最后在多个工况下对本文所提方案进行实验验证。结果表明,与常规驱动方案相比,该文方法减小了30%~50%的电流电压过冲,有效抑制振荡与电磁干扰,提高了SiC MOSFET变换器的运行可靠性。

碳化硅MOSFET 有源驱动 栅极电流 电流过冲 电压过冲

0 引言

与传统硅基功率器件相比,碳化硅(Silicon Carbide, SiC)MOSFET具有宽禁带、击穿与阻断电压高、导热特性好、开关速度快等优点[1-2],在电动汽车、航空航天、新能源等领域拥有传统功率器件无法比拟的巨大优势[3-4]。然而,随着SiC MOSFET开关速度的增加,器件的开关特性对内部寄生参数和结电容非常敏感,研究表明10kV SiC MOSFET的d/d高达140V/ns[5],导致在高速开关过程中极易产生严重的电流、电压过冲与振荡[6-7],同时加剧电磁干扰(Electromagnetic Interference,EMI)的影响,增加器件损耗,缩短寿命[8-10]。

针对以上问题,国内外学者提出了多种SiC MOSFET电流、电压过冲与振荡的抑制方法,如并联RC缓冲电路[11]、低杂散电感的封装设计[12]、优化回路PCB布局[7]、增大栅极电阻[13]等,但是这些方法的抑制效果有限或需要在功率电路中加入其他元件,额外增加损耗并可能产生过电压、过电流等问题。

与上述方法相比,有源驱动电路(Active Gate Driver, AGD)是在常规驱动电路(Conventional Gate Driver, CGD)基础上增加由有源器件构成的电路,在SiC MOSFET开关过程的特定阶段改变驱动电路的结构,从而对SiC MOSFET的开关性能进行优化[14],受到了国内外学者的广泛研究,相继提出了变栅极电阻[15-16]、变栅极电压[17-18]和变栅极电流[14,19]三种方案。文献[15-16]采用短路电阻法控制不同阶段的栅极电阻,有效降低二极管反向恢复电流峰值与SiC MOSFET过电压,但栅极电压检测容易受到栅极回路振荡的干扰而产生错误的开关动作。文献[17-18]通过检测SiC MOSFET漏-源极电压和漏极电流,在开关过程的电流、电压上升阶段动态切换栅极电压,实现对电压、电流过冲与振荡的有效抑制,但是电压转换模块所能提供的电平有限,调节范围较窄。文献[14]对变电流驱动方案进行优化,在传统驱动电路基础上增加了两条支路,通过注入、分流的方式实现栅极电流的调节,但该电路结构复杂,使用了很多有源器件,有待进一步优化,文献[19]提出一种基于镜像电流源的AGD电路,在开关过程的不同阶段,通过调节栅极电流实现对电压、电流过冲与振荡的抑制。文献[20]提出一种多级AGD驱动方案,设有主驱动与辅助驱动两级电路,但是该方案较为复杂,驱动电路的切换需要通过软件实现。文献[21]通过同时控制栅极电阻和栅极电流来抑制开关电流、电压过冲,为了精确检测SiC MOSFET的开关状态,采用串联电阻的方式检测漏极电流,但是该方案会额外增加损耗。

基于变栅极电阻、变栅极电压的AGD方法本质均是通过调节栅极电流实现对电压、电流过冲与振荡的有效抑制。另外,由于开关过程十分短暂,驱动电路控制信号的产生是AGD方案的难点,同时还要防止因开关信号抖动或电压、电流振荡而造成AGD电路误动作。因此,本文在对SiC MOSFET开关特性进行深入分析的基础上,提出一种基于漏极电流变化率dd/d、漏-源极电压变换率dds/d和栅极电压gs反馈的SiC MOSFET栅极电流动态调节的AGD电路。该电路具有结构简单、检测精度高、控制信号发生时间准确、可靠性高等优势。最后搭建双脉冲实验平台对所提AGD电路的电压、电流过冲与振荡的抑制效果进行了实验验证。

1 SiC MOSFET开关特性分析

图1为SiC MOSFET双脉冲测试电路等效模型[4],其中M1为理想的MOSFET模型,gd为栅漏极电容,gs为栅源极电容,ds为漏源极电容,F为寄生电容,bus为滤波电容,g_in和g_out分别为内外部栅极电阻,g、d、s、S分别为栅极、漏栅极、开尔文源极、功率源极的寄生电感,load为负载电感,VD1和VD2为二极管模型。同时在电路中引入输入电容iss、输出电容oss、反向传输电容rss的概念来表征各极电容之间的关系。各电容之间关系为iss=gs+gd、oss=gd+ds、rss=gd。开尔文源极与功率源极间寄生电感sS=s+S,栅极电阻g=g_in+g_out。此外,gs、ds、th为器件端子测得的量,th_in、gs_in、ds_in为器件内部测得的量。

图1 SiC MOSFET双脉冲测试电路等效模型

1.1 开通特性分析

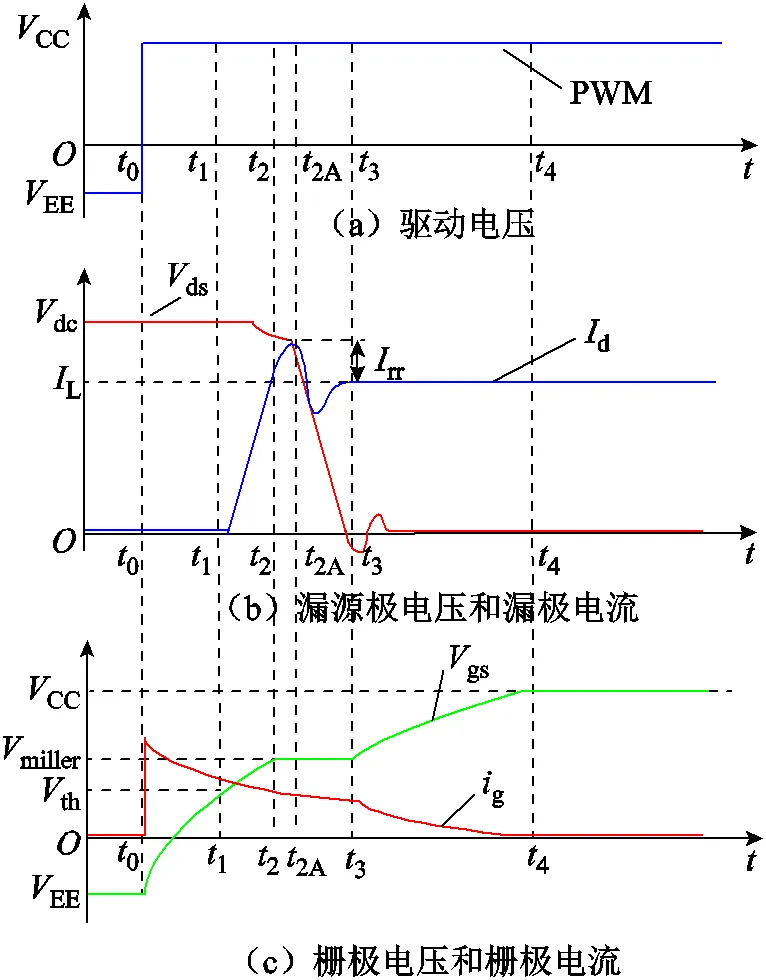

SiC MOSFET的开通特性曲线如图2所示[22],其中开通过程主要包括四个阶段。

图2 SiC MOSFET开通特性曲线

1)0~1时刻。栅极充电延时,驱动电压由负压EE跳变为正压CC,通过栅极电阻对输入电容iss进行充电,此时栅极电压gs_in小于阈值电压th_in,漏源极电压ds和漏极电流d保持不变。

2)1~2A时刻。在1时刻,栅极电压达到阈值电压,栅极电流g向输入电容iss继续充电,漏极电流d逐渐上升至负载电流L,受反并联二极管(SiC肖特基二极管,SiC SBD)结电容充电电流rr的影响,d会继续上升,在2A时刻达到尖峰电流d_peak,d_peak可表示为

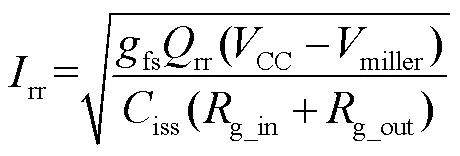

式(1)中,rr与漏极电流变化率dd/d成正相关[23],即

式中,rr为结电容充电电荷;dd/d可表示为[21]

将式(3)代入式(2),得到rr与g的关系为

由式(4)可知,rr与g成正相关,因此,减小g可以有效减小漏极电流尖峰。

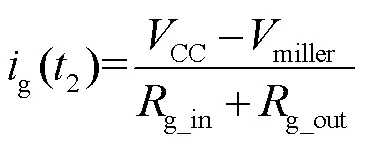

3)2A~3时刻。漏极电流d经过振荡恢复至负载电流并保持不变(d=L),栅极电压钳位于米勒平台电压miller,反并联二极管开始阻断漏源极电压,ds逐渐下降至零。2A时刻的栅极电流可表示为[24]

漏源极电压ds下降变化率可表示为

4)3~4时刻。栅极电流继续给电容gs充电至MOSFET饱和,栅极电压快速上升至给定驱动电压CC,漏源极电压下降至接近零的值,漏极电流d维持在负载电流L,SiC MOSFET完全开通。

1.2 关断特性分析

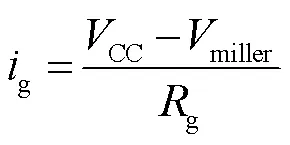

关断过程如图3所示,同理也分为四个阶段[24]。

图3 SiC MOSFET关断特性曲线

1)5~6时刻。驱动电压由正压CC跳变为负压EE,输入电容iss通过栅极电阻g开始放电,此时处于放电延时阶段,漏极电流d和漏源极电压ds保持不变,6时刻栅极电压降至米勒平台电压miller。

2)6~7时刻。漏源极电压ds逐渐上升。

3)7~8时刻。栅极电压下降至阈值电压,迅速减小的漏极电流d在电路的寄生电感上产生感应电压并与母线电压一起叠加在漏源极电压上,形成电压过冲并发生振荡,叠加后形成电压尖峰ds_peak,可表示为

式中,loop为功率回路的总寄生电感[24],可由式(8)表示;关断电流变化率dd/d可由式(9)表示[21]。

与开通过程相似,在电压上升阶段减小栅极电流g可以有效减小电压过冲量。

4)8~9时刻。栅极电压下降至负压EE,SiC MOSFET完全关断。

综上所述,在SiC MOSFET开通过程的电流d上升阶段可以通过减小栅极电流的方式来抑制d的过冲;同理在SiC MOSFET关断过程的电压ds上升阶段,减小负栅极电流的方式抑制ds的过冲。为了尽量不增加开关损耗,在开关过程的其他阶段恢复原栅极电流大小,从而减少在米勒平台内电容gd的充放电时间,提高开关速度。

2 有源驱动电路的硬件实现方案

基于上述分析,本文提出一种基于SiC MOSFET开关瞬态反馈的有源栅极电流主动调节电路,如图4所示,共分为以下四个部分。

图4 有源驱动电路原理

1)开通电流上升状态检测电路,由dd/d检测电路和开通过程栅极电压gs-on电压检测电路构成。

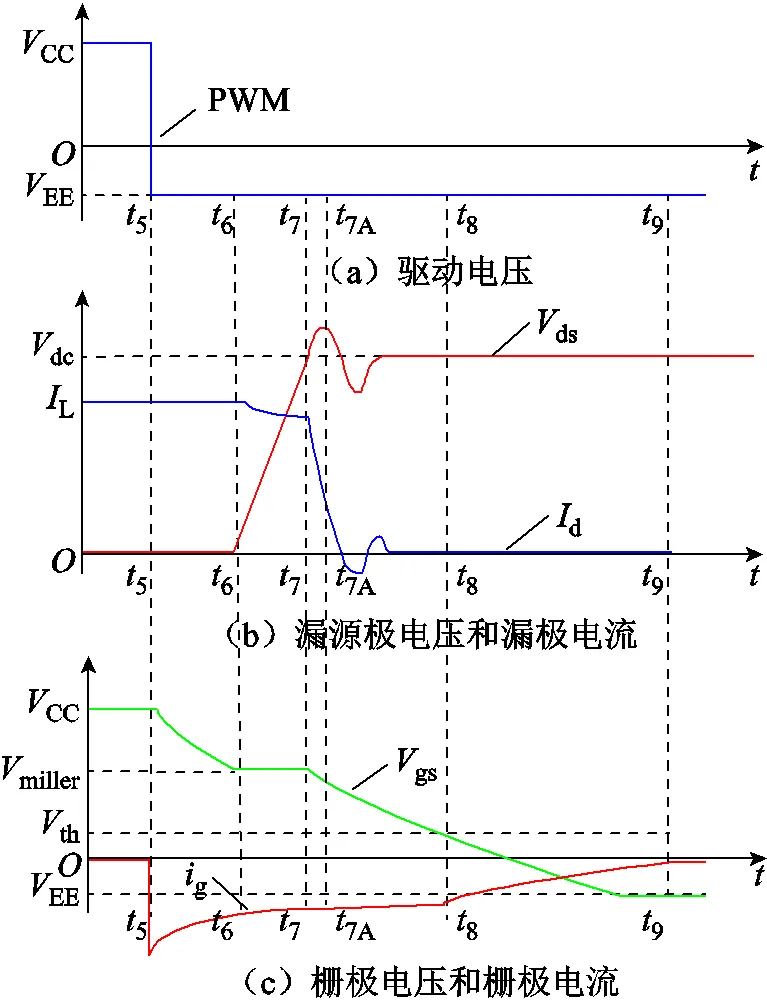

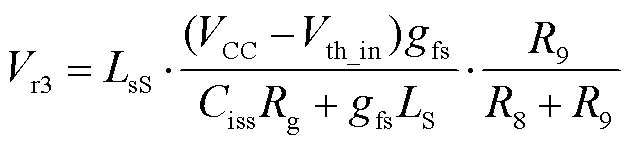

dd/d检测电路利用开尔文源极和功率源极之间的寄生电感sS因开通电流变化而产生感应电压sS的原理,将电流变化信号转变为电压信号进行检测。电路中设置二极管VD1用于排除关断过程中电流下降而产生的干扰信号。获得的感应电压与参考电压r3进行比较,得到相应的逻辑信号传输至下一级的判断电路。r3取值为

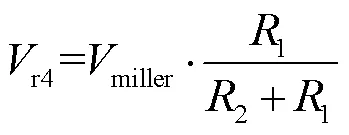

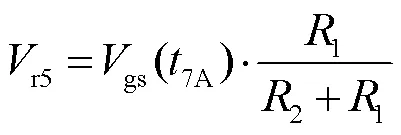

由分压电阻6、7,比较器OP1、OP2以及与门AND3构成的gs-on检测电路用于排除电流上升阶段和器件导通后电流d振荡所产生的干扰。通过检测gs是否处于[r1,r2]区间,配合dd/d检测电路所产生的逻辑输出信号,可以精确识别开通过程的电流上升阶段,其中比较电压r1和r2的取值分别为

2)关断电压上升状态检测电路,由dds/d检测电路和关断过程栅极电压gs-off检测电路两部分组成。

dds/d检测电路利用微分电路计算关断时漏源极间电压变化率的原理,将电压变化率转变为恒定电压信号,再经过比较器与设定的参考电压r6进行比较,电路中设置单向二极管用于阻断器件导通时电压下降过程产生的干扰信号。r6取值为

与开通部分同理,分压电阻1、2,比较器OP4、OP5以及与门AND2构成的gs-off检测电路用于排除器件导通后电压ds振荡所产生的干扰。通过检测gs是否处于[r4,r5]区间,配合dds/d检测电路所产生的逻辑输出信号,精确地识别关断过程的电压上升阶段,其中比较电压r4和r5的设置取值为

式中,gs(7A)为7时刻的米勒平台电压miller经过if放电时间后7A时刻的栅极电压的值;if为7A和7的时间差。

3)分流电路,包括一个推挽放大电路、MOS1管、二极管和电阻。开通电流上升状态检测电路产生的检测信号经过推挽电路放大功率后驱动MOS1管导通,经二极管和电阻分流出部分栅极输入电流。

4)注入电路,结构与分流电路相同。关断电压上升状态检测电路产生的检测信号经推挽电路驱动MOS2管导通,向栅极注入反向栅极电流,减小关断过程栅极电容的放电电流。

3 有源驱动控制过程

3.1 开通过程控制

SiC MOSFET开通时栅极电压gs、漏极电流d、漏源极电压ds以及考虑器件延时的情况下每个检测电路的信号波形如图5所示。开通过程的控制可分为四个阶段。

图5 主动控制下开通过程的特性曲线

1)外加驱动信号由负电压EE跳变为正电压CC,栅极电压gs逐渐上升。此阶段gs没有达到gs-on检测电路设定的最低值r2,逻辑与门AND3输出低电平。gs小于阈值电压th,器件两端的电流和电压没有发生变化,dd/d检测电路和dds/d检测电路均没有感应信号输出。

2)此时栅极电压满足r1>gs>r2,gs-on检测电路AND3输出高电平。同时,快速上升的漏极电流在寄生电感sS上产生感应电压,当感应电压经过分压后满足sS>r3,OP3输出高电平。逻辑与门AND1接收两路高电平信号后输出高电平,经推挽放大电路提升功率后控制MOS1管导通。经过约60ns的延时后,在ds上升的后半段分流电路被导通,栅极电流g经过电阻10流向地端,栅极电流减小为g-g1,漏极电流的变化率也随之减小,相应的开通电流过冲量减小。而此阶段的电流注入电路处于低电平状态,不产生动作。

3)漏极电流d上升阶段结束后,会出现几个周期的振荡,导致dd/d检测电路OP3再次产生高电平信号,但是由于此阶段gs>miller,因此AND3输出低电平,MOS1管及时关断,电流分流电路被阻断,栅极电流恢复至g。

4)电流变化率为零,dd/d检测电路的感应信号为低电平,控制电路不动作,MOS1管不导通,此时工作状态与上一阶段相同。

需要说明的是,开通过程的控制中需要满足id-on>delay1,其中id-on为开通的漏极电流上升时间,delay1为检测电路元器件自身延时的总和,且>1。

3.2 关断过程控制

SiC MOSFET关断时栅极电压gs、漏极电流d、漏源极电压ds以及每个检测电路的信号波形如图6所示。与开通过程相同,关断过程的控制也分为四个阶段。

图6 主动控制下关断过程的特性曲线

1)外加驱动信号由正压CC变为负压EE,栅极电压gs开始下降,此阶段gs还没降到gs-off检测电路设定的最大值r4,逻辑与门AND2输出为低电平。SiC器件处于关断延迟阶段,dd/d检测电路和dds/d检测电路均没有感应信号输出,控制电路不发生动作。

2)考虑到检测电路与控制电路的硬件延迟(实验测试延迟为40ns左右),为了避免错过最佳的栅极电流调控时机,在漏源极电压ds上升的后半段开通电流注入电路,漏极电流下降的前半段关断注入电路。此时栅极电压满足r4>gs>r5,gs-off检测电路AND2输出高电平。dds/d检测电路产生感应信号,经电阻分压后大于阈值电压r6,比较器OP6输出高电平。逻辑与门AND4接收两路高电平信号输出的高电平,经推挽放大电路后控制MOS2导通,电流注入电路被导通,向栅极端注入正向电流,此时栅极电流为-g+g2,对应的关断电压过冲量得到减小。

3)当漏源极电压ds上升结束后,ds经过几个周期的振荡后趋于稳定,dds/d检测电路在振荡过程中会再次输出高电平信号,gs经分压后小于r5,逻辑与门AND4输出低电平,MOS2管被及时关断,电流注入电路被阻断,栅极电流恢复至g。

4)漏源极电压ds和漏极电流g振荡趋于稳定值,各检测电路输出均为低电平,控制电路不发生动作,此时工作状态与上一阶段相同。

需要说明的是,关断过程的控制中需要满足vds-off>delay2,其中vds-off为关断的漏源极电压上升时间,delay2为检测电路元器件自身延时的总和,且>1。

3.3 电流尖峰抑制机理

首先对未采用有源驱动方案的电流尖峰进行分析。在开通过程的电流上升阶段,由于栅极电流g变化率较小,因此g变化在栅极和开尔文源极寄生电感上产生的压降可以忽略[23]。驱动回路的等效电路如图7a所示,其回路的基尔霍夫电压方程为

在图2中的2时刻,gs处于米勒平台,此时g的表达式为

将式(19)代入式(4),得到未采用有源驱动方案情况下的过冲电流rr为

在开通阶段采用本文提出的分流电阻法,驱动等效电路如图7b所示,将分流电阻10并入驱动电路,为了便于分析10对栅极电流的影响,构建其戴维南模型,等效输入电压eq与输出电阻eq为

在2时刻,gs=miller,g的表达式为

将式(21)与式(22)代入式(4),即可得到加入分流电路的情况下,过冲电流rr的表达式

在Vds=300V,Id=110A,Vmiller=3.8V,Rg_out=6.8Ω,Rg_in=3Ω,Ciss=12nF,Ls=2.4nH,Lloop=48nH,=85S,Qrr=1.2µC的条件下,对有源分流驱动方案的电流尖峰抑制效果进行理论证明。根据式(19)~式(23),令R10在3~30Ω范围内变化,分别绘制Vgs达到米勒平台电压时刻ig与Irr的曲线,并与无源驱动方案对比,如图8所示。

与传统无源驱动方案相比,加入分流电阻10能够有效降低g(2),从而降低过冲电流rr,并且电流尖峰抑制效果随着10增加而减小。

3.4 电压尖峰抑制机理

结合图3与图6分析本文提出的电流注入电路对关断过程电压尖峰的抑制作用。根据式(7),7A时刻电压过冲量rr处于最大值,也就是回路总电感loop上产生的感应电压,结合式(9)满足关系

因此,减小t7A时刻栅极电流ig能够降低Vds的尖峰。关断过程的无源驱动电路如图9a所示。

由于gs(7A)近似为米勒平台电压,因此在加入电流注入电路情况下栅极电流为

采用电流注入法,驱动电路如图9b所示,构建其戴维南等效电路模型,等效输入电压eq与输出电阻eq为

引入电流注入电路后,g(7A)为

将式(26)与式(27)代入式(24),得到加入有源电流注入电路的电压过冲表达式。在不造成误开通的前提下,令R5在20~60Ω范围内变化,绘制与图8相同条件下的栅极电流与过冲电压曲线,如图10所示。可以看出在注入电路开通的情况下,可明显降低ig(t7A),从而有效减小过冲电压Vrr,且电压过冲的抑制作用随着R5的增加而减小。

4 实验结果与分析

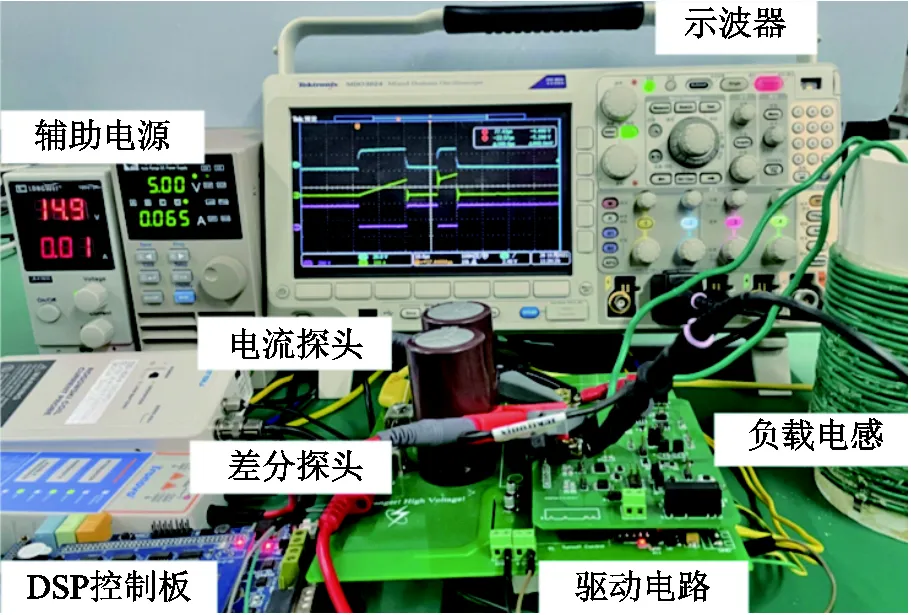

为了验证本文设计的有源驱动电路的有效性,搭建了如图11所示的双脉冲测试实验平台。其中,SiC MOSFET模块型号为CAS300M12BM2,示波器为Tektronix MDO3024,采用DSP28335控制板产生双脉冲信号,差分探头为Tronovo—HPD0100A,电流探头为IWATSU—SS684,负载电感值为48.5μH,模块的部分参数见表1,实验样机中器件型号参数见表2。

表1 CAS300M12B2M模块的部分参数

Tab.1 Part parameters of the CAS300M12B2M module

表2 实验样机中器件型号

Tab.2 Components in the experimental prototype

图11 双脉冲测试实验平台

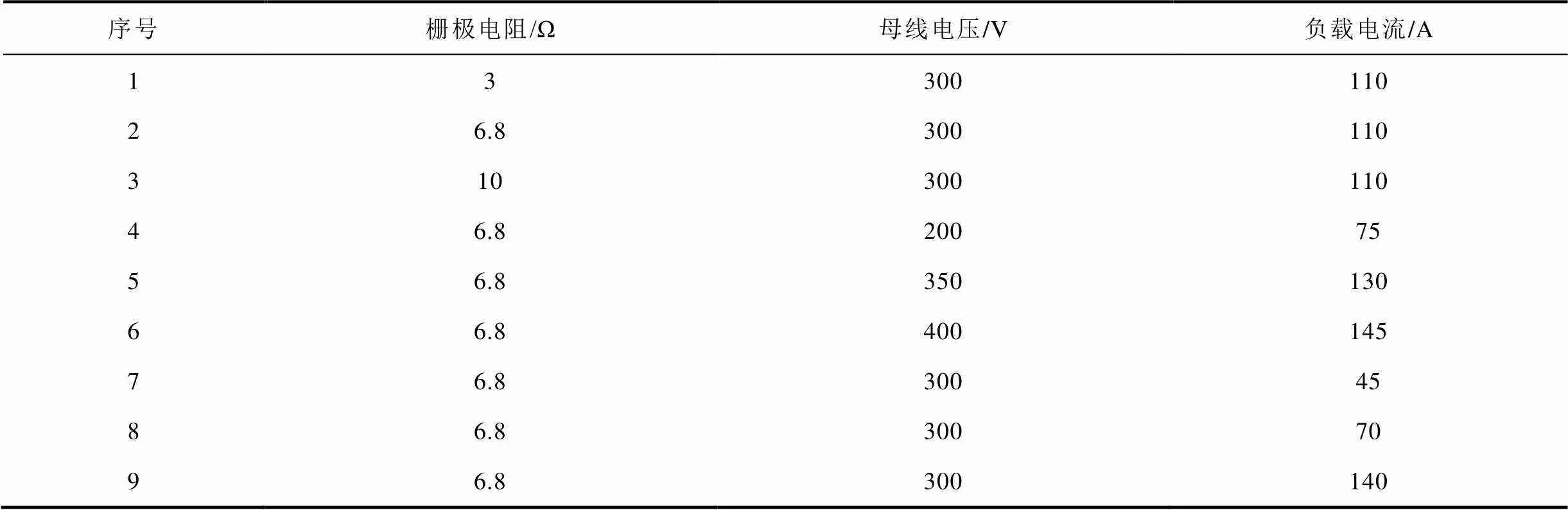

本文共设定了九种实验工况见表3,分别在不同栅极电阻、不同直流母线电压和不同负载电流工况下,对所提出的新型有源驱动电路(AGD)与传统驱动电路(CGD)开关过程中的电流、电压过冲及振荡进行比较,各工况的开通和关断波形依次如图12~图14所示。图15给出了各工况下SiC MOSFET模块的开通与关断损耗结果,并在同等电流电压过冲抑制效果下,对比AGD与CGD的开关损耗[17]。

表3 九种实验工况设置

Tab.3 Nine experimental conditions

4.1 不同栅极电阻效果分析

为了验证设计的有源驱动方案在不同栅极电阻下的控制效果,设置实验工况为1~3,即直流端母线电压300V,负载电流110A,栅极电阻取值分别为3Ω、6.8Ω和10Ω,对比实验结果如图12所示。

由图12可知,同等直流电压和负载电流的条件下,取不同阻值的栅极电阻,AGD对开关过冲抑制效果明显。其中,栅极电阻取3Ω时,开通电流峰值由187A下降到151A,电流过冲量降低了36A,减小了46.7%。而关断电压峰值由374V下降到354V,过冲量降低了20V,减小了27.1%。当栅极电阻取6.8Ω和10Ω时,开通电流过冲量分别降低了27A和24A,减小了44.3%和53.3%。关断电压过冲量分别降低了28V和24V,减小了53.8%和52.1%。同时,AGD的电流和电压可以快速进入稳定状态,波形振荡幅度更小,振荡时间更短。

图12 不同栅极电阻下开通与关断波形

图13 不同母线电压开通和关断波形

图14 不同负载电流开通和关断波形

图15 CGD与AGD在不同工况的开关损耗对比

图15a为不同栅极电阻条件下CGD与AGD的开关损耗对比,结合图12可以看出,栅极电阻为3Ω时AGD的电流电压抑制效果需要CGD的电阻增加到10Ω才能实现,但此时开关速度明显降低,同时开关损耗增加40%,而使用AGD的开关损耗只增加13.9%。此外,同等栅极电阻条件下,AGD相比CGD的开关损耗平均只增加了22.1%,但电流和电压的过冲值平均降低了48.1%和44.3%。

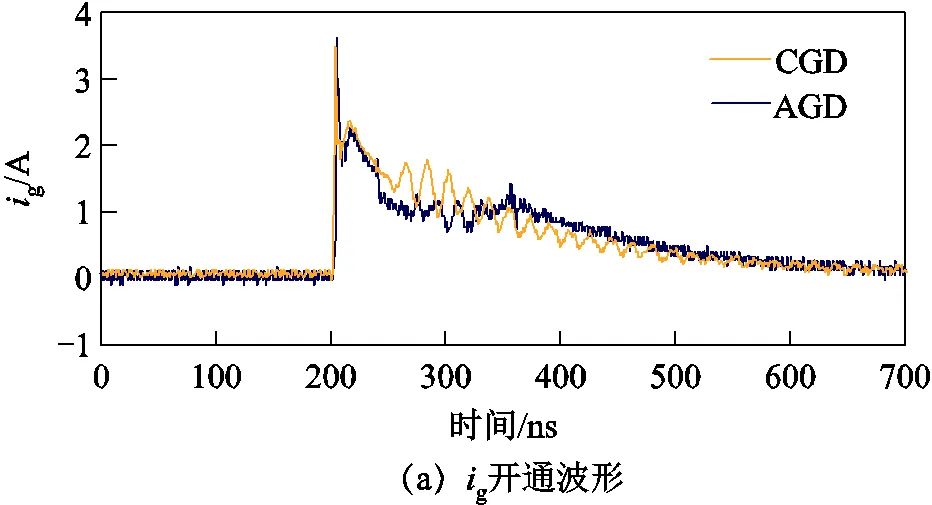

图16分别给出了栅极电阻g=6.8Ω,L=110A,dc=300V工况下CGD与AGD的栅极电流实验波形。可以看出,在电流上升阶段与电压下降阶段,本文提出的AGD方案能够有效降低栅极电流,而在其他过程AGD与CGD的电流曲线保持一致。说明本文所提基于dd/d、dds/d和gs反馈的SiC MOSFET栅极电流动态调节电路的控制信号发生时间精确,具有良好的实时性和有效性。

4.2 不同母线电压效果分析

为了验证本文有源驱动方案在不同母线电压下都具有良好的效果,本文分别设置母线电压为200V、300V、350V、400V,对应的负载电流为74A、110A、129A、147A,栅极电阻均为6.8Ω,开通和关断波形如图12c、图12d和图13所示。

从图12c、图12d和图13中可知,四种母线电压下,AGD相较于CGD在开通时电流过冲量分别减小了19A、26A、26A、25A,平均降低了40.4%。关断时电压过冲量分别减小了18V、18V、28V、32V,平均降低了45.9%。同时,AGD对电流电压的高频振荡也具有显著的抑制效果。

图15b是不同母线电压下的开关损耗对比,可知AGD有效减小了电流电压过冲与振荡,而器件的开关损耗平均只增加了29.4%,并且随着母线电压的上升,开关损耗增加率也逐渐减小。

4.3 不同负载电流效果分析

为了验证本文提出的有源驱动方案在不同的负载电流条件下均具有效性,通过改变首个脉冲时间以获得45A、70A、110A、140A四种不同负载电流,此时栅极电阻为6.8Ω,母线电压为300V,对比实验结果如图14、图12c和图12d所示。

由图14、图12c和图12d可知,在相同栅极电阻和母线电压条件下,AGD的开通电流过冲、关断电压过冲、振荡幅值和振荡时间都明显小于CGD。其中,AGD的开通电流过冲量比CGD分别减小了15A、20A、27A、26A,平均降低了39.1%。同样,关断电压过冲量分别减小了12V、24V、28V、32V,平均降低了48.9%。而AGD的开关损耗平均只增加了30.9%,开关损耗对比如图15c所示。

4.4 EMI对比分析

通过降低开关过程中的电流电压过冲量能够从源头上减小SiC MOSFET高频电磁干扰的发射。图17和图18给出了dc=300V,L=110A,g=6.8Ω工况下,CGD和AGD的开通电流与关断电压波形的频谱分析对比结果。

图17 AGD和CGD的Id频谱对比

图18 AGD和CGD的Vds频谱对比

从频谱图17和图18可知,CGD的开关电流电压振荡均在7.3MHz附近产生尖峰,尖峰出现的位置与振荡频率基本一致,而使用AGD的尖峰幅值明显降低,验证了本文提出的有源驱动电路能够有效降低SiC MOSFET开关过程的电磁干扰。

5 结论

不同工况下的实验结果证明了本文所提基于开关瞬态反馈的SiC MOSFET栅极电流主动调节电路能够有效抑制开通关断过程电流电压过冲、振荡与电磁干扰,并得到以下结论:

1)在SiC MOSFET开通过程的电流上升阶段减小栅极电流,在关断过程的电压上升阶段注入反向栅极电流,能够有效降低电流电压的过冲与振荡。

2)提出的SiC MOSFET漏极电流变化率dd/d、漏-源极电压变化率dds/d以及栅极电压gs的检测电路可以精确识别开关过程的电流上升阶段与电压上升阶段,同时能够有效防止由驱动信号抖动以及电流电压振荡产生的误动作。

3)本文提出的AGD方案结构简单、通用性强,可根据开关速度、开关损耗、电流与电压过冲等工况需求改变电流分流电路与电流注入电路中的电阻以及比较电路的各阈值电压。

[1] Zhao Shuang, Zhao Xingchen, Dearien A, et al. An intelligent versatile model-based trajectory-optimized active gate driver for silicon carbide devices[J]. IEEE Journal of Emerging and Selected Topics in Power Electronics, 2020, 8(1): 429-441.

[2] 张建忠, 吴海富, 张雅倩, 等. 一种SiC MOSFET谐振门极驱动电路[J]. 电工技术学报, 2020, 35(16): 3453-3459.

Zhang Jianzhong, Wu Haifu, Zhang Yaqian, et al. A resonant gate driver for SiC MOSFET[J]. Transactions of China Electrotechnical Society, 2020, 35(16): 3453-3459.

[3] 余宝伟, 郭希铮, 部旭聪, 等. 全碳化硅辅助变流器功率回路振荡问题[J]. 电工技术学报, 2021, 36(增刊2): 619-626.

Yu Baowei, Guo Xizheng, Bu Xucong, et al. Oscillation of power circuit of full SiC auxiliary converter[J]. Transactions of China Electrotechnical Society, 2021, 36(S2): 619-626.

[4] 冯超, 李虹, 蒋艳锋, 等. 抑制瞬态电压电流尖峰和振荡的电流注入型SiC MOSFET有源驱动方法研究[J]. 中国电机工程学报, 2019, 39(19): 5666-5673, 5894.

Feng Chao, Li Hong, Jiang Yanfeng, et al. Research on current injection active drive method of SiC MOSFET with transient voltage and current spike and oscillation suppression[J]. Proceedings of the CSEE, 2019, 39(19): 5666-5673, 5894.

[5] Zhao Shuang, Dearien A, Wu Yuheng, et al. Adaptive multi-level active gate drivers for SiC power devices[J]. IEEE Transactions on Power Electronics, 2020, 35(2): 1882-1898.

[6] Chen Hao, Divan D. High speed switching issues of high power rated silicon-carbide devices and the mitigation methods[C]//2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 2015: 2254-2260.

[7] Nayak P, Hatua K. Active gate driving technique for a 1200 V SiC MOSFET to minimize detrimental effects of parasitic inductance in the converter layout[J]. IEEE Transactions on Industry Applications, 2018, 54(2): 1622-1633.

[8] 王宁, 张建忠. 基于开关轨迹优化的SiC MOSFET有源驱动电路研究综述[J]. 电工技术学报, 2022, 37(10): 2523-2537.

Wang Ning, Zhang Jianzhong. Review of active gate driver for SiC MOSFET with switching trajectory optimization[J]. Transactions of China Electrotechnical Society, 2022, 37(10): 2523-2537.

[9] 邵天骢, 郑琼林, 李志君, 等. 基于干扰动态响应机理的SiC MOSFET驱动设计[J]. 电工技术学报, 2021, 36(20): 4204-4214.

Shao Tiancong, Zheng Trillion Q, Li Zhijun, et al. SiC MOSFET gate driver design based on interference dynamic response mechanism[J]. Transactions of China Electrotechnical Society, 2021, 36(20): 4204-4214.

[10] 李辉, 廖兴林, 肖洪伟, 等. 基于SiC MOSFET直流固态断路器关断初期电压尖峰抑制方法[J]. 电工技术学报, 2018, 33(5): 1058-1067.

Li Hui, Liao Xinglin, Xiao Hongwei, et al. Voltage overshoot suppression method of SiC MOSFET-based DC solid-state circuit breaker at turn-off initial stage[J]. Transactions of China Electrotechnical Society, 2018, 33(5): 1058-1067.

[11] Liang Mei, Li Yan, Chen Qian, et al. Research on an improved DC-side snubber for suppressing the turn-off overvoltage and oscillation in high speed SiC MOSFET application[C]//2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 2017: 1358-1365.

[12] Regnat G, Jeannin P O, Frey D, et al. Optimized power modules for silicon carbide mosfet[J]. IEEE Transactions on Industry Applications, 2018, 54(2): 1634-1644.

[13] 柯俊吉, 赵志斌, 谢宗奎, 等. 考虑寄生参数影响的碳化硅MOSFET开关暂态分析模型[J]. 电工技术学报, 2018, 33(8): 1762-1774.

Ke Junji, Zhao Zhibin, Xie Zongkui, et al. Analytical switching transient model for silicon carbide MOSFET under the influence of parasitic parameters[J]. Transactions of China Electrotechnical Society, 2018, 33(8): 1762-1774.

[14] 刘平, 李海鹏, 苗轶如, 等. 基于驱动电流动态调节的低过冲低损耗SiC MOSFET有源门极驱动[J]. 中国电机工程学报, 2020, 40(18): 5730-5741.

Liu Ping, Li Haipeng, Miao Yiru, et al. Low overshoot and low loss active gate driver for SiC MOSFET based on driving current dynamic regulation[J]. Proceedings of the CSEE, 2020, 40(18): 5730-5741.

[15] Camacho A P, Sala V, Ghorbani H, et al. A novel active gate driver for improving SiC MOSFET switching trajectory[J]. IEEE Transactions on Industrial Electronics, 2017, 64(11): 9032-9042.

[16] Yamaguchi K, Katsura K, Yamada T, et al. Comprehensive evaluation of gate boost driver for SiC-MOSFETs[C]//2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 2016: 1-8.

[17] Yang Yuan, Wen Yang, Gao Yong. A novel active gate driver for improving switching performance of high-power SiC MOSFET modules[J]. IEEE Transactions on Power Electronics, 2019, 34(8): 7775-7787.

[18] Wen Yang, Yang Yuan, Gao Yong. Active gate driver for improving current sharing performance of paralleled high-power SiC MOSFET modules[J]. IEEE Transactions on Power Electronics, 2021, 36(2): 1491-1505.

[19] Sukhatme Y, Miryala V K, Ganesan P, et al. Digitally controlled gate current source-based active gate driver for silicon carbide MOSFETs[J]. IEEE Transactions on Industrial Electronics, 2020, 67(12): 10121-10133.

[20] Dymond H C P, Liu Dawei, Wang Jianjing, et al. Multi-level active gate driver for SiC MOSFETs[C]// 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 2017: 5107-5112.

[21] Vamshi K M, Hatua K. Current controlled active gate driver for 1200V SiC MOSFET[C]//2016 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Trivandrum, India, 2016: 1-6.

[22] 王莉娜, 马浩博, 袁恺, 等. SiC MOSFET半桥电路开关瞬态过电流、过电压建模与影响因素分析[J]. 电工技术学报, 2020, 35(17): 3652-3665.

Wang Lina, Ma Haobo, Yuan Kai, et al. Modeling and influencing factor analysis of SiC MOSFET half-bridge circuit switching transient overcurrent and overvoltage[J]. Transactions of China Electrotechnical Society, 2020, 35(17): 3652-3665.

[23] 王旭东, 朱义诚, 赵争鸣, 等. 驱动回路参数对碳化硅MOSFET开关瞬态过程的影响[J]. 电工技术学报, 2017, 32(13): 23-30.

Wang Xudong, Zhu Yicheng, Zhao Zhengming, et al. Impact of gate-loop parameters on the switching behavior of SiC MOSFETs[J]. Transactions of China Electrotechnical Society, 2017, 32(13): 23-30.

[24] 朱义诚, 赵争鸣, 王旭东, 等. SiC MOSFET与SiC SBD换流单元瞬态模型[J]. 电工技术学报, 2017, 32(12): 58-69.

Zhu Yicheng, Zhao Zhengming, Wang Xudong, et al. Analytical transient model of commutation units with SiC MOSFET and SiC SBD pair[J]. Transactions of China Electrotechnical Society, 2017, 32(12): 58-69.

Active Gate Driver for SiC MOSFET Based on Switching Transient Feedback

Liu Ping Chen Zijian Miao Yiru Yang Jiangtao Li Wei

(College of Electrical and Information Engineering Hunan University Changsha 410006 China)

Due to the influence of internal parasitic parameters and junction capacitance, silicon carbide (SiC) power devices have great voltage and current overshoot and high-frequency switching oscillation in the process of high-speed switching, which seriously affects the operation reliability of SiC-based converters. In this paper, firstly, switching characteristics of SiC MOSFET are deeply analyzed to reveal the mathematical relationship between gate driving current and voltage and current overshoot. Then, a new active gate drive circuit with variable driving current is proposed. The gate current is actively regulated in the current or voltage rising stage of the switching process to suppress voltage and current overshoot and oscillation through the direct detection and feedback of the transient drain current change rate dd/d, drain-source voltage change rate dds/dand driving voltage of SiC MOSFETgs. Finally, experimental results show that the proposed method can effectively reduce voltage and current overshoot by 30%~50%, suppress the oscillation and electromagnetic interference, and improve the operation reliability of SiC MOSFET converter.

SiC MOSFET, active gate drive, gate current, current overshoot, voltage overshoot

10.19595/j.cnki.1000-6753.tces.211068

TM46

江苏省输配电装备技术重点实验室开放资金(2021JSSPD11)和湖南省自然科学基金(2021JJ30116)资助项目。

2021-07-14

2022-01-14

刘 平 男,1983年生,副教授,研究方向为电动车辆高性能电力电子变换与电机驱动控制。E-mail:pingliu@hnu.edu.cn

苗轶如 男,1988年生,博士后,研究方向为电力电机变换器拓扑结构与控制技术。E-mail:miaoyiru@cqu.edu.cn(通信作者)

(编辑 李冰)