并网VSC的大扰动失稳模式

2022-08-09邢光正徐式蕴王金浩郑惠萍

邢光正,闵 勇,陈 磊,汤 涌,徐式蕴,王金浩,郑惠萍

(1. 清华大学电机系电力系统及发电设备安全控制和仿真国家重点实验室,北京 100084;2. 中国电力科学研究院有限公司,北京 100192;3. 国网山西省电力公司电力科学研究院,山西太原 030001)

0 引言

随着系统中各类新能源发电设备所占比例的不断提高,以同步机为主导的传统电力系统将逐渐演变为以电力电子设备为主导的新型电力系统[1],其中电压源变换器VSC(Voltage Source Converter)是使用最广泛的电力电子接口设备。

不同于发电机等电磁变换设备,采用电力电子接口的新能源发电设备在动态特性上存在显著差异[2]。同步发电机的动态特性主要由转子运动方程等物理过程主导,而电力电子设备由于其高度可控性,动态特性主要由控制过程主导,大规模接入后导致系统的稳定机理发生巨大变化。同时,电力电子设备中不同时间尺度的控制环节相互级联、相互耦合,并存在大量切换控制[3],使得电力电子设备产生多时间尺度的复杂动态行为[4⁃5],进而导致系统中出现不同的稳定问题和失稳模式。小扰动稳定方面,宽频带振荡是由电力电子设备引发的一种新的稳定问题,近年来得到了大量关注和研究[6⁃9]。

大扰动稳定问题也开始逐渐引起重视,失稳模式的研究是其中一个基础性工作。根据Lyapunov稳定性的定义,一个动态系统不能收敛到稳定平衡点SEP(Stable Equilibrium Point)就是失稳,但实际研究中,往往根据失稳的不同主导动态和不同机理,分成不同的失稳模式,例如传统系统中的功角失稳模式、电压失稳模式[10]。电力电子设备并网系统中已经发现了一些新的失稳模式,例如锁相环PLL(Phase Locked Loop)引发的失去同步问题[11⁃12](又叫广义同步稳定性[13])。同步稳定问题已经得到较充分的研究,其主要关注低电压穿越期间,VSC 外环控制退出,切换为定电流控制时的大扰动稳定问题[14⁃15]。文献[16]说明了外环控制投入时,考虑外环和PLL的模型也存在多摆失稳的现象。文献[17]研究了考虑脉宽调制(PWM)饱和情况下带恒阻抗直流负载的三相整流器存在的灾难性分岔现象及引发的大扰动稳定问题。但目前仍然缺乏对大扰动失稳模式系统性的研究。

传统电力系统中,转子运动方程是主导的动态过程,因此功角失稳是系统最主要的大扰动失稳模式,并由此衍生出等面积法则等方法用来解释稳定机理。电力电子设备的动态特性由控制过程主导,因此大扰动稳定过程主要受各个控制环节影响,有必要从不同控制环节对系统的大扰动失稳模式进行研究。PLL 引发的失去同步问题,就是一种和PLL环节强相关的失稳模式。除了PLL,VSC 中还有其他不同的控制环节,各环节是否会发生失稳、失稳时有何表现,是大扰动稳定研究的重要基础。

正如单机无穷大系统是研究功角稳定的最简系统,单VSC 接入无穷大系统也是研究VSC 并网系统失稳模式的最简系统。本文针对该系统,考虑VSC正常状态和故障状态下的不同控制模式,分别从PLL、外环、内环3个不同控制环节的角度,研究系统中可能存在的大扰动失稳模式。首先提出了控制环节失稳的定义和判据,然后说明了该系统中PLL、外环和内环均可能产生失稳,失稳形态既有单调失稳,又有振荡失稳,对应的稳定边界既有不稳定平衡点UEP(Unstable Equilibrium Point)的稳定流形,又有不稳定极限环。

1 系统模型

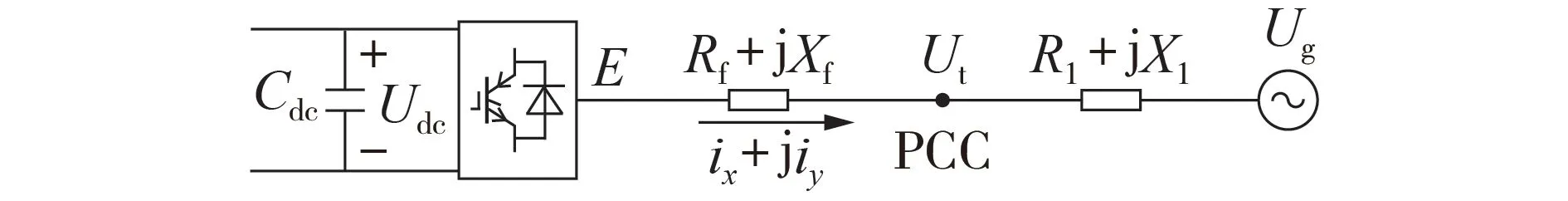

本文采用VSC 接入无穷大母线VSC-IB(VSC connected to Infinite Bus)系统,线路图如图1 所示。图中:E为VSC 的内电势;Ut为公共连接点PCC(Point of Common Coupling)处的电压;Udc为直流电容Cdc两端电压;Ug为无穷大系统等效电压;Rf+jXf为滤波器阻抗;Rl+jXl为线路阻抗;ix+jiy为同步旋转xy坐标系下的线路电流。

图1 VSC-IB系统电路图Fig.1 Circuit diagram of VSC-IB system

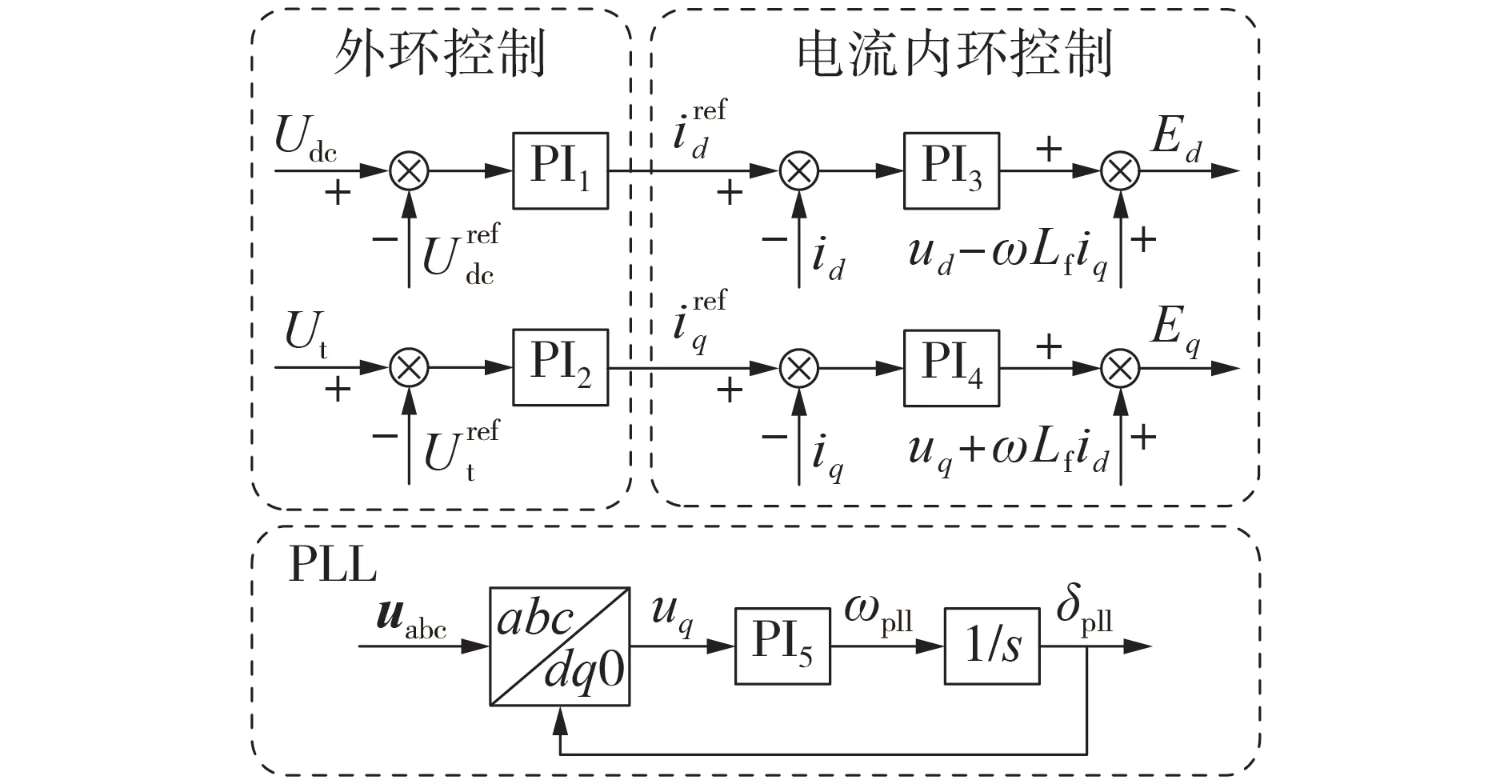

采用矢量控制的VSC 含有内、外2 层控制环节。外环用来产生dq轴电流指令值作为内环的输入,本文中外环分别采用直流电压控制DVC(Direct Voltage Control)和交流电压控制AVC(Alternative Voltage Control),也是目前一种典型的控制策略。当d轴电流指令值采用直流电压控制时,需要考虑直流电容的功率平衡。内环控制通过PWM 策略调整内电势,使得输出电流跟踪电流指令值。PLL 的作用是锁定PCC处电压相角。当系统发生短路故障时,VSC 通常会切换进入低电压穿越模式,此时外环控制退出,系统转为电流内环控制,即直接给定dq轴电流指令值。系统完整的控制结构如图2所示。图中:PI1—PI5为比例积分(PI)控制器为PCC 处电压指令值;为直流侧电压指令值;δpll和ωpll分别为PLL 的相角和角频率;Ed和Eq分别为VSC内电势E的d、q轴分量;ud、uq分别为Ut的d、q轴分量;id、iq分别为注入PCC 电流的d、q轴分量;ω为dq坐标系下的角频率,即ω=ω0+ωpll,ω0为系统标称角频率;Lf为滤波器电感。各控制环节的动态方程如下。

图2 包含直流电压控制和交流电压控制外环的VSC控制结构图Fig.2 Control structure diagram of VSC including DVC and AVC outer loops

1.1 外环控制

根据图2,d轴采用直流电压控制,q轴采用交流电压控制。外环包含x1、x3和Udc这3个状态量,外环控制方程如下:

式中:kp1、ki1和kp3、ki3分别为PI1控制器和PI3控制器的比例、积分参数;x1、x3分别为PI1、PI3控制器积分环节的状态量;P、Pref分别为并网有功功率及其参考值。

1.2 PLL环节

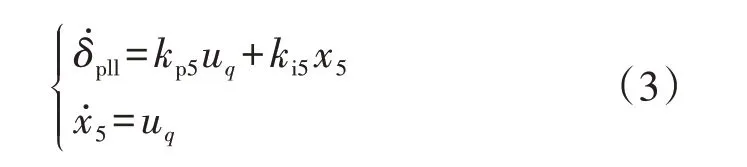

PLL 环节采用基于单同步旋转坐标变换的PLL结构,控制结构图如图2所示。PLL环节的控制方程如下:

式中:x5为PI5控制器积分环节的状态量;kp5、ki5分别为PI5控制器的比例、积分参数。

1.3 电流内环控制

电流内环控制方程如下:

1.4 线路动态

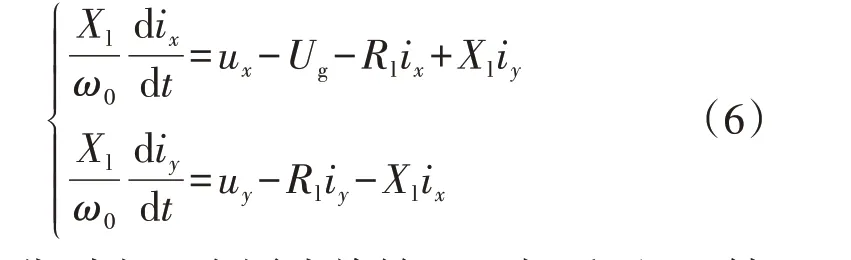

线路部分的动态方程为:

式中:ux、uy分别为Ut在同步旋转xy坐标系下x、y轴的分量。

2 VSC控制环节失稳的定义和判据

由第1 节分析可以看到,除了直流侧电容的电压动态、线路动态,上述VSC-IB 系统的其他动态都是由控制过程主导的,而且直流电压动态也和直流电压控制过程紧密耦合成一个整体。故大扰动失稳模式主要和控制环节有关,不同的失稳模式可能由不同的控制环节主导。为了能够全面地分析系统中可能存在的大扰动失稳模式,首先需要明确各控制环节失稳的定义和判据。

1)控制环节失稳定义为无法实现其控制目标。

由VSC-IB 系统的模型可知,不同的控制环节需实现不同的控制目标:外环控制的目标是直流电压、交流电压等于指令值;内环控制的目标是dq轴电流等于指令值;PLL 的控制目标是相角锁定机端电压相角。因此,如果某个控制环节无法实现其控制目标,则本文定义该环节失稳。

更加具体地,图2 中各个控制环节都包含PI 控制,实现控制目标对应于PI 环节的输入为0,因此,以有功/d轴控制为例,可将Udc--id、uq是否收敛到0分别作为外环、内环、PLL是否失稳的判据。

2)多控制环节失稳时主导环节的确定。

仿真结果可能显示多个环节都无法实现控制目标,此时需要进一步分析,确定导致系统失稳的主导环节和原因。

VSC 的控制是一种典型的分层控制,上层控制依赖于下层控制目标的实现。例如:当PLL 失去同步时,电流环仍然可以很好地跟踪dq轴电流的指令值,此时认为PLL环节发生失稳;而当电流环无法跟踪指令值时,PLL 不可能实现控制目标,可以说明PLL 环节是电流环的上层。因此,如果上下层控制都同时出现失稳,则失稳的根本原因还是下层控制失稳。还有另外一种情形,上层控制失稳持续偏离目标值,下层控制初始阶段能够稳定,但最后也出现失稳,这种情形则是上层控制失稳。其原因如下:一是从时间角度,上层控制先表现出失稳;二是从逻辑角度,下层控制失稳的原因是上层控制失稳后给出的下层目标值不合理。针对本文采用的控制结构,从上至下依次为电压外环、PLL和电流环。

3)大扰动失稳模式和非线性环节相关。

大扰动稳定是非线性系统的特殊现象。对于一个线性系统,只存在小扰动稳定问题,不存在大扰动稳定问题,如果平衡点是小扰动稳定/不稳定的,则系统就是全局稳定/不稳定的。因此,大扰动稳定问题是非线性所导致的。非线性可能导致系统失去平衡点或出现非全局的稳定域,都会导致相应的大扰动失稳[18]。因此,分析大扰动失稳模式时需要厘清相关的非线性环节。

3 大扰动失稳模式

本节基于上文的VSC 并网系统模型,考虑外环控制退出和投入2 种不同的情况,针对不同环节,分别研究系统中的大扰动失稳模式。需要强调的是,本文的目的是全面分析VSC 并网系统中“可能存在的”大扰动失稳模式,而并不关注该失稳模式在实际系统中发生的风险,因此,采用的故障扰动或者给定的初始状态点和实际可能存在一定偏差,其目的是发现所有“可能存在的”失稳模式。实际系统中,不同失稳模式发生的风险,将是后续研究的内容。

3.1 PLL失去同步

本节研究外环控制退出、采用电流控制的情形,对应VSC的低电压穿越模式。

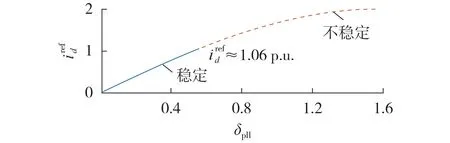

3.1.1 平衡点存在性分析与失去平衡点失稳

SEP 和UEP 是状态空间中非常重要的点。在仅包含同步机的传统电力系统中,稳定边界主要由UEP 的稳定流形组成。因此,首先分析系统中SEP和UEP的分布情况。

系统参数如附录A 表A1 所示,随着i的改变,系统对应的平衡点及小扰动稳定性也不同。在第2节中系统方程的基础上,令导数为0 可得式(7),进而解出系统平衡点。

图3 δpll随irefd 变化的分岔图Fig.3 Bifurcation diagram of δpll changing with irefd

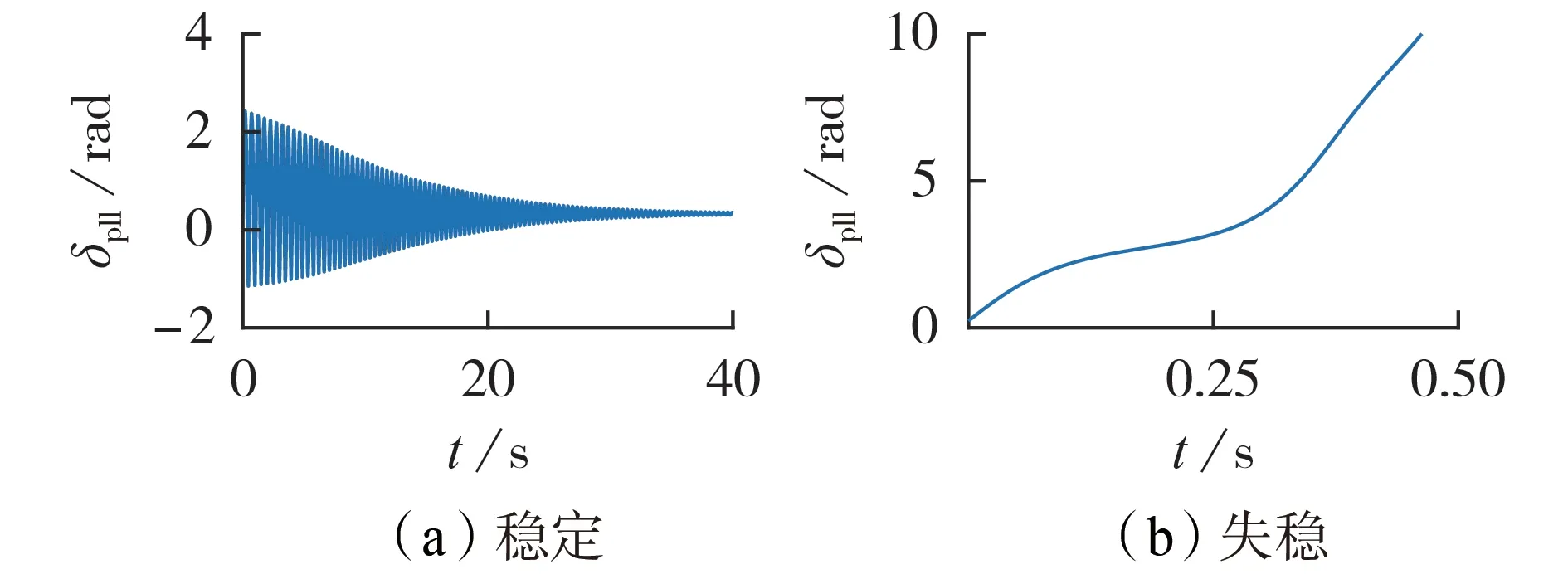

3.1.2 振荡失稳

为了进一步说明失稳形态,观察δpll在稳定和失稳2 种情况下的表现,如图4 所示。由图4(b)可以看出,此时δpll振荡发散。

图4 =0.8 p.u.时δpll时域仿真结果Fig.4 Time domain simulative results of δpll when =0.8 p.u.

3.1.3 单调失稳

为了进一步说明失稳形态,观察δpll在稳定和失稳2 种情况下的表现,如图5 所示。由图5(b)可以看出,此时δpll单调失稳。

图5 0.3 p.u.时δpll时域仿真结果Fig.5 Time domain simulative results of δpll when 0.3 p.u.

3.1.4 基于降阶模型的分析

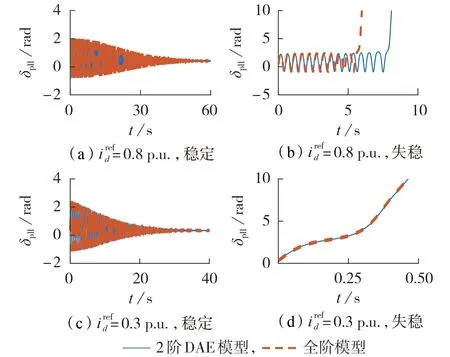

本节通过对比降阶微分代数方程(DAE)模型和全阶模型的仿真结果,以进一步说明此失稳模式和PLL环节相关。

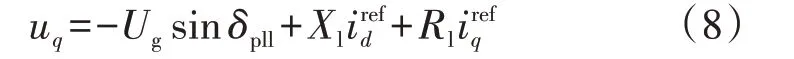

对多时间尺度系统,认为PLL 的时间尺度远大于电流环及线路动态,可以对原系统进行降阶,忽略电流环动态和传输线动态,可以得到2阶DAE模型,其中状态变量只包含δpll和x5。此时系统的微分方程可简化为式(3),其中:

因为降阶后电流内环退化为代数方程,实际上id-和iq-始终为0。此时使用3.1.2、3.1.3 节中同样的参数和初值,对比振荡失稳和单调失稳情况下2 阶DAE 模型和全阶模型δpll的时域仿真结果,如图6 所示。在仅含有PLL 的动态时,DAE 模型的失稳模式和全阶系统基本一致,进一步说明该失稳模式和PLL相关。

图6 2种失稳模式下DAE模型和全阶模型δpll时域仿真结果Fig.6 Time domain simulative results of δpll of DAE model and full-order model under two instability patterns

3.1.5 稳定边界

针对外环控制退出的系统,采用2阶DAE 模型,可通过相平面对2 阶非线性动力系统的边界进行描述。分别将外环失稳对应的2 种工况下系统稳定和失稳情形的轨迹与稳定边界的关系绘制出来,如图7(a)、(b)所示。

图7(a)对应3.1.2 节中的振荡失稳,图中实线和虚线分别代表系统稳定和失稳状态下的轨迹。图中的阴影部分区域代表系统的稳定域。可以看出:稳定状态下,系统初始点位于稳定边界内,故仍然可以回到平衡点;失稳状态下,系统初始点位于稳定边界外,系统轨迹振荡发散。系统稳定边界和UEP 无关,由不稳定极限环构成。图7(b)对应3.1.3节中的单调失稳,此时系统稳定边界接触到UEP。说明此时系统的稳定边界为UEP的稳定流形。

图7 DAE模型根轨迹与稳定边界的关系Fig.7 Relationship between DAE model trajectory and stability boundary

3.1.6 小结

对于外环退出的VSC 控制模式,在存在SEP 的前提下,系统存在2 种失稳模式,主要和系统的运行工况相关,当irefd较大,接近小扰动稳定临界值时,系统的稳定域较小,稳定边界由不稳定极限环构成,当状态量值位于稳定域外时,系统发生振荡失稳;而当逐渐减小,远离小扰动稳定临界值时,系统的稳定域逐渐增大,直到稳定边界接触UEP 的稳定流形,此时系统单调失稳。

通过降阶模型的时域仿真,可以说明这2 种失稳模式都和PLL 环节相关,失稳机理均是PLL 环节无法实现锁相,对应了式(8)中PLL环节的非线性。

3.2 外环失稳

3.2.1 平衡点存在性分析与失去平衡点失稳

投入外环的情况下,VSC-IB 系统参数如附录B表B1 所示。根据平衡点处状态变量的导数为0,求解非线性代数方程,可以解出系统平衡点。

此时系统同样存在系统失去平衡点的可能。使用表B1 中的参数,Pref=0.7 p.u.时,系统发生断线故障,t=0.2 s 时Xl从0.8 p.u.增大至1.6 p.u.,时域仿真结果如附录B图B1所示,直流电压外环发生失稳。

对包含外环控制的全阶模型,分别画出系统的小扰动稳定性随有功功率参考值的变化曲线,如附录B图B2所示。可以看出:当有功功率参考值Pref大于传输线的功率极限时,系统不存在平衡点;当Pref小于功率极限时,可以解出2个平衡点,平衡点处δpll值分别对应曲线的左半部分和右半部分,蓝色实线表示SEP,红色虚线表示UEP。左侧分支存在1 个临界有功功率Pcri,对应于系统中存在的Hopf分岔。如果参考功率超过Pcri,则1对共轭的特征根将越过虚轴,使得特征值实部由负变正,系统变为小扰动不稳定。接下来将对系统存在SEP 的情况进行大扰动稳定分析。

3.2.2 振荡失稳

在表B1 中参数的基础上,设置Pref=0.8 p.u.,改变平衡点处状态量Udc的值,作为仿真的初始点。分别令Udc=4.5 p.u.、Udc=4.6 p.u.,各PI 控制环节输入量以及δpll的时域仿真结果如附录B 图B3 所示。由图B3(a)可知,当Udc=4.5 p.u.时,外环的PI控制环节输入量振幅持续减小,说明系统没有失稳。由图B3(b)可知,当Udc=4.6 p.u.时,外环的PI控制环节输入量增幅振荡,说明直流电压控制环节失稳(交流电压控制仿真结果类似),但详细模型的PLL和电流内环的PI 环节输入量都为0,说明快动态的PI 控制环节和电流内环仍然保持稳定。

进一步通过δpll说明系统失稳模式,如附录B 图B4(b)所示,δpll表现为振荡失稳。当t≈11 s时,δpll单调发散。对比图B3(b)可知,此时PLL 环节和电流内环开始失稳。

3.2.3 单调失稳

设置Pref=0.7 p.u.。同样改变平衡点处状态量Udc初值,全阶模型的各PI环节输入量的时域仿真结果如附录B图B5所示。当Udc=4.9 p.u.时,外环的PI控制环节输入量振幅持续减小,最终回到SEP,说明系统没有失稳,如图B5(a)所示。当Udc=5.0 p.u.时,直流电压控制环节的输入量减小,仍未回到平衡点,但详细模型的PLL和电流内环的PI控制环节输入量都为0,证明快动态的PI 控制环节已达到稳态,t≈0.6 s时,uq进一步表现为单调发散,此时全阶系统的PLL环节也产生失稳,如图B5(b)所示。

同理进一步通过δpll说明系统失稳模式,如附录B图B6(b)所示,此时δpll表现为单调失稳。

3.2.4 基于降阶DAE模型的分析

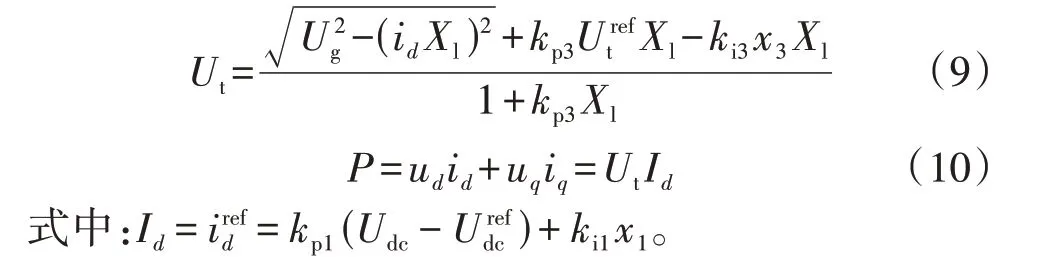

由3.1.1 节原理,外环控制的时间尺度远大于PLL,可以对原系统进行降阶,忽略PLL、电流环动态和传输线动态,进而获得3阶DAE模型,其中状态量只包含x1、x3和Udc。此时系统的微分方程可简化为式(2),其中,Ut和P均为非线性项,具体表达式如下:

接下来将对比降阶DAE 模型和全阶模型δpll的仿真结果,以进一步说明失稳和电压外环相关。使用3.2.2、3.2.3 节中相同参数和初值,对比振荡失稳和单调失稳情况下3阶DAE模型和全阶模型的时域仿真结果,如附录B 图B7 所示。在仅含有电压外环的动态时,DAE 系统的失稳模式和全阶系统基本一致,可以说明失稳模式和电压外环相关。

3.2.5 稳定边界

降阶系统采用3 阶DAE 模型,因此有可能在状态空间中描述系统的稳定边界。分别绘制外环失稳对应的2 种工况下系统稳定和失稳情形的轨迹与稳定边界的关系,如附录B图B8所示。

图B8(a)对应3.2.2 节中的振荡失稳。可以看出:稳定状态下,系统初始点在稳定边界内部,故障恢复后仍然可以回到平衡点;失稳状态下,系统初始点位于稳定边界外部,进一步振荡发散,最终遇到奇异面终止。图B8(b)对应3.2.3 节中的单调失稳:稳定状态下,系统初始点在稳定边界内部,系统恢复稳定;失稳状态下,系统初始点位于稳定边界外部,系统外环失稳,进而导致DAE 系统的轨迹遇到奇异面,仿真终止,此时对应全阶系统的PLL 失稳,说明在外环失稳的驱动下系统会进一步发生PLL失稳。

3.2.6 小结

对于外环投入的VSC 控制模式,并存在SEP 的前提下,系统也存在2 种失稳模式:当Pref较大,接近小扰动稳定临界值时,系统的稳定域较小,稳定边界由不稳定极限环构成,当状态量值位于稳定域外时,系统发生振荡失稳;而当Pref逐渐减小,远离小扰动稳定临界值时,系统的稳定域逐渐增大,直到稳定边界接触奇异面,此时系统单调失稳。

通过降阶模型的时域仿真,可以说明这2 种失稳模式都和外环直流、交流电压控制环节相关,对应了式(9)、(10)中外环控制环节的非线性。

3.3 考虑PWM饱和时电流环失稳

实际运行的VSC 都存在各种饱和或限幅环节,用以确保VSC运行在安全的范围内,其中PWM饱和由PWM 的物理特性决定,而非人为设置的环节,具有一般性,因此有必要讨论考虑PWM 饱和时系统的失稳模式。

3.3.1 PWM饱和

在图2 所示的控制框图模型基础上,考虑PWM过程,当调制比m过高时,经过PWM 的内电势实际值不一定等于其指令值,假设VSC 的内电势是通过正弦脉宽调制(SPWM)产生的。标称频率下E的基波分量由PWM 输出的电容电压Udc产生。对于m=Eref/(Udc/2)≤1(Eref为VSC 内电势参考值),实际内电势E与m成正比,即:

当m>1,即PWM 进入过调制的饱和状态时,线性关系不再成立,变为:

VSC 内电势参考值Eref与实际值E之间的关系如图8 所示,图中内电势为标幺值。当m趋于无穷大时,内电势上限Eup为2Udc/π。

图8 考虑PWM饱和的内电势参考值和实际值Fig.8 Internal potential reference value and actual value considering PWM saturation

3.3.2 平衡点存在性分析

对平衡点处的各状态变量,同样可以通过代数方程求解。系统各参数如附录C 表C1 所示,首先求解不考虑饱和时系统各电气量的值,即ix、iy、ux、uy,若平衡点处内电势E超过其上限值,说明此时系统不存在平衡点。

采用表C1 的参数,随着Pref的变化,可以得到系统平衡点的变化轨迹,如附录C图C2所示。

3.3.3 电流内环失稳

选取Pref=0.3 p.u.,解出平衡点,并改变时域仿真下状态量的初值,分别令x3=-0.060和x3=-0.066,可得到2 组仿真结果,分别对应系统稳定和失稳,并绘制各PI 环节的输入量时域仿真曲线,如附录C 图C3所示。对系统未发生失稳的情形,各PI 环节输入量在初始偏离0 后,快速衰减并逐渐回到0,说明系统依旧保持持稳定,如图C3(a)所示。失稳情况下,图C3(b)中对应d轴电流内环PI 环节在降阶DAE 模型和全阶模型下发生失稳,q轴电流环类似。因为此时系统的快动态过程无法快速回到稳态,因此外环以及PLL 的控制目标也无法实现,图C3(b)中电压外环和PLL环节PI环节的输入量也表现为失稳。

4 结论

本文针对最常见电力电子接口设备VSC,研究了并网VSC 的大扰动失稳模式。得到主要结论如下。

1)VSC 的动态特性由控制过程主导,给出了控制环节失稳的定义,发现并分析了并网VSC外环、内环及PLL不同环节对应的大扰动失稳模式。

2)系统各环节的大扰动失稳均和环节内的非线性环节相关。PLL 环节的非线性主要来自输入量uq;外环的非线性主要来自于交流电压q轴分量以及有功功率的表达式;电流内环中的非线性是由PWM饱和特性引起的。

3)不同于传统同步机并网系统,VSC-IB 系统的稳定边界既包含UEP 的稳定流形,也包含不稳定极限环,分别对应单调失稳、振荡失稳2 种失稳形态。主要原因是小扰动稳定分析中存在亚临界Hopf 分岔,因此分岔点附近稳定边界受其限制。此外,稳定性边界也受PWM饱和的约束。

4)不稳定极限环作为VSC-IB 系统稳定边界的重要组成部分,如果系统工作点在Hopf 分岔附近,则稳定性边界可能会受到极限环限制,系统表现为振荡失稳。如果系统工作点远离Hopf 分岔,稳定边界由UEP的稳定流形组成,则系统表现为单调失稳。

本文的主要目的是尽可能全面地梳理VSC并网系统中可能出现的大扰动失稳模式,因此并没有过多地考虑所采用的参数是否符合实际情况。针对实际中的参数取值范围,在所发现的某些失稳模式中一些模式有可能出现,而有些出现的概率很低,这是后续研究的重要内容。本文全面地分析了VSC并网系统大扰动失稳模式和稳定边界组成,这为电力电子设备并网的大扰动稳定分析奠定了基础。

附录见本刊网络版(http://www.epae.cn)。