一种基于FPGA的多面阵雷达时序控制器设计*

2022-08-01陈昌勇张良俊刘文佳冯正康

陈昌勇,张良俊,杨 媛,刘文佳,叶 舟,冯正康

(上海航天电子技术研究所,上海 201109)

0 引 言

雷达作为一种性能稳定的探测设备,对运动目标具有较好的检测能力,是防御威胁的重要手段。然而对于无人机这类目标,背景杂波强,目标回波微弱,受强地杂波影响严重,因此目标检测更加困难[1]。传统的单面旋转雷达尽管已经从一维相扫发展到二维相扫,但对于无人机探测来说,雷达数据率小,不利于跟踪机动性强的无人机目标。多面阵雷达是相控阵雷达的一种,其利用多个二维相扫阵面协同工作实现多空域覆盖,省去了传统雷达的伺服机构,拆装灵活,同时可大幅度提高雷达数据率,改善雷达多目标跟踪能力,能有效地探测无人机类“低慢小”目标[2-5]。

针对某多面阵雷达工作模式多、资源调度复杂、时序控制繁琐等问题,本文提出了一种基于现场可编程门阵列(Field Programmable Gate Array,FPGA)的时序控制器设计方案,以满足多面阵雷达的应用需求,在反无人机雷达领域具有广泛的应用前景。

1 时序控制系统

多面阵雷达时序控制系统如图1所示,该系统由显控计算机、信号处理系统、时钟源、定位定向设备以及4个天线阵面组成。其中,显控计算机主要完成雷达工作阵面选择,雷达工作模式、工作状态等命令的控制;信号处理系统由中央处理器(Central Processing Unit,CPU)、FPGA等组成,CPU根据显控命令完成时序控制参数等调度报文的下发,FPGA用于实现时序控制器的主要功能;时钟源作为信号处理系统的时钟来源;定位定向设备用于给信号处理系统传输秒脉冲等信息;天线阵面由波控机、频综接收机以及天线组成,4个天线阵面根据时序控制器的时序信号和报文进行协同工作并回告状态。

图1 多面阵雷达时序控制系统示意图

2 时序控制器设计

2.1 时序控制器组成

作为时序控制系统的核心,时序控制器要负责控制多个阵面协同工作,实现雷达时间资源以及报文的实时分配。因此,要求时序控制器处理速度快、配置灵活、接口丰富。综合考虑,选用FPGA完成该控制器的设计。

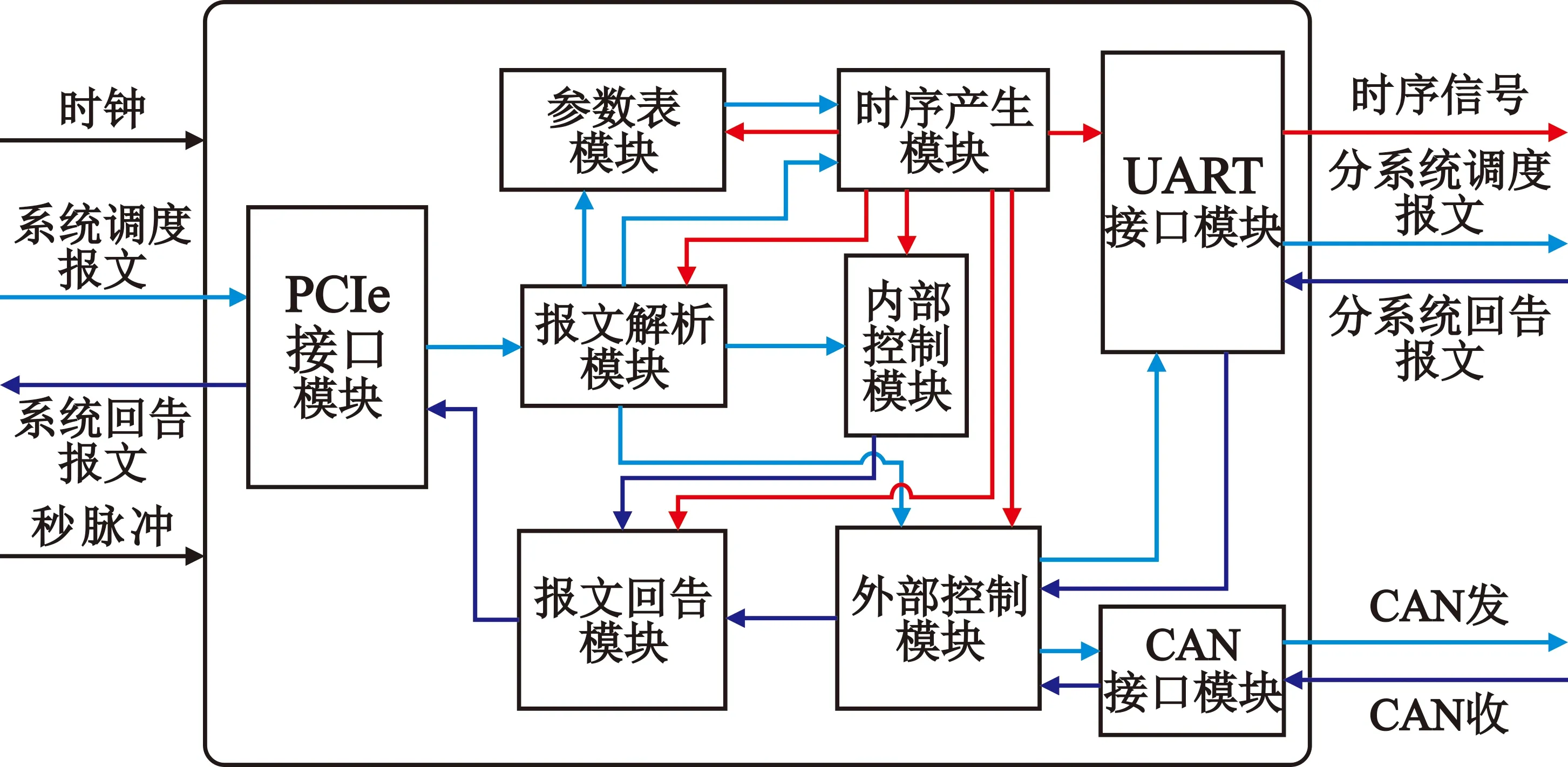

如图2所示,时序控制器具备接口控制、报文收发、时序产生等功能,由Peripheral Component Interconnect Express(PCIe)接口模块、参数表模块、报文解析模块、报文回告模块、时序产生模块、内部控制模块、外部控制模块、通用异步收发器(Universal Asynchronous Receiver/Transmitter,UART)接口模块、控制器局域网络(Controller Area Network,CAN)接口模块等组成。

图2 时序控制器组成框图

2.2 工作时序设计

在多面阵雷达中,时序控制器的主要功能之一便是根据调度报文及参数产生时序信号,用于控制各个分系统之间有条不紊地工作。

时序信号的产生主要由PCIe接口模块、报文解析模块、参数表模块、时序产生模块共同完成,随后通过UART接口模块送出。多面阵雷达的主要工作时序如图3所示。

图3 多面阵雷达主要工作时序示意图

2.3 PCIe总线接口设计

PCIe总线是一种高速串行点对点双通道高带宽传输总线,相比于其他主流总线,其速度快、实时性好、可控性佳,被广泛用于实现外部设备与CPU的通信[6]。

本设计利用FPGA自带IP核等资源实现了PCIe总线接口的功能,保证了CPU和FPGA之间的快速通信。

图4是PCIe接口模块顶层设计原理图。其中,读写地址和读写数据位宽均为16 b;模块内读写分开,使用独立接口和独立时钟;内部提供自定义寄存器,可灵活配置相应功能。

图4 PCIe接口模块顶层设计原理图

2.4 UART接口设计

多面阵雷达工作时,时序控制器需要与多个分系统进行稳定的通信,将时序信号和调度报文及时送出;与此同时,接收来自各分系统的状态回告,确保整个通信链路有序运行。为此,本设计选用RS422标准来实现UART接口的功能。利用差分传输的优势,保证了更好的抗噪声性能和更远的传输距离[7]。

UART接口模块顶层设计原理图如图5所示。在本设计中,波特率、校验类型等都进行了参数化处理,可根据实际需求进行选择。

图5 UART接口模块顶层设计原理图

2.5 CAN总线接口设计

为确保多面阵雷达能更为精确地探测到目标,时序控制器需及时获取定位定向设备送出的秒脉冲、位置等信息。

考虑到CAN总线组网自由、扩展性强等优点,在与定位定向设备通信时,除秒脉冲以外的其他信息均采用CAN总线传输,秒脉冲采用RS422串口传输。

图6是CAN接口模块顶层设计原理图。模块设计时,对CAN数据率、帧格式等进行了参数化处理,便于模块的拓展与维护。

图6 CAN接口模块顶层设计原理图

3 验证方案设计

3.1 PCIe总线接口验证方案设计

PCIe总线接口的通信主要包括图7所示的两条链路。其中,链路①代表FPGA发CPU收,主要用于传输各分系统的回告BIT;链路②代表CPU发,FPGA收,主要用于传输时序参数等调度报文。

图7 CPU与FPGA通信链路图

对于PCIe总线接口的验证,可采用如下方式:

(1)对于链路①的验证,首先在FPGA中存储多组数据,通过FPGA的虚拟输入/输出(Virtual Input/Output,VIO)核来选择要发送的数据包,CPU收到FPGA给的帧中断后将收到的数据与地址存下来,然后将FPGA发送的数据包与CPU收到的数据包进行对比,验证传输是否正确;

(2)对于链路②的验证,首先在CPU中存储多组数据,分别发送给FPGA,FPGA将收到的数据与地址存下来,然后将CPU发送的数据包与FPGA收到的数据包进行对比,验证传输的正确性。

3.2 UART接口验证方案设计

对于UART接口的验证,可利用USB转串口工具,连接时序控制器待测的RS422接口与计算机,分别验证以下两个功能:

(1)利用计算机上的串口调试助手按固定周期进行发包,用FPGA进行收包,将FPGA收下来的数据包与串口调试助手发送的数据包进行对比,验证UART接口接收功能是否正常;

(2)首先在FPGA中按包格式存储多组数据,然后通过FPGA的VIO核来选择要发送的数据包,利用串口调试助手进行收数,最后将FPGA发送的数据与串口调试助手收到的数据进行比对,验证UART发送功能是否正常。

3.3 CAN总线接口验证方案设计

CAN总线接口的验证可借助CAN调试工具连接时序控制器待测的CAN接口与计算机,验证CAN接口的收发功能。

为验证CAN接口的接收功能是否正常,利用计算机上的CAN调试助手作为发端,选好数据率和帧格式,向FPGA发送数据包,FPGA在收到数据后,将数据与CAN调试助手发送的数据进行比较。

为验证CAN接口的发送功能是否正常,首先在FPGA中按包格式存储多组数据,然后通过FPGA的VIO核来选择要发送的数据包,利用计算机上的CAN调试助手作为收端,接收FPGA发送的数据,最后将FPGA发送的数据与CAN调试助手收到的数据进行比较。

3.4 工作时序验证方案设计

时序控制器设计完成后,首先对PCIe总线接口以及UART接口进行验证,验证无误后再对产生的时序信号作如下验证:

(1)用显控计算机对雷达工作模式等命令进行下发,利用FPGA开发工具对时序信号进行抓取,通过时序信号的内部计数值,可以确定时序信号的脉宽和周期,再与所设计的参数进行对比,即可验证时序信号是否正确;

(2)在(1)验证无误的基础上,利用示波器抓取时序控制器待测RS422接口送出的时序信号,通过测量其脉宽和周期,对比设计参数,验证其信号是否正确。

4 在线验证

根据提出的验证方案,设计优先对PCIe总线接口、UART接口以及CAN总线接口的功能进行了正确验证。在此基础上,通过FPGA开发工具将设计文件烧写、固化,对时序控制器的主要功能进行了在线验证。

4.1 工作时序验证

多面阵雷达要求时序控制器根据各种工作模式和状态产生正确的时序信号,从而保证多个阵面的有序工作。

为了在线验证时序控制器产生的时序信号是否正确,实验时通过显控计算机来切换雷达工作模式和状态,同时利用FPGA开发工具对时序信号进行在线抓取。

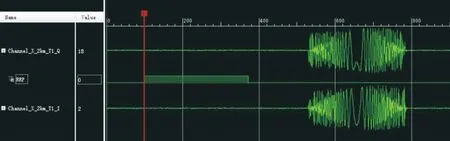

图8是多面阵雷达实际工作时抓取到的某种工作模式下的主要工作时序信号,通过与设计参数进行对比,发现时序控制器产生的时序信号符合要求。通过此方法,本设计也验证了其他工作模式和状态下产生的时序信号,结果正常。

图8 多面阵雷达主要工作时序验证图

4.2 模拟中频仿真验证

时序控制器不仅要产生时序信号,还要根据时序信号去调度各个阵面工作,只有时序信号与调度参数能够成功匹配,才能确保整个控制的正确性。

为了在线验证此功能,本设计利用显控进行模拟中频仿真等命令的下发,利用时序控制器将调度参数和产生的时序信号发送到各阵面,频综接收机根据收到的时序和参数产生模拟中频仿真信号,然后通过模数转换子卡将信号送到FPGA进行抓取验证。

图9是多面阵雷达模拟中频仿真验证图,主要验证时序控制器在不同工作脉冲(Receiving Reference Pulse,RRP)下工作时脉宽与目标信号是否匹配,同时验证2 km模拟目标采集是否正常。

(a)RRP脉宽为短脉宽时的2 km模拟中频仿真

如图9(a)所示,当RRP脉宽为短脉宽时,目标信号与脉宽相匹配;同时,通过计算RRP上升沿与目标信号的后端距离可知模拟目标出现在2 km附近。图9(b)是RRP脉宽为长脉宽时的2 km模拟中频仿真,通过计算发现,目标信号与长脉宽相匹配,目标出现在2 km附近。由图9可知,时序控制器相关功能运行正常,满足设计要求。

通过模拟中频仿真实验在线验证了时序控制器的时序产生、参数调度等主要功能。

5 结 论

本文提出了一种基于FPGA的多面阵雷达时序控制器设计方案。在时序控制器的设计过程中,该方案优先进行了通用化、参数化、可测试性设计,有利于程序的维护、拓展以及产品功能的测试验证;充分考虑了多面阵雷达工作模式多、资源和时序调度复杂的问题,利用FPGA接口丰富、速度快的优点实现了时序产生、PCIe接口等功能。

目前,该时序控制器已成功地应用于某型多面阵雷达,各项功能得到了充分验证,性能稳定,效果良好。