基于防错锁控制结构的延迟锁相环设计

2022-07-30田震唐路,2

田 震 唐 路, 2

(1.东南大学 微电子学院, 南京 210096)(2.东南大学 信息科学与工程学院, 南京 210096)

延迟锁相环DLL(Delay Locked Loop)技术的产生能有效地解决传输过程中出现的时钟延迟和偏移问题,已广泛用于时钟发生器、时钟数据恢复电路、高速存储接口等各类电路中[1-2]。由于其具有受温度和电源电压等非理想因素的影响小、单极点系统无条件稳定等优点[3],可以提供稳定的时钟信号,成为高精度电路时钟源的首选电路。

然而在工程实践中,延迟锁相环常常出现锁定和谐波锁定等异常锁定状态,导致整体环路工作异常。国内延迟锁相环的相关教材中,并未对该现象给出合理的解决方案,造成课程教学与实际电路设计之间存在较大的差距。针对该现象,文献[4]提出了一个解决该问题的方法,但是不适用于产生多路时钟输出的应用场景。文献[5]提出了另一种内嵌辅助锁相环的DLL结构,该结构虽然可以避免死锁定和谐波锁定,但电路的功耗和面积相比普通的DLL结构大了将近一倍。文献[6]提出了用数字算法辅助校准,但电路实现复杂,仅适用于全数字延迟锁相环。

据此,结合实践设计了一种基于防错锁控制结构的延迟锁相环,使用该结构的延迟锁相环有效地解决了死锁定或谐波锁定等问题,电路结构简单、功耗低且适用于多路时钟输出。这种结构的延迟锁相环的设计过程有助于学生理解并解决死锁定和谐波锁定问题,且加深了对延时锁相环精度和速度的理解。

第一和第二部分分析了DLL工作原理和具体设计细节,第三部分展示了电路版图和后仿真结果。最后,第四部分进行总结。

1 原理分析

1.1 整体结构

基于防错锁控制结构,已设计并实现了100路时钟输出的延迟锁相环电路。该电路在理想20 MHz的时钟驱动下,能在2 μs内准确锁定。输出时钟相位延迟均值为496 ps,确定性抖动为3.82ps,自身随机性抖动为2 ps,可满足开关电容运放、模数转换器等电路多时序且高精度的需求。

如图1所示,DLL主要由鉴相器PD(Phase Detector)、电荷泵CP(Charge Pump)、环路滤波器LPF(Loop-Phase Filter)、快速锁定鉴相器QPD(Q-uick Phase Detector)和压控延时链VCDL(Voltage-Controlled Delay Line)五部分组成,为了适应不同频率,在DLL电路中可以加入四分频模块(Divider)用于调节输入时钟频率。

图1 DLL电路结构框图

当外部时钟输入DLL时,从VCDL模块中间抽头产生多路相位延时的时钟。输出反馈时钟信号(CLK_FB)和与输入参考信号(CLK_REF)相比,相位延迟2π。

1.2 防错锁控制结构

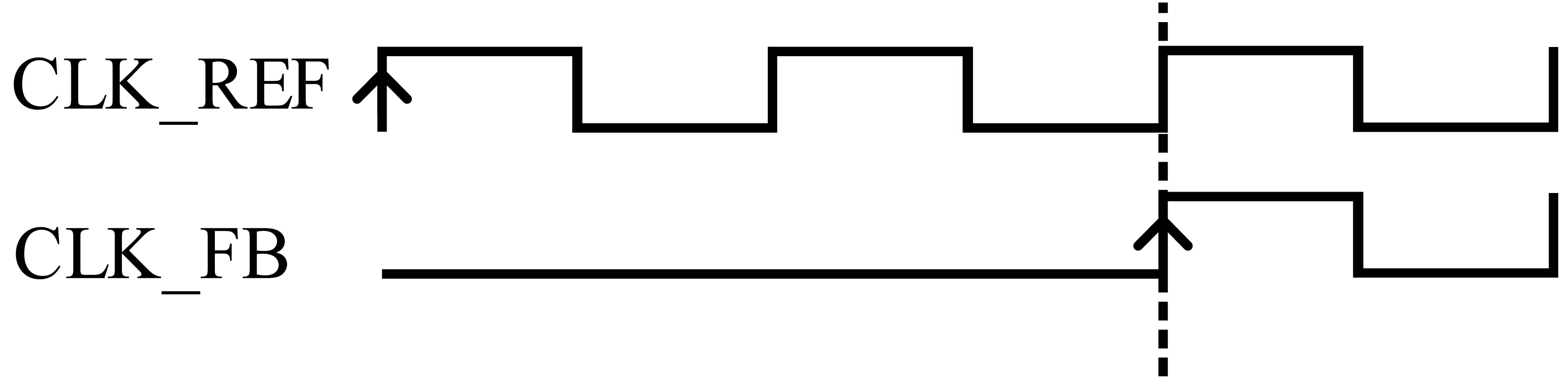

对于一个刚启动的DLL电路而言, CLK_FB相对于CLK_REF延迟相位是不确定的。如图2所示,这种不确定性会造成DLL锁错时钟边沿,最终导致DLL出现死锁或谐波锁定。

(a)DLL正确锁定

(b)DLL死锁定

(c)DLL谐波锁定图2 DLL锁定状态分析

如图1所示,为了避免死锁或谐波锁定等异常状态的出现,本文设计了一种防错锁控制结构,主要由QPD和PD两部分组成。其中QPD输入信号CLK1……CLKn是VCDL抽头产生的分时钟。

以延时过小出现死锁定为例,详细分析整体环路工作过程,如图3所示。当QPD检测到延时过小,使得CLK_FB第一个上升沿进入A区间(QPD有效,PD无效)之后, UP_CAC信号变为高电平,同时PD_EN关闭,UP_PD和DOWN_PD无效。此时QPD控制电荷泵并对LPF充电,增大延时,如图3(a)所示。当延时增大到一定程度时,CLK_FB第一个上升沿进入B区间(QPD无效,PD有效),检测到该状态之后,UP_CAC和DOWN_CAC无效,同时PD_EN变为高电平,打开PD工作开关,进行相位细调,PD控制电荷泵对LPF充电,继续增大延时,如图3(b)所示。PD不会一直对LPF充放电,只有检测到CLK_REF上升沿UP_PD信号才会出现窄脉冲信号,实现细调的目的,同时也消除了电荷泵的鉴相死区,若干个周期后,环路锁定,如图3(c)所示。

(a)A区间,QPD工作,PD关闭

(b)B区间,QPD关闭,PD工作

(c)DLL最终锁定波形图图3 DLL锁定过程关键节点波形图

2 关键子电路设计

2.1 快速锁定鉴相器的设计

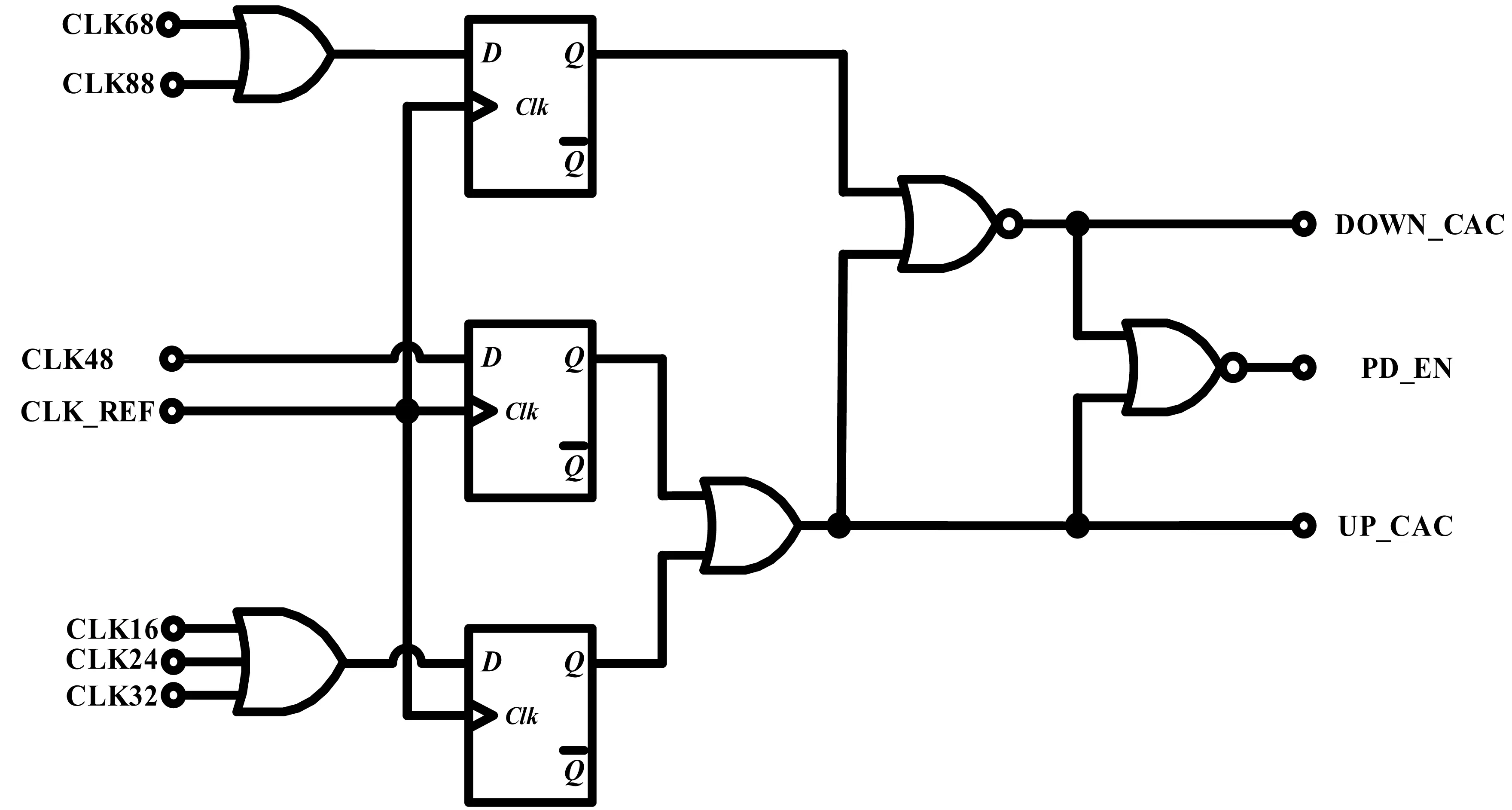

防错锁结构主要由鉴相器和快速锁定鉴相器组成。如图4所示,快速锁定鉴相器电路由三个D触发器和相关逻辑门组成,其中CLK_REF作为三个D触发器的时钟信号,三个D触发器的数据端分别是VCDL产生的分时钟信号或其组合,根据它们的相位关系,来判断VCDL的相位延时是否满足锁定条件。如不满足,输出相关的调制信号DOWN_CAC、UP_CAC、PD_EN,调节延时。

图4 快速锁定鉴相器原理图

最终仿真结果显示快速锁定鉴相器的鉴相范围为(0, 1.18π) ∪(2.19π, 6.4π)。

2.2 新型鉴相器的设计

DLL须在相位差为2π左右进行充放电,在此相位差附近经典PFD结构鉴相范围不满足DLL的设计要求,如图5(a)所示,设计了一种新型PD结构。

(a) 新型鉴相器原理图

(b) 新型鉴相器鉴相范围图5 新型鉴相器原理图

PD由6个反相器、四个D触发器、两个与门组成。与门的作用在于使得QPD电路工作时PD不进行工作,当粗调完成后PD_EN置1,PD开始工作。PD能比较相位差,同时能将相位差转换成脉宽可调的脉冲信号,并用脉宽表示相位差的大小,输出的脉冲信号转化为环路滤波器上的充放电电流。在鉴相器设计过程中要重点关注鉴相范围和鉴相精度两个设计指标。首先要保证鉴相无死区,在满足这个条件的前提下尽可能的提高鉴相范围。如图5(a)所示,由电路仿真可以得到本文PD的鉴相范围。

QPD的鉴相范围为(0, 1.18 π) ∪(2.19 π,6.4 π),所以鉴相器的鉴相范围只需要(π, 3 π)即可,实际仿真结果,PD的鉴相范围为(0.967 π,2.945 π),可以保证两者结合使用无鉴相死区,符合设计要求。

3 电路后仿真结果

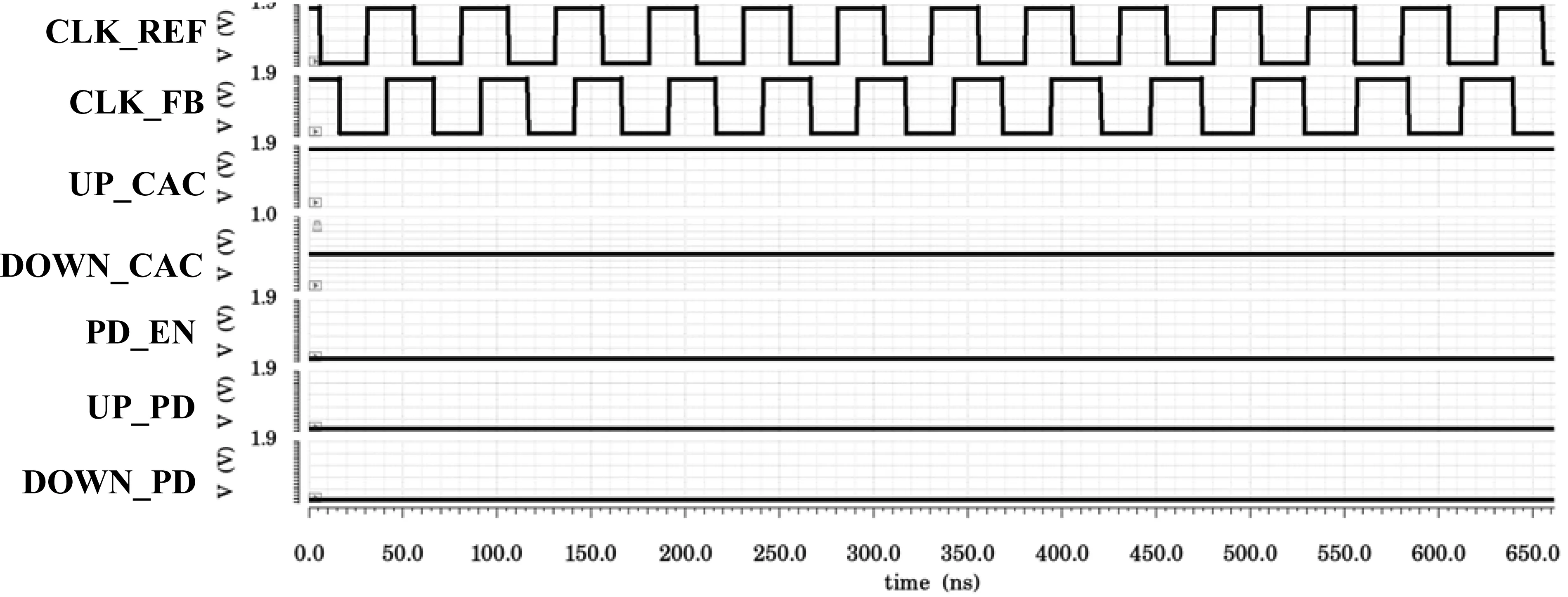

基于0.18 μm CMOS工艺完成本次电路设计、版图设计以及后仿真。如图6所示,100路时钟输出的DLL版图总面积为415 μm*460 μm。在常温27 ℃、1.8 V电源电压、tt工艺角下,当输入信号周期为20 MHz时,关键节点的波形图如图7所示,锁定过程基本和理论分析一致。

图6 100路时钟输出的DLL版图,总面积为415 μm*460 μm

(a)锁定过程中,A区间,QPD工作,PD关闭

(b)锁定过程中,B区间,QPD关闭,PD工作

(c)最终锁定各个关键节点波形图7 基于0.18 μm CMOS工艺27℃、1.8 V电源电压、tt工艺角下后仿真DLL锁定波形图

如图7(c)所示,在2 μs内延迟锁相环能准确锁定,锁定之后CLK_FB比CLK_REF延迟一个周期。

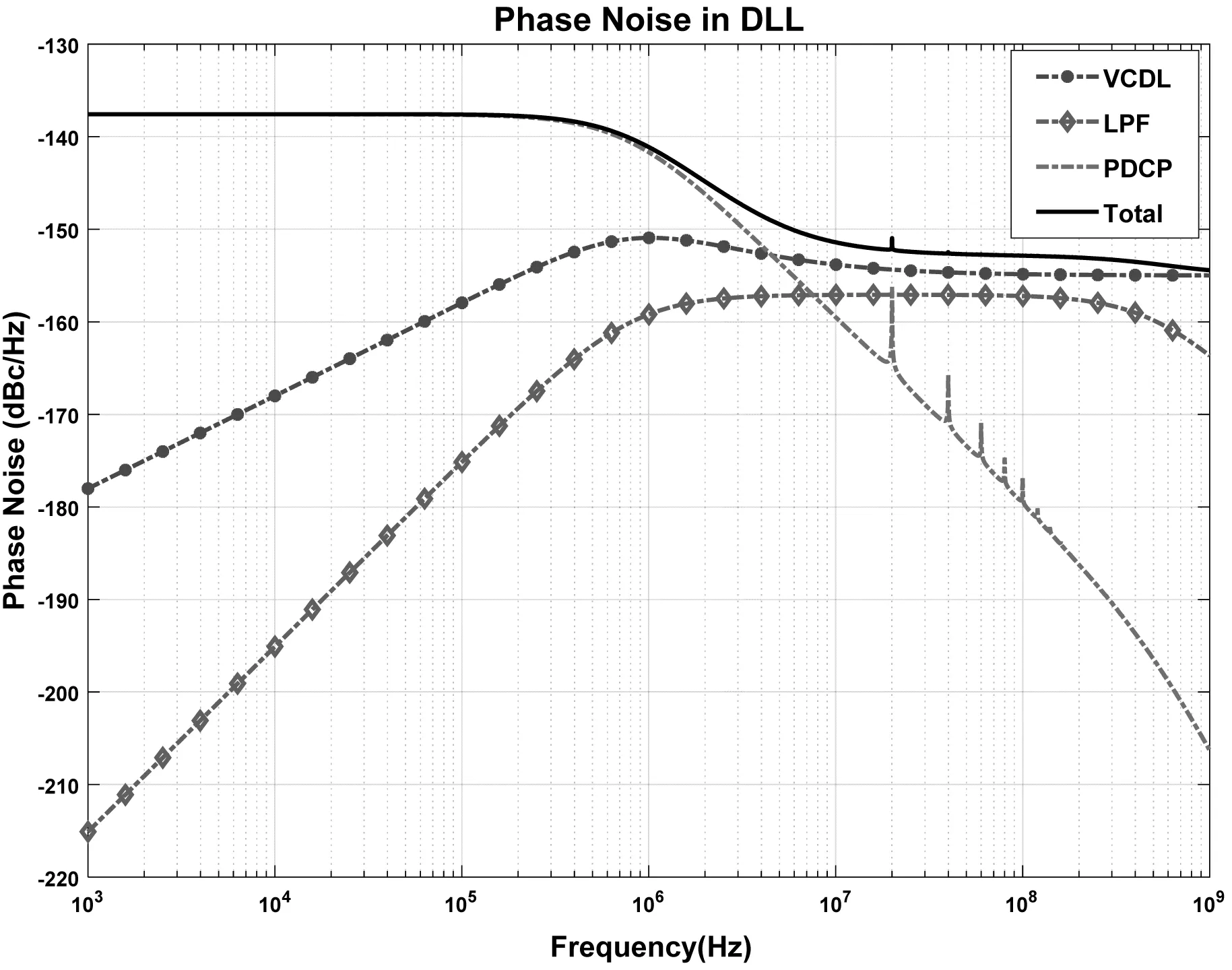

在理想20 MHz的时钟驱动下,各相时钟输出分布均匀,相邻两路相位间距均值为496 ps,最大时钟偏差为20 ps。如图8(a)眼图结果所示,DLL确定性抖动为3.82 ps;如图8(b)所示,根据DLL整体环路的相位噪声拟合结果在Matlab中计算得到DLL随机性抖动约为2 ps。上述结果表明:设计的DLL电路满足低抖动且快速准确锁定要求。

(a) DLL眼图仿真结果

(b) DLL相位噪声拟合结果图图8 基于0.18 μm CMOS工艺27 ℃、1.8 V电源电压、tt工艺角下后仿真DLL结果图

4 结语

提出了一种防错锁控制结构,有效地解决了延迟锁相环中出现的死锁定或谐波锁定等问题。实际仿真验证之后,采用该结构和控制方式的延迟锁相环能同时兼顾锁定速度和锁定精度,可以为高精度电路提供稳定、准确、多相位低抖动的时钟源。并有助于学生了解防错锁在DLL实际电路中的实现方法和意义,增强学生学习延迟锁相环相关知识的系统性。对于改进微电子集成电路教学方式和指导实践具有一定的意义。