面向超高速以太网ADB-DMA的设计与实现

2022-07-12吴剑箫

吴剑箫 王 鹏

1(中国科学院上海高等研究院 上海 200120) 2(中国科学院大学 北京 100049) 3(上海大学计算机工程与科学学院 上海 200444) 4(数学工程与先进计算国家重点实验室 江苏 无锡 214215)

0 引 言

DMA技术是计算机系统中一种高速高效的数据传输技术。使用DMA控制器可直接实现内存与外设间数据交换,减少对处理器的占用时间,从而提高整体系统性能[1],多应用于视频、音频和网络接口等高吞吐率外设。DMA控制器有两种实现方式:寄存器模式与描述符(descriptor)模式[2]。在寄存器模式中处理器直接控制DMA相关寄存器,配置相关传输参数,控制数据传输的启动与停止。它具有较好的数据传输性能,但需要处理器对寄存器进行实时配置,灵活性较差。描述符模式需要处理器在内存中预先布设好用于指示DMA操作的描述符,DMA控制器通过描述符获得缓存地址、数据长度等信息进行操作,并通过改写描述符与处理器或软件进行交互,因而具有较强的灵活性。通用外设接口协议如以太网、PCIe等常使用该方式实现网络协议栈的标准化处理。配置并更新描述符需要DMA控制器与处理器多次内存读写交互,因此需要处理器频繁参与,总线效率低下。

本文提出一种新型自适应双缓冲DMA(ADB-DMA)架构,在保证标准协议栈兼容处理的前提下,可大幅提高用户数据吞吐量,最大程度减少对处理器的打扰,使总线效率达到最大化。该DMA控制器根据帧类型对数据包进行分类,对标准协议栈包,如IP、ARP与RARP等,使用基于描述符DMA方式进行传输;对用户数据包则进行寄存器模式DMA传输。该架构结合了两种DMA传输模式的优点,在保证高传输性能的同时支持标准网络协议栈处理,方便软件移植。通过仿真与FPGA测试与Synopsys公司以太网DMA控制器[3]进行对比,该自适应双缓冲DMA控制器结构具有对处理器打扰小、带宽利用率高、处理流程简单等优点。

1 自适应双缓冲DMA(ADB-DMA)的结构与原理

1.1 自适应双缓冲DMA结构

以太网等高速接口协议的帧格式中含有若干字节的类型字段,用于指示所传输数据对应协议。通过自定义该类型字段,可将用户数据与基于标准协议栈数据包进行有效区分。ADB-DMA能够根据类型字段自适应选择对应的DMA方式对该数据进行传输,其结构如图1所示。

图1 自适应双缓冲DMA结构

在进行数据传输时,高速接口向DMA控制器发送DMA请求,DMA控制器将该请求传递到处理器,申请系统总线的控制权。处理器会对该请求进行响应,并对DMA控制器进行控制,根据帧类型选取数据传输方式,配置对应模式下的寄存器后使DMA控制器开始进行数据传输。DMA控制器将对应读写信号传递给内存与接口,将对应数据地址传递给内存,从而实现高速接口对内存的直接访问。待数据传输完毕后,向处理器发送中断,将系统总线的控制权交还给处理器。

使用描述符模式DMA传输标准协议栈包。描述符中包括软硬件握手标志、控制状态、缓存地址、数据长度等信息。通过寄存器可配置描述符的起始地址,描述符在内存中可采用环形链表组织形式。各描述符的地址首尾相连。在传输完当前描述符后,描述符地址更新为下一个描述符地址,当处理完最后一个描述符后,描述符地址重新更新为首个描述符的地址。

使用寄存器模式DMA传输用户数据,并使用双缓冲对数据进行接收,该模式下需要配置的寄存器有起始地址寄存器、数据包长寄存器、总数据长度寄存器、源地址和目的地址寄存器、中断所需包数寄存器、控制状态寄存器、中断状态寄存器等。通过配置起始地址寄存器指示收发数据位置。

1.2 自适应双缓冲DMA工作原理

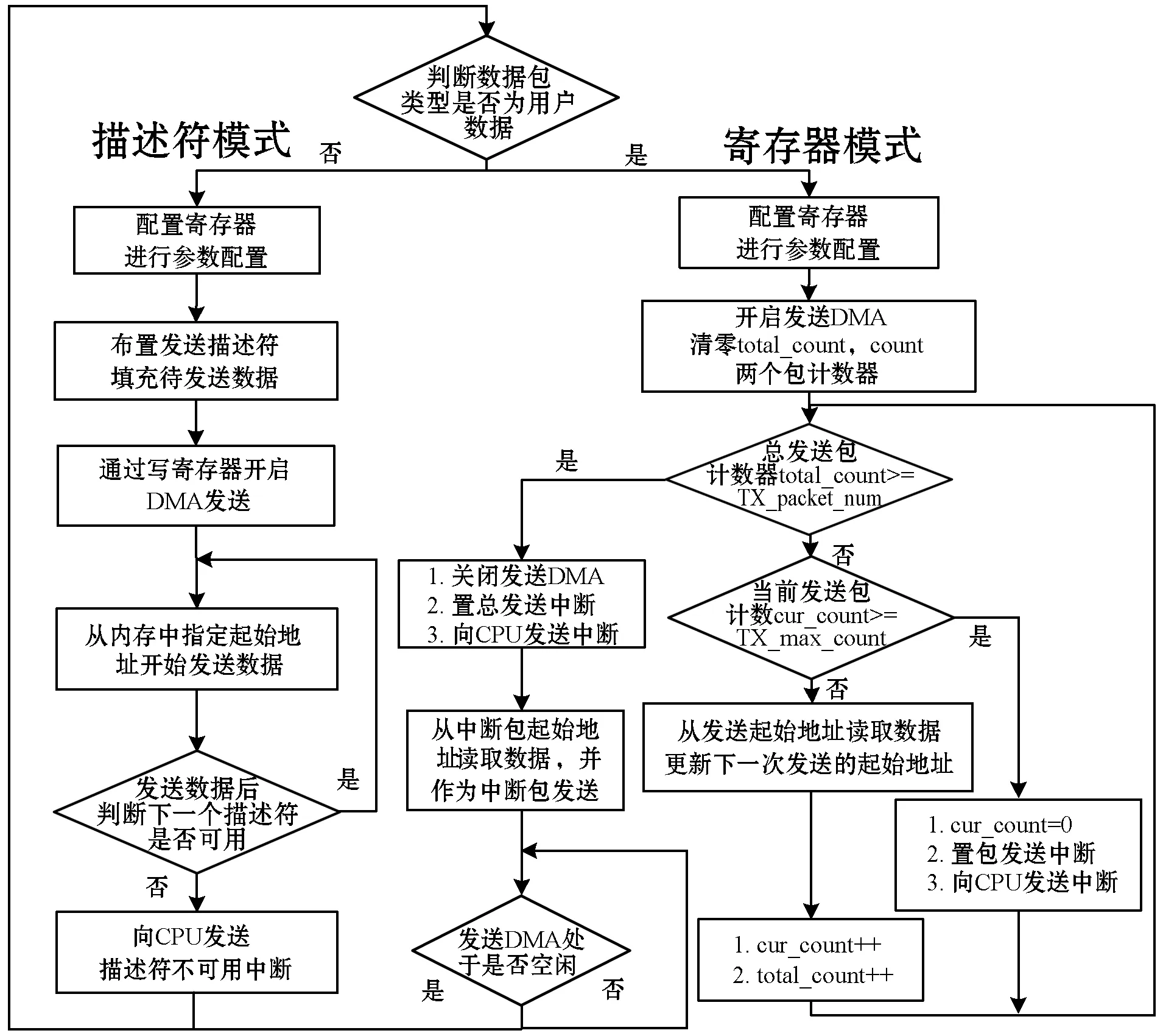

该DMA结构在工作时首先根据帧类型,选取DMA的传输模式,其工作原理如图2所示。

图2 DMA发送流程

发送工作流程:

(1) 判断发送数据是否为用户数据。

(2) 若发送数据为用户数据,选用寄存器模式DMA进行发送。配置发送端寄存器,进行起始地址、包长、总发送长度等参数的配置。

(3) 写发送控制寄存器,开启DMA发送操作,并清零总发包计数器total_cnt与当前发包计数器cur_cnt。

(4) 判断发包计数器是否达到总发包数与中断所需发包数。

(5) 若两个计数器均未达到要求值,则从发送数据起始地址取出一个包的数据,并更新发送数据起始地址。两个计数器的计数值加1。

(6) 若当前发包计数器达到中断所需包数,则清除当前发包计数器。在中断寄存器中置包发送中断,向CPU发送中断。返回步骤(4)。

(7) 若总发包数计数器达到总发包数,则代表发送完成。写发送控制寄存器,关闭DMA发送;在中断寄存器中置总发送中断,向CPU发送中断。

(8) 从内存中中断包起始地址处读取数据作为中断包发送。

(9) 发送完成后读取发送DMA状态,若状态空闲,可进行下一次发送操作。

(10) 若所需发送的数据为标准协议栈包,选用描述符模式DMA进行发送。写描述符模式寄存器,配置操作模式,描述符起始地址以及中断使能。

(11) 在指定的描述符地址处开始填充发送描述符,并向描述符指定的内存位置填充所发数据。

(12) 通过写描述符模式寄存器,开启DMA发送。

(13) 将数据从指定内存地址发送。

(14) 当前发送描述符对应数据发送完毕后,发送中断并判断下一个描述符是否可用。

(15) 若下一个描述符可用则继续发送下一个描述符对应的数据,否则置描述符不可用中断,向CPU发送中断后,进行下一次数据包发送。

相比发送流程,DMA接收流程较为简单,工作流程如图3所示。

图3 DMA接收流程

接收工作流程:

(1) 判断数据包是否为用户数据。

(2) 若接收数据为用户数据,选用寄存器模式DMA进行接收。写接收端寄存器,配置两个缓冲起始地址、包长、总发送长度等参数。

(3) 写接收端控制寄存器,开启DMA接收操作。

(4) 读取中断寄存器,若缓冲满中断为高则说明缓冲中已填充了足够的数据包,可对缓冲中的数据进行接收,并清空中断。

(5) 从对应缓冲中取出数据包,并更新接收数据起始地址为另一块缓冲的地址。

(6) 若收到的包为中断包,则代表该次接收完成。复原数据接收起始地址,并发送接收完成中断。

(7) 若所需接收的数据为标准协议栈包,选用描述符模式DMA进行接收。写寄存器,配置操作模式,描述符起始地址以及中断使能。

(8) 在指定的描述符地址处开始填充接收描述符。

(9) 通过写寄存器,开启DMA接收。

(10) 将数据保存到描述符指定的地址。

(11) 当前接收描述符对应数据接收完毕后,发送中断并判断下一个描述符是否可用。

(12) 若下一个接收描述符可用则继续接收下一个描述符对应的数据,否则进行下一次数据包接收。

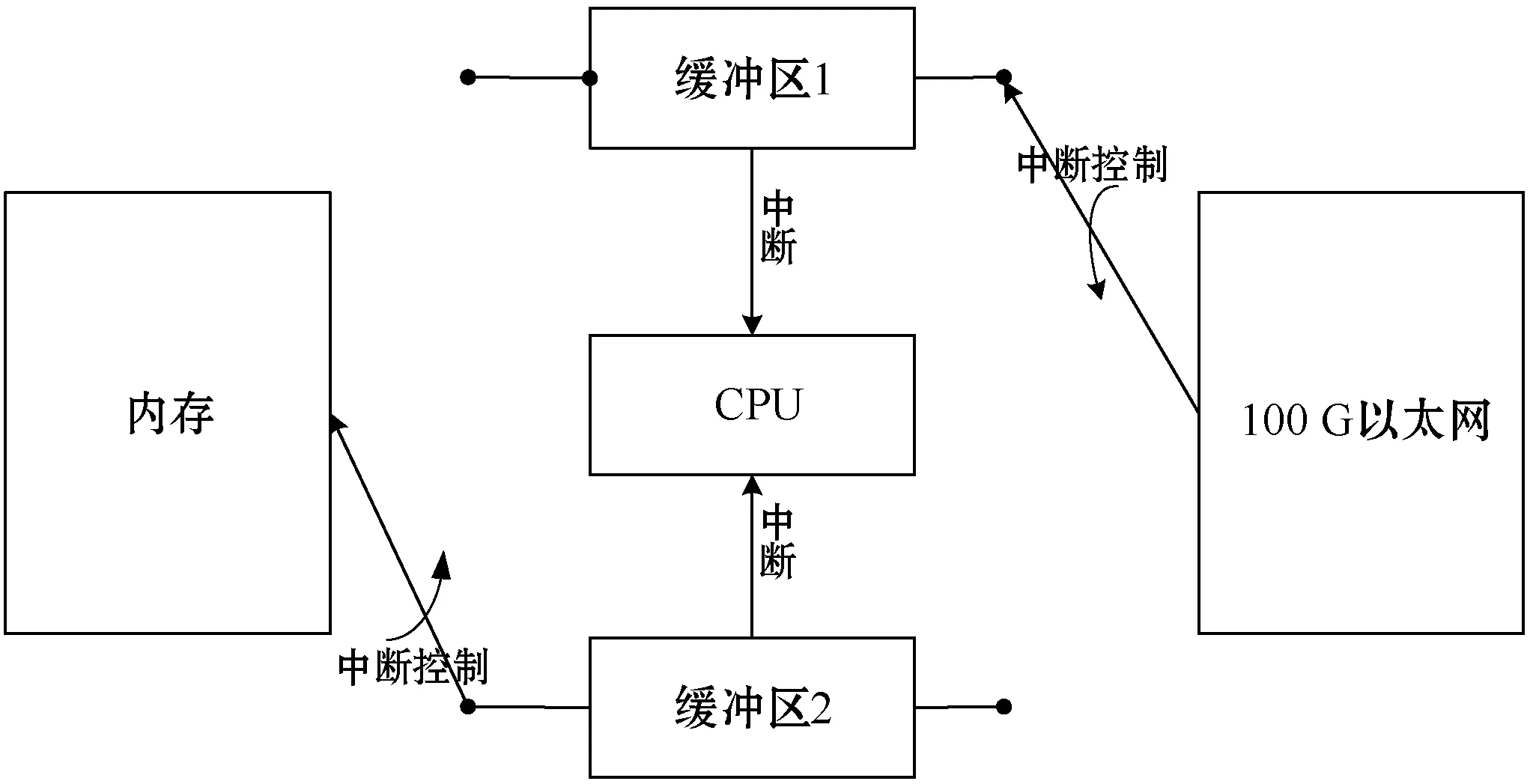

为了进一步提升大量连续用户数据接收的效率,在寄存器模式DMA中使用了乒乓操作的双缓冲结构进行数据接收[4],双缓冲结构的工作原理如图4所示。

图4 DMA双缓冲结构工作原理

接收数据首先存放在缓冲区1中,当缓冲1中数据存满时,向CPU发送缓冲满中断。DMA开始从缓冲1中读取数据,接收数据的存取地址切换为缓冲区2。当DMA将缓冲区1的数据读出后,向CPU发送中断,更新读地址为缓冲区2的地址,待缓冲区2数据准备完毕后进行读取。同时控制新数据存入缓冲区1,进行下一轮读缓冲区操作。

2 与传统描述符模式DMA的性能比较

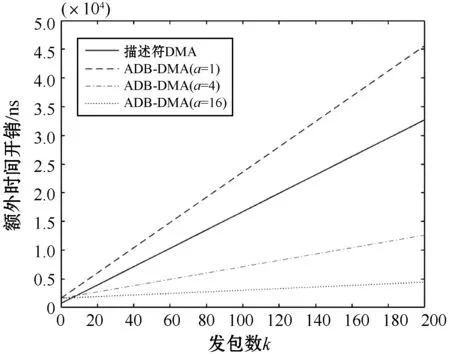

由于ADB-DMA控制器采用两种模式进行数据传输,用户数据传输带来的额外时间开销和整体数据传输效率与传统描述符模式DMA不同。以Synopsys公司以太网DMA控制器(基于描述符)为例,对两者的性能进行对比。

2.1 用户数据传输额外时间开销

(1) 传统描述符DMA。设DMA总传输包数为k,则CPU需要进行k次发送描述符和k次接收描述符的读写,总共需要进行2k次内存访问。除此之外每进行一次数据传输,CPU就需要处理一收一发两次中断,故CPU共需要处理2次中断。同时DMA引擎也需要访问内存中的描述符去判断当前描述符是否可用,从而按照描述符中的地址进行数据传输并为下一次传输改写描述符。即DMA引擎也需要进行2k次内存访问。

另外,在进行数据传输时需要配置总线模式寄存器,发送端、接收端描述符起始地址寄存器,中断使能寄存器和操作模式寄存器共5个寄存器来初始化传输参数与状态的配置;每处理一次中断需要读一次中断状态寄存器并清空一次中断状态寄存器,即需要进行7次寄存器读写操作。

设CPU处理一次中断所用的时间为t中断,进行一次内存访问的时间为t访存,读写寄存器的时间为t寄则时间开销T为:

T=2×t中断+4k×t访存+7×t寄

(1)

时间开销T为:

(2)

传统处理器完成一次中断处理所消耗时间为30个时钟周期左右[5-6],目前处理器的主频一般为3 GHz左右,故处理一次中断的时间约为10 ns;进行一次内存访问的时间约为40 ns[7],读写DMA寄存器一般需要10个时钟周期左右,一般寄存器读写时钟频率为100 MHz,故寄存器读写时间开销约为100 ns。分别选取DMA中最大传输包个数a为1、4和16,得出采用两种DMA进行数据传输时传输包数与额外时间开销的关系如图5所示。

图5 两种DMA传输时传输包数与额外时间开销的关系

2.2 总体传输效率

传输效率可以通过总线的利用率体现,总线利用率越高,数据传输效率越高。总线利用率U可通过式(3)求出。

(3)

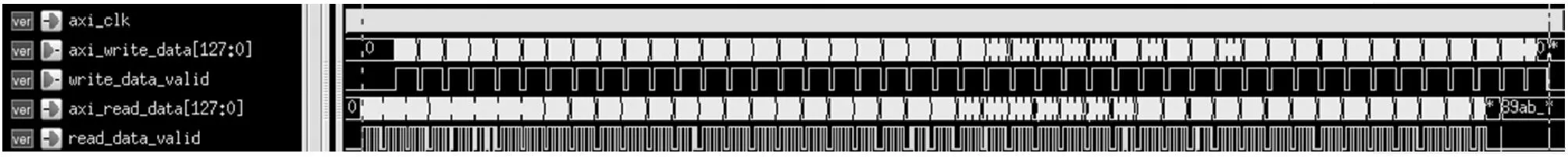

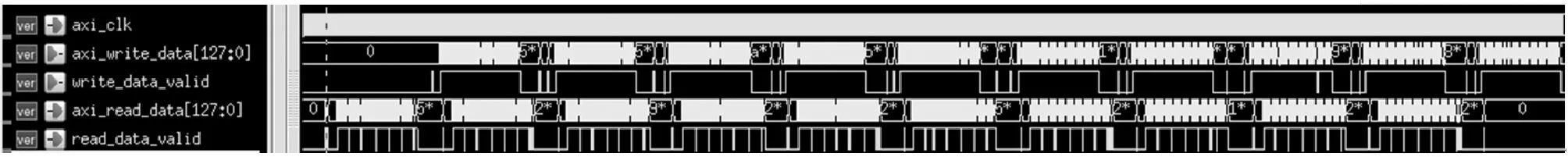

通过仿真得出该DMA与传统基于描述符DMA数据传输时AXI总线的使用情况如图6和图7所示。

图6 自适应双缓冲DMA数据传输时AXI总线情况

图7 传统基于描述符DMA数据传输时AXI总线情况

描述符模式DMA传输15 600字节数据时,AXI总线读数据使用了1 494个时钟周期,总线利用率为65.3%,AXI总线写数据使用了1 462个时钟周期,总线利用率为66.7%,平均总线利用率为66.0%。

设计的ADB-DMA传输65 536字节数据时,AXI总线读数据使用了4 518个时钟周期,总线利用率为90.7%,AXI总线写数据使用了4 494个时钟周期,总线利用率为91.1%,平均总线利用率为90.9%,比描述符模式的DMA的总线利用率高24.9百分点。

通过上述对比可见,该ADB-DMA用户数据传输所需的额外时间开销比传统的基于描述符的DMA小,总体带宽利用率比传统DMA高24.9百分点。另外本文提出的ADB-DMA虽使用了两种模式的DMA,但基于寄存器模式的DMA结构主要由寄存器构成,并没有增加太大的逻辑量。通过逻辑综合工具Design complier对两种结构的面积进行评估。描述符模式DMA总面积为31 946.91,此ADB-DMA总面积为33 662.48,该结构仅比传统描述符DMA结构的设计面积大5.37%。该ADB-DMA具有速度快、效率高、结构简单的特点。

3 设计验证与性能测试

仿真验证后,对设计进行了FPGA验证。验证选用了Xilinx KC705 FPGA开发板,为模拟CPU进行中断处理与内存操作,采用了openrisc作为软核CPU[8],并分配了两块内存空间作为发送、接收内存区。验证环境如图8所示。

图8 FPGA验证环境示意图

验证时,通过APB总线配置DMA相关寄存器,将要发送的数据放入发送内存区并开启DMA收发。数据在外部环回,通过检测接收内存区中的数据是否与发送内存区的数据一致进行验证。经验证,该DMA结构能够根据传输的帧类型自动选择对应的DMA方式进行数据传输,在不同传输参数下,该DMA均能正常工作。

验证完成后还使用该环境对设计的DMA与Synopsys公司以太网DMA控制器在FPGA上进行了数据传输性能的对比。选取最大以太网帧包长1 518字节进行长时间连续DMA传输,设计的双缓冲DMA与传统基于描述符的DMA的总线利用率分别为79.8%与58.3%。受限于频率因素,在FPGA中总线频率和时钟关系与实际应用中略有差别,因此测得的带宽利用率与仿真结果存在差异。但通过两种DMA的对比,仍能说明设计的自适应双缓冲DMA具有速度快、效率高的特点。

4 结 语

为适应百G以太网等超高速协议的应用需求,本文提出一种新型的ADB-DMA结构,可根据传输帧类型自适应完成对标准协议及用户数据包的处理。相较于传统基于描述符DMA控制器,ADB-DMA数据传输额外时间开销更低,且总体带宽利用率提高了24.9百分点,而面积开销增加仅为5.37%。目前该结构已成功应用于国产芯片100 G以太网接口,从而为国产集成电路自主可控提供有力支撑。