基于FPGA的道岔信号采集和故障监测单元设计

2022-07-03李东庆李常辉

蒋 婷 吴 磊 李东庆 李常辉

(上海电气泰雷兹交通自动化系统有限公司,上海 200120)

近年来,随着电子电路技术的不断进步,全电子联锁产品在铁路行业的应用数量逐年增加。目前,已经在地铁或大铁信号系统中应用的全电子联锁产品一般都是将功能执行单元和信号监测单元分别布局在不同的电路板卡上,即执行单元和监测单元为2 个独立的产品。未来在体积、功能和安全方面对全电子产品提出了更高的要求和挑战。新一代的全电子联锁产品将向更安全、更小型以及更强的数据处理能力的方向发展。把信号监测单元逐步集成到功能执行单元中,使产品具有更简单和更小型的特点。该文提出了一种具有实时性强、可灵活配置且低成本的基于FPGA 的道岔信号采集和故障监测单元的解决方案,由于篇幅所限,该文重点介绍与FPGA 相关的部分。

1 信号采集和故障监测整体架构

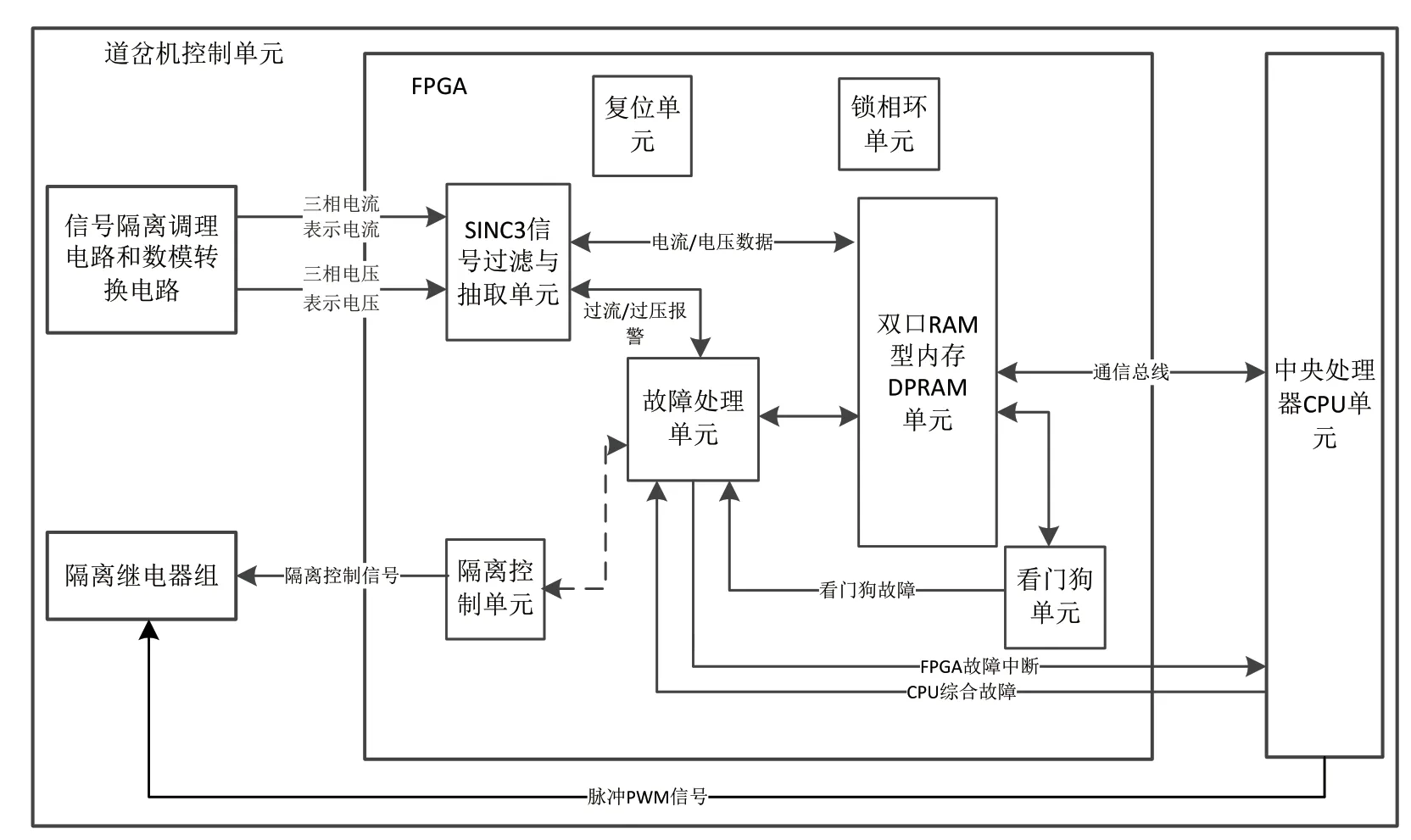

道岔信号采集和故障监测单元以FPGA 为核心处理器,如图1 所示。主要包括以下4 个部分:1) 三相相电压、三相电流以及表示电压和表示电流等外部模拟信号的隔离和信号调理单元。2) 基于Σ-Δ AD 的转换单元。3) 基于FPGA 的SINC3 数字滤波器和信号抽取单元。4) 基于FPGA 的故障监测单元。其中第一部分、第二部分和第三部分组成信号采集单元,第四部分构成故障监测单元。来自道岔机外部的电压电流信号经过第一部分后完成信号隔离和比例调整,并将其送给第二部分进行模数转换,再经过第三部分完成数字抽取和信号采样。采样完成后一部分信号送给第四部分进行故障监测,另一部分信号送给上位机进行处理。

图1 道岔信号采集和故障监测单元架构框图

2 道岔信号采集单元

道岔信号采集单元需要对轨旁道岔机的3 路三相电流信号、3 路三相相电压、1 路表示电压和1 路表示电流进行采集,精度需要达到1%。轨旁道岔机属于室外设备,采样信号在送给控制电路处理前,须考虑防止来自电源和负载道岔接口引入对控制侧电路的噪声干扰。该文设计的采集单元首先经过隔离和信号调理电路对采集信号进行预处理,并将预处理后的信号送给Σ-ΔAD,再基于FPGA 编码对SINC3 数字滤波器进行数字滤波和信号抽取。Σ-Δ 调制技术是基于过采样、噪声整形和数字抽取滤波的技术。与其他类型的AD 转换器相比,Σ-ΔAD 基于过采样和求均值技术,在不增加成本的基础上,可降低噪声影响,改善信噪比,从而有效提高分辨率;而其数字抽取滤波器位于Σ-ΔAD 后级,在转换过程中噪声抑制和响应时间是可控的。这些特性使该采集方案非常适合在道岔机控制系统这种环境比较复杂的工况中使用,具体情况如下。

2.1 信号隔离和信号调理电路的设计

该文采用TI新推出的一种新型芯片AMC3301进行信号隔离,再搭配运放搭建信号调理电路。AMC3301 是一款采用电容隔离原理的芯片,隔离电压等级可达4 250 V/min另外,这颗芯片内置隔离DCDC,不需要配置独立的隔离电源,因此基于AMC3301 的隔离电路比传统的隔离芯片加隔离电源或者互感器隔离方案的面积要小很多。

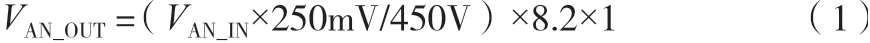

三相相电压与表示电压的隔离调理电路相同,以A 相相电压隔离调理电路为例,如图2 所示,A 相电压信号先经过前级电阻分压,增益记为。再经过AMC3301 芯片进行信号隔离,增益记为,即为AMC3301 内部增益(8.2)。然后由TLV9064IPWR 构成的信号缩放电路进行信号比例调整,缩放比例记为。三相输入相电压的额定有效值为AC 220 V,峰值为AC 311 V。设计的电压隔离调理电路最大可采集的输入峰值电压值为AC 450 V,由于所选的AMC3301 输入范围为±250 mV,内部放大系数为8.2,因此可将配置为250 mV/450 V, 而为8.2,的值可以根据后级电路设置为1。电压采集隔离电路的输入/输出关系如公式(1)所示。

式中:为来自道岔外部输入A 相相电压峰值;为经过信号隔离芯片和调理电路转换后的输出电压值。

三相电流和表示电流的隔离调理电路相同,以A 相电流隔离调理电路为例,将图2 中的电阻分压部分改为小电阻取样电流信号,后续电路一致(如图3 所示)。A相电流信号先经过前级小电阻取样,增益记为。再经过AMC3301 芯片后,增益记为。然后经过由TLV9064IPWR 构成的信号缩放电路进行信号比例调整,缩放比例记为。三相输入电流的额定有效值为2 A,峰值为±2.83 A,启动电流最大值不超过±12 A。该文设计的电流隔离调理电路最大可采集的输入电流峰值为±25 A,由于所选的AMC3301 输入范围为±250 mV,内部放大系数为8.2,因此可将配置为250 mV/25 A,而即为8.2,的值可以根据后级电路设置为1。电流采集电路的输入/输出关系如公式(2)所示。

图3 A 相输入电流隔离调理电路框图

式中:为来自道岔外部输入A 相电流值峰值;为经过信号隔离芯片和调理电路转换后的输出电压值。

3 路三相相电压、3 路三相电流信号、1 路表示电压和1 路表示电流这些信号都在经过上述信号隔离和调理电路后送给ADS1204 芯片进行模数信号转换。

2.2 AD 转换单元的设计

外部信号经过上述隔离调理电路后送给AD 转换单元进行处理。 该文AD 转换单元采用来自TI 的Σ-ΔAD 芯片ADS1204,这是一款4 通道二阶Σ-Δ 调制器,能将模拟输入信号转换为高速的单比特数据流。采用适当调制速率和数字抽取滤波器,该器件可在无丢码的情况下实现16 位模数转换。

该文设计的道岔信号采集电路总共采集8 路信号,采用了2 个4 通道ADS1204 芯片,采用单端接法,参考电压使用内置的2.5 V 电源,采样时钟使用外部有源晶振,可以将模拟转换后产生的数据流信号送给FPGA 处理。

2.3 基于FPGA 的SINC3滤波和信号抽取单元的设计

经过ADS1204 后将模拟输入信号转换为高速的单比特数据流,需要通过适当的数字滤波器重构原始信息。在FPGA 内部使用芯片手册上推荐的SINC3 滤波器实现数字信号抽取。SINC3 滤波器是在高速采样频率下执行下级级联的阶累加运算,将输入的单比特数据流转换成多比特数据。其中,SINC3 滤波器的三阶累加运算,如图 4(a) 所示。然后在低抽取频率f下执行级联的阶微分运算,获取位流的均值为1 的密度,以完成滤波功能,其中,SINC3 的三阶微分运算如图4(b)所示。

图4 SIN3 数字滤波器原理框图

SINC 数字滤波器的阶数的选择与滤波器前端Σ-ΔAD 调制器的阶数有关 ,的取值至少要比Σ-ΔAD 调制器的阶数大1,以防止边带外过度失真的噪声调制进入基带。

SINC 数字滤波器输出数据的位数是输入数据位数的倍 ,由于输入数据是单比特的数据流,即也是输出数据的位数。因此的大小由SINC 数字滤波器的阶数和抽取率决定 ,三者之间满足公式(3)。

SINC 数字滤波器输出数据的频率f(即数据抽取频率)与采样频率满足公式(4)。

SINC 数字滤波器在抽取率不同时,会产生不同的直流增益,与阶数和抽取率满足公式(5)。

SINC 数字滤波器的响应时间是滤波器阶数和抽取频率的函数,如公式(6)所示。

由于所选择的ADS1204 是一款二阶Σ-Δ 调制器,因此选择=3 的SINC3 的滤波器即可。当采用=10.24 MHz(该时钟为系统时钟的2 分频,为了方便计算将采样时钟设为10.24 MHz) 时,根据公式(3)~公式(6)可得SINC3数字滤波器各参数间的关系,见表1。

由表1 可知,抽取率越高、直流增益越大,意味采样点越多,输出数据的位数越长,采样精度也越高,但会导致滤波器响应时间过长和输出数据的频率过低。

表1 SINC3 数字滤波器的各参数关系(fs=10.24 MHz)

如图1 所示,ADS1204 转换抽取的电流电压信号须供后级的CPU 使用,综合考虑电流、电压值的精度会影响后级CPU 控制算法的精度,这一部分需要采集的信号须具有高精度的特点;而将采集到的信号与内部阈值进行比较产生过流/过压保护信号的过程须具有响应时间短的特点,使系统及时响应,以发挥很好的保护作用。基于此,该文采用双模块抽取电压电流信号,即将经过FPGA 内部采用额定抽取率为256 的滤波器的信号存到DPRAM 里面供后级CPU 读取,而将经过采用抽取率为16 的滤波器的信号与内部阈值进行比较产生的过流/过压信号送到故障监测模块进行处理。并且可以根据不同的系统软件配置相应的抽取率,十分灵活。

与其他一般AD 转换加上CPU 读取值的方案对比,一般的AD 转换速度都是一定的,再加上CPU 任务繁重,一般只会在一个大周期250 ms 内读取1 次AD 转换的值,且读取的点数也有限制,不能达到较高的精度。与CPU 不同的是FPGA 具有并行处理的特点,采用抽取率为256 的滤波器响应时间只有75 μs,道岔机的三相电流和三相电压周期为20 ms,20 ms 内最多可采集265 个点,该文设计的采集模块20 ms 内采集64 个点,并且在CPU 访问FPGA 的间隔时间内采样连续10 个周期数据存在DPRAM 中供CPU一次读取处理,大大减轻了CPU 负荷,提高了CPU 计算电流电压有效值的精度。

同时,一般的AD 转换加上CPU 读取值的方案不能实时去监控非正常的过压过流信号,而现在利用FPGA 灵活可编程的特性,在内部增加过流/过压比较单元,并将过流/过压状态送给故障监测模块实时监测,可在道岔发生堵转、短路或其他异常情况下中断CPU,使CPU 可以快速给出反应,避免故障影响进一步扩大。

3 基于FPGA 的故障监测单元的设计

道岔属于室外设备,当发生自然灾害时,设备老化或操作不当就可能发生故障,一般故障类型包括混线、短路、断线或堵转等。反应到道岔控制系统里为所采集的信号发生过压、过流、欠压、欠流、电压曲线畸变或电流曲线畸变等现象。

该文设计的道岔故障监测单元以FPGA 为中央处理单元、CPU 为辅助处理单元。FPGA 将与道岔相关的信号都进行了模拟量的采集存储,并发送给上层CPU,使上层控制平台具有实时监测所有道岔相关信息的功能。

FPGA 内将故障级别分为I 级和II 级,如图1 所示。I 级故障包括CPU 下发的硬接线故障-CPU 综合故障和内置的看门狗模块产生的喂狗不及时故障–看门狗故障。其中,看门狗故障是FPGA 对CPU 的监控,当CPU 发生故障时,FPGA 及时作出反应,发挥硬件冗余作用,提高系统安全性。将过流/过压信号统一定义为II 级故障。过流/过压故障信号为FPGA 内部由SINC3 滤波器抽取出来的道岔3 路三相电压、3 路三相电流、1 路表示电压和1 路表示电流信号与FPGA 内置对应阈值的比较,连续读取配置的次数都超过阈值后产生对应的过压/过流故障,共有4 路过压信号和4 路过流信号。当发生任意一种故障时,FPGA都会给CPU 发送中断,CPU 可以读取存在FPGA 内的对应的故障号,并进行后续处理。

当产生I 级故障时,FPGA 产生故障中断信号给CPU,CPU 读取故障并进行相应处理。同时,FPGA 产生封锁隔离继电器驱动的命令,及时让隔离继电器失电落下,断开输入380 V AC 电源和道岔之间的通路,使道岔系统导向安全侧。当产生II 级故障时,FPGA 仅产生故障中断信号给CPU,CPU 读取故障并根据其他信息进行相应处理。在故障排除后,可由CPU 发送动态复位信号,当复位信号有效时复位故障监测单元,解除保护状态,比传统的单一命令解除保护状态更加安全。

利用I 级故障及时断开隔离继电器的反应时间为微秒级,保证在系统发生严重故障时可以及时作出故障导向安全的反应;而将过流/过压信号定义为II 级故障,使FPGA可以实时给CPU 报警,给 CPU 及时作出相应的处理提供可能,又给CPU 留有内部识别判断宽恕时间,不会在小噪声的影响下切断系统影响运行。与传统的故障处理方法相比,该文所述的方案在提高安全性的同时,又保证了可靠性。

4 试验分析

以上文的道岔信号采集和故障监测原理为基础,开发了道岔控制单元硬件电路,在实验室搭建了以道岔控制单元硬件电路板为主控单元控制S700K-C 转辙机的测试平台。在测试平台制造道岔转辙机过流等故障,控制平台可及时响应,导向安全侧,符合系统设定预期,说明FPGA数据处理准确,对故障响应快速,系统运行安全、稳定。

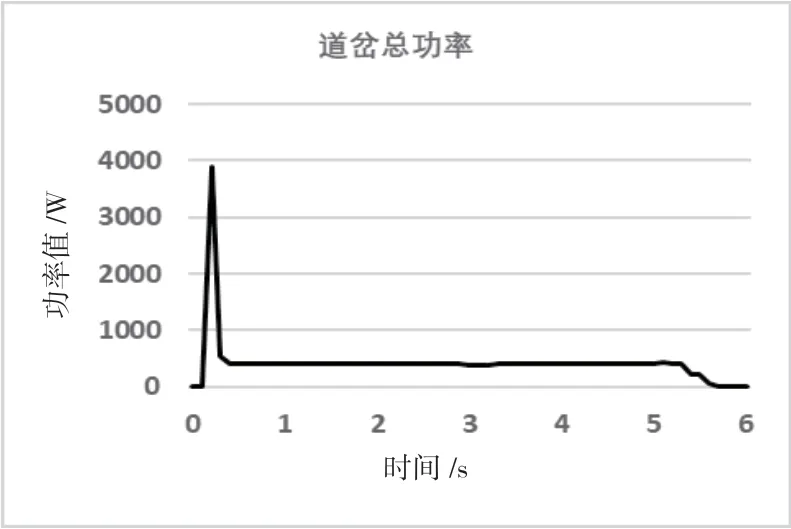

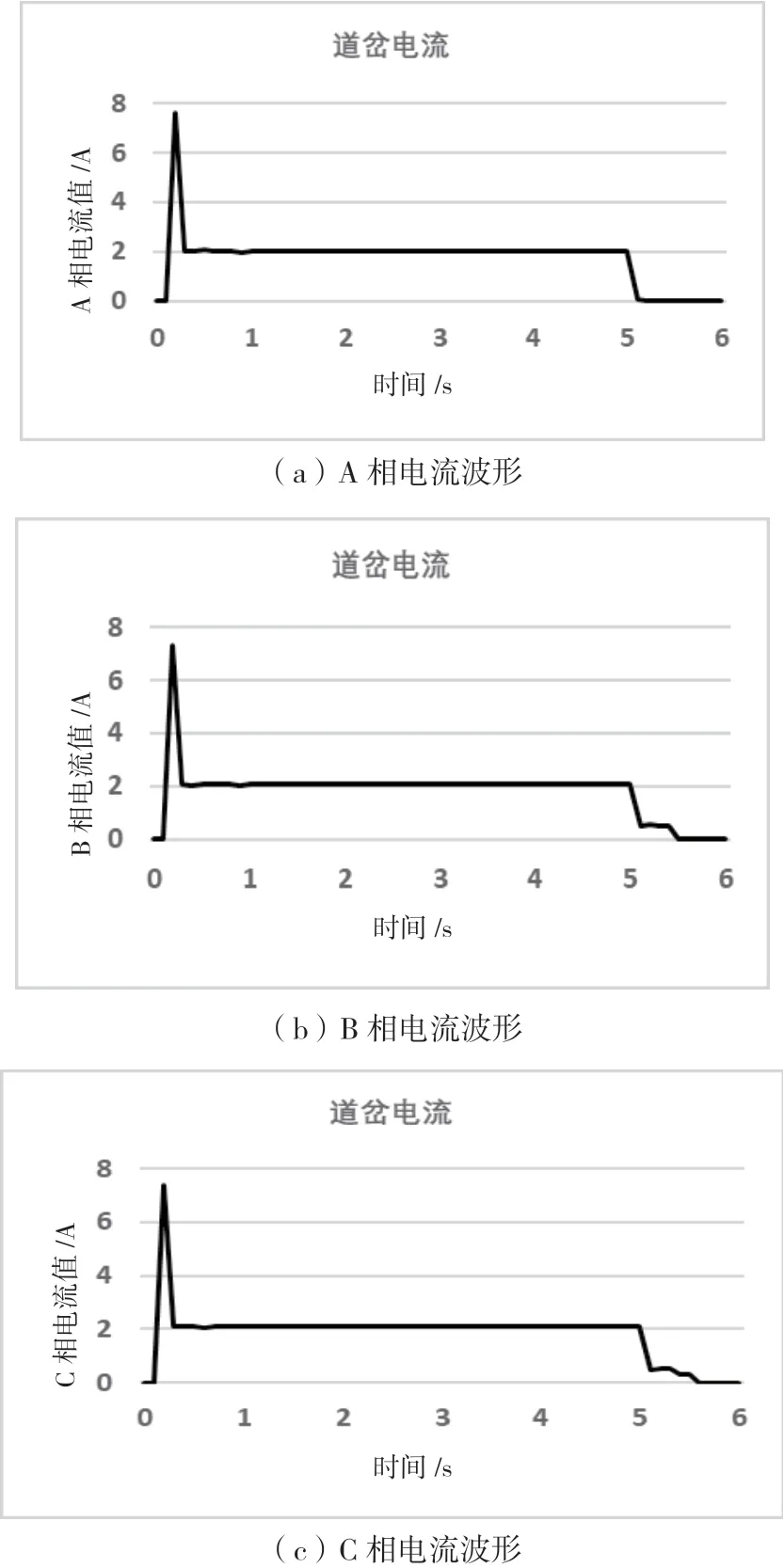

启动转辙机,测试板卡采样信号精度指标符合预期1%的需求。在空载时,正驱转辙机到定位,上位机监测到的道岔功率,如图5 所示。输出的三相相电流波形如图6 所示(图6(a)、图6(b)以及图6(c)分别对应A、B 以及C 三相电流)。上位机打印出来的波形数据是利用FPGA 采集到的三相电压和三相电流信号计算得出的。

图5 S700K-C 转辙机空载时输出总功率波形

图6 S700K-C 转辙机空载时正驱电流波形

5 结论

该文提出的集成道岔信号采样和故障监测功能的硬件控制单元在搭建的道岔控制实验室平台上,测试运行正常,电流电压采集精度符合预期,并开展了多次故障模拟测试,故障监测单元响应实时,实现了快速且有效保护的目标。另外,该文所述的故障监测功能是集成在具有道岔执行功能的硬件电路板上的,与传统的分别用2 套硬件电路板实现执行功能和监测功能的方案相比,其具有更小型化的特点,并且还可以节约成本。